2. Экстракция списка сетей с паразитными элементами.

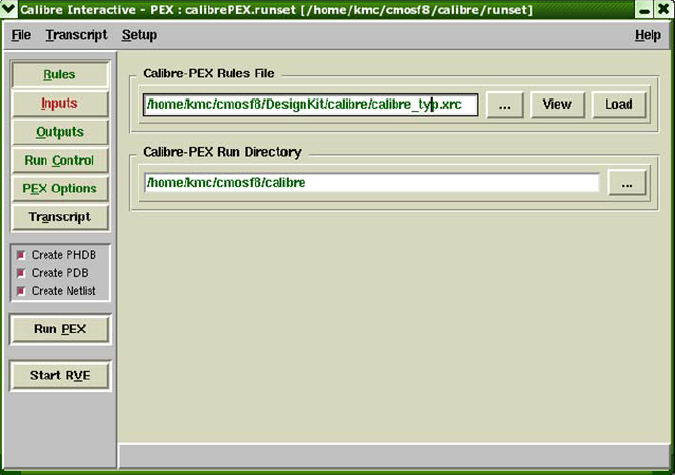

Запуск главного окна экстрактора осуществляется из меню окна топологического редактора Calibre → Run PEX. В появившемся окне в разделе Rules требуется указать путь к правилам экстракции и к рабочему каталогу (см. рисунок 6).

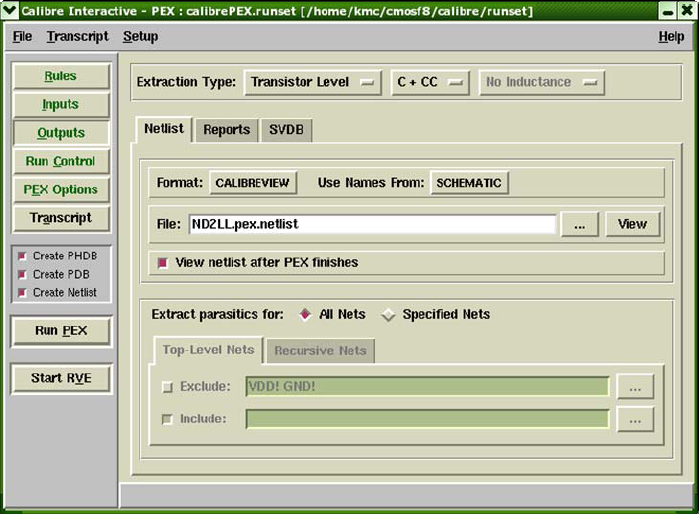

Дополнительно требуется задать параметры выходного файла и тип экстракции (см. рис. 7).

Рис. 6. Окно для указания правил и рабочей папки экстракции

Рис. 7. Окно задания параметров экстракции

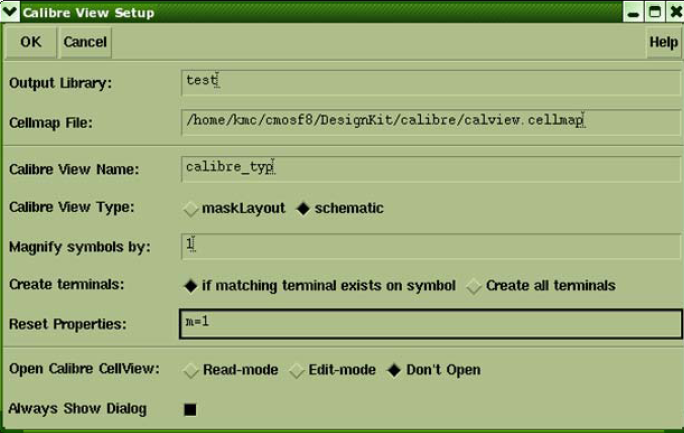

После завершения процесса экстракции появится окно Calibre View Setup, в котором необходимо задать путь к файлу трансляции cellmap.calview, имя вида ячейки, тип ячейки (см. рис.8).

Рис. 8. Окно Calibre View Setup

После нажатия на клавишу «Ok» появиться новое представление ячейки сalibre, представляющее собой электрическую схему с паразитными элементами.

3. ЛАБОРАТОРНЫЕ ЗАДАНИЯ И МЕТОДИЧЕСКИЕ УКАЗАНИЯ ПО ИХ ВЫПОЛНЕНИЮ

Методические указания по выполнению задания

1. Произвести проверку правил проектирования топологии в блоке согласно заданию предыдущих лабораторных работ в программе Calibre.

2. Произвести верификацию топологии проекта и электрической схемы (согласно варианту задания) в пакете Calibre.

3. Провести экстракцию списка сетей с паразитными элементами.

4. КОНТРОЛЬНЫЕ ВОПРОСЫ К ЛАБОРАТОРНЫМ ЗАДАНИЯМ

1. Для каких целей используется пакет Calibre?

2. В чем заключается различие программ Diva и Calibre?

3. Опишите процесс верификации топологии и электрической схемы в приложении Calibre LVS.

4. Для чего нужен модуль Calibre RVE?

5. Перечислите основные настройки в окне Calibre View Setup?

5. Требования к содержанию отчета

Отчет по лабораторной работе должен содержать следующие разделы:

1. Цели и задачи лабораторной работы.

2. Топология устройства.

3. Краткое описание и результаты выполненной работы:

4. Отчет DRC проверки

5. Отчет об LVS проверки.

6. Отчет извлечение списка сетей с паразитными элементами.

7. Выводы о проделанной работе.

Лабораторная работа № 3

«Физическая верификация и характеризация топологии аналоговых устройств в программе Assura»

1. общие сведения

Цели работы

Ознакомление с программой физической верификации Assura, получение навыков настройки и работы со средой верификации, овладение полным циклом физической верификации в программе Assura.

Краткие теоретические сведения

Assura – это программный инструмент, предназначенный для проведения полного цикла физической верификации, как отдельных блоков, так и ИС любого размера, независимо от типа технологии, и извлечения из топологии списка соединений с паразитными элементами.

2. Домашние задания и методические указания по их выполнению

Методические указания по выполнению задания

1. Проверка норм проектирования и исправление ошибок

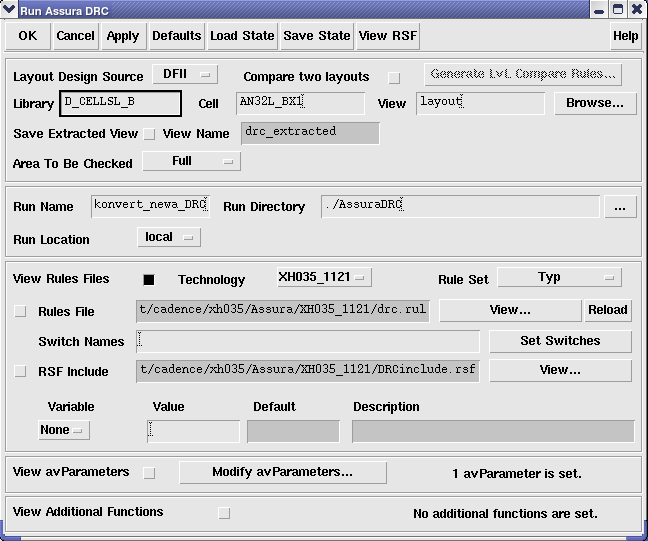

Для запуска приложения Assura DRC, предназначенного для проверки проектных норм, необходимо вызвать процесс «Assura/Run DRC» в меню редактора топологии Virtuoso. В результате выполнения команды на экран выводится интерфейс, показанный на рис. 1.

Рис. 1. Интерфейс программы Assura DRC

Перед запуском процесса проверки не обходимо указать место расположения проверяемого файла:

- Library – директория;

- Cell – название ячейки проекта;

- View – представление (обычно Layout);

- Run Name – имя процесса. Здесь необходимо ввести имя текущего процесса;

- Run Directory – рабочая директория, где будет сохраняться текущий выполняемый процесс (по умолчанию Assura DRC);

- технологический процесс (Technology).

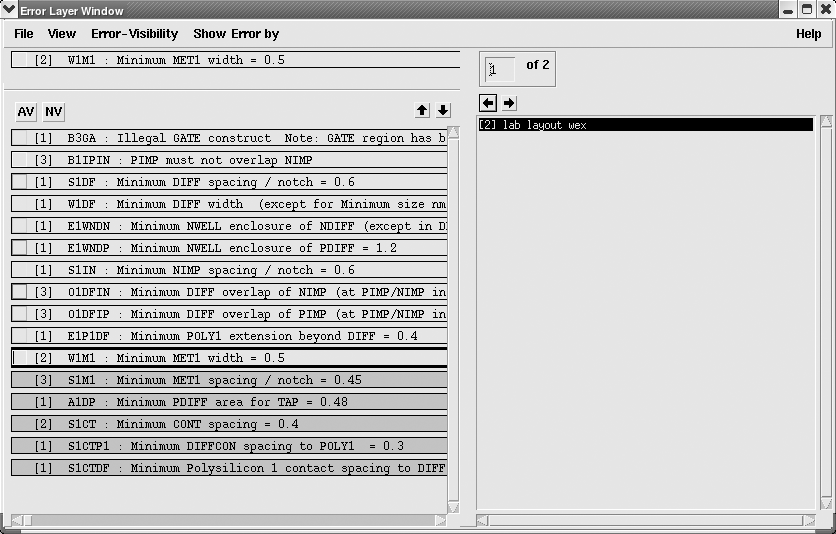

После выполнения проверки норм КТТ Assura выведет результаты проверки в окне Error Layer Window, показанном на рис. 1.

Рис. 2. Окно поиска исправления ошибок Error Layer Window

В ELW внизу слева перечислены правила проектирования в виде списка, которые были нарушены (обнаруженные ошибки). В каждой строке сначала указывается цвет, которым будет подсвечена ошибка данного правила, затем в квадратных скобках указано число подобных ошибок и название правила, которое описано в файле drc.rul. Обычно, в названии правила также указывается необходимая величина (в мкм.) расстояния между слоями, зазора внутри слоя или перекрытия слоев. Вверху слева указывается текущее правило проектирования и его название. Справа в поле для текущего правила указывается топологическая ячейка, в которой эта ошибка найдена. С помощью стрелок вправо / влево осуществляется переход к следующей/предыдущей ошибке, которая будет подсвечена в топологии в виде цветного полигона.

Дополнительные возможности:

- с помощью кнопок «AV» (показать все) и «NV» (скрыть все) можно показать/скрыть все подсвеченные ошибки;

- правой кнопкой мыши можно изменять цвет подсветки ошибок;

- если для какого-то правила проектирования много ошибок, то их можно выбирать, вводя число в правой верхней части окна в поле «numbers». Здесь же указывается текущий номер ошибки для конкретного правила.

Верификация электрической схемы и топологии

Для того чтобы осуществить верификацию топологии и электрической схемы в программе Assura, необходимо вызвать процесс «Assura/Run LVS» в меню редактора топологии Virtuoso. В результате выполнения команды на экран выводится интерфейс, показанный на рис. 3.

Рабочая область Assura включает:

- название схемотехнической ячейки и библиотека ячейки

- название топологической ячейки и библиотека ячейки

- файл извлечения списка электрических связей (extract.rul);

- файл сравнения списков электрических связей топологии и схемы (compare.rul).

Сразу после запуска процесса верификации программа-экстрактор начинает извлечение электрической схемы из топологии. Экстрактирование происходит согласно правилам, определенным в файле extract.rul.

Рис. 3. Интерфейс Assura LVS

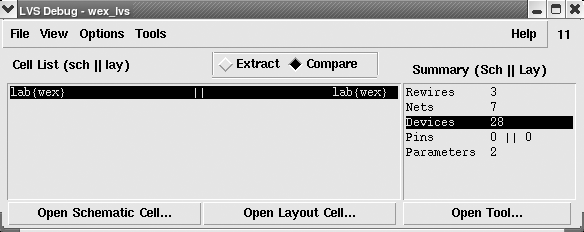

После извлечения электрической схемы из топологии автоматически запускается процесс верификации. После окончания верификации на экран будет выведен файл отчета. В случае нахождения ошибок Assura LVS сразу после закрытия окна отчета выводит на экран графический интерфейс отладки LVS Debug, показанный на рис. 4.

Рис. 4. Интерфейс отладки LVS Debug

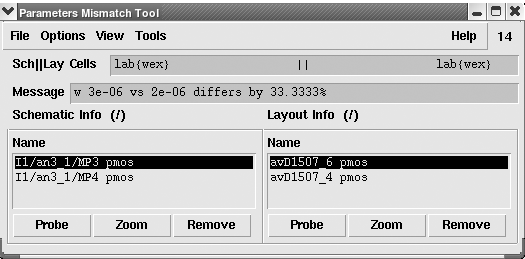

В правой части окна указаны все ошибочные приборы, сети и терминалы. Для того чтобы посмотреть ошибки необходимо выбрать тип ошибок, которые будут выведены «Rewires», «Nets», «Devices», «Pins», «Parameters» и нажать на клавишу «Open Tool». После выполнения этих действий на экран выводится окно ошибок выбранного типа. Пример такого окна, Parameters Mismatch Tool (параметрические ошибки), представлен на рис. 5.

В верхней строке окна указаны названия ячеек (директорий) схемы и топологии. Строка ниже содержит информацию о расхождении параметров. Нижняя половина окна разбита на две части: информация о приборах топологии и информация о приборах схемы.

Рис. 5. Окно ошибок Parameters Mismatch Tool

При нахождении соответствия между приборами в топологии и схеме, но не соответствия их размеров Assura LVS указывает эти приборы и их тип в частях информации схемы и топологии. При выделении, например, прибора схемы выделяется соответствующий ему прибор топологии. Ошибочный прибор можно найти независимо в каждом из видов представления (схема и топология). При нажатии на клавишу «Probe» в выбранном представлении выделяется ошибочный прибор. Нажатие на клавишу «Zoom» увеличивает выделенное место до размера окна, а нажатие на клавишу «Remove» отменяет выделение прибора.