Учебное пособие 1484

.pdf

61

ройства. В каждый сменный блок вводится дополнительная аппаратура для передачи состояния входов блока на его выход.

Все сменные блоки одного уровня (ранга) проверяются одновременно и управляются одним управляющим сигналом.

Диагностирование заключается в настройке схем управления на проверку сменного блока i-го уровня, подаче тестовых воздействий на его вход, опросе результатов и сравнении их с эталонными.

Вариант 2. Селекторы устанавливаются только в сменных блоках, соединенных с первичными входами диагностируемого устройства, и на обратных связях, обеспечивая их разрыв в режиме диагностирования.

Выходы каждого сменного блока соединены со средствами тестового диагностирования. Средства тестового диагностирования имеют информационные выходы, соединенные с дополнительными входами всех селекторов и служащие для выдачи тестовых воздействий на блоки устройства. Кроме того, СТД имеют один управляющий вход, соединенный с управляющими входами дополнительных селекторов устройства.

На входы СТД, которые соединены с выходами сменных блоков диагностируемого устройства, поступают ответы последних на тестовые воздействия. В СТД выполняется анализ этих ответов, в результате которого выдается диагноз.

При определении последовательности диагностирования сменные блоки устройства ранжируются, т. е. располагаются по уровням по отношению к первичным входам устройства. Диагностирование сменных блоков выполняется последовательно в порядке возрастания номеров рангов. Тесты для сменных блоков j-го ранга (j 2), построенные первоначально в терминах этих блоков, пересчитываются затем в терминах тех входов блоков (j - s)-x рангов (s 1), к которым подключены селекторы. Это - внешние входы устройства, а также входы, принадлежащие местам обрыва обратных связей.

4.8. Метод диагностирования с помощью схем встроенного контроля

Этот метод характеризуется тем, что объектом элементарной проверки является сменный блок, а средствами функционального диагностирования - схемы встроенного контроля (СВК), конструктивно совмещенные с каждым сменным блоком /9/.

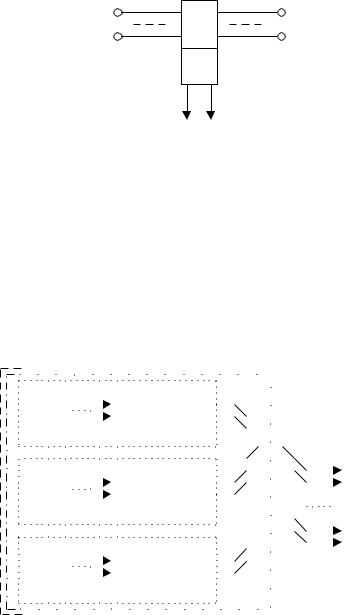

На рис.4.14 показаны диагностируемое устройство (ДУ) и схемы встроенного контроля, образующие самопроверяемый сменный блок. Наибольшая вероятность правильного диагностирования достигается при полной проверяемости ДУ и самопроверяемости СВК.

62 |

|

|

Р |

x1 |

z |

|

ДУ |

xn |

zk |

|

СВК |

f1 |

f2 |

Рис. 4.14. Самопроверяемый сменный блок

ДУ называется полностью проверяемым, если любая его неисправность заданного класса обнаруживается СВК в момент ее первого появления на выходных устройствах. Требование полной проверяемости ДУ и самопроверяемости СВК приводит к значительным аппаратурным затратам, что ограничивает применяемость данного метода устройствами, реализованными в основном на больших интегральных схемах.

На рис.4.15 приведена структура функционального диагностирования. Локальными средствами функционального диагностирования ЛСФДi являют

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

f |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

Р1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

СВК1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

|

|

|

ЛСФД1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

f |

2 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

f |

i |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

f |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

Рi |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

СВКi |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

f |

2 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

f |

i |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

УАИ |

|

||||||||||||||||||

|

|

|

|

ЛСФДi |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

n |

|

|

|

||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

f1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

f1n |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

f |

2 |

n |

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||

|

|

|

|

Рn |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

СВКn |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

f |

|

|

n |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||

|

|

|

|

ЛСФДn |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ОД |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ОСФД |

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 4.15. Структура системы диагностирования, использующая схемы встроенного контроля

ся самопроверяемые СВКi с парами выходов fi1, fi2, приданные каждому сменному блоку Бi с общим средством функционального диагностирования ОСФД, и устройство анализа и индикации УАИ. Назначение последнего - синхронизация сигналов ошибок и однозначная индикация неисправного блока.

Достоинством метода диагностирования с помощью схем встроенного контроля является практически мгновенное диагностирование сбоев и отказов, сокращение затрат на локализацию перемещающихся отказов и разработку диагностических тестов.

4.9. Диагностирование с помощью самопроверяемого

дублирования

63

Этот метод аналогичен предыдущему , так как он тоже основан на принципе самопроверяемости сменных блоков. Разница состоит в том, что самопроверяемость сменных блоков достигается введением дублирующей аппаратуры и самопроверяемых схем сжатия, обеспечивающих получение сводного сигнала ошибки, свидетельствующего о неисправности сменного блока. На рис.4.16 приведена структурная схема самопроверяемого блока. Этот способ обеспечения самопроверяемости приводит к большим дополнительным затратам аппаратуры, что оправдывает его применение лишь в больших интегральных микросхемах /9/.

X1  X2

X2  Xn

Xn

ДУ

ДУ'

|

|

Z1 |

|

|

Z2 |

|

|

Zk |

Z1 |

Сж1 |

|

|

|

|

Z2 |

|

|

Zk |

Сжk-1 |

f1 |

|

f2 |

|

|

|

Сж1,...,Сжk-1 - схема сжатия

Рис. 4.16. Структурная схема самопроверяемого блока

При реализации ЭВМ на больших и сверхбольших интегральных микросхемах последние часто используются не полностью, так как ограничивающим фактором является не число транзисторов БИС, а число выводов. Поэтому введение в БИС дублирующих схем, обеспечивающих ее самопро веряемость, позволяет более полно использовать возможность БИС без значительного увеличения объема аппаратуры.

4.10. Метод диагностирования по регистрации

состояния

Усложнение структуры ЭВМ, повышение степени интеграции и быстродействия элементов приводят к увеличению относительной доли сбоев в общем числе ошибок ЭВМ. В связи с этим очень важно уметь локализовать причину сбоев по ситуации, зафиксированной в момент их появления. Такую возможность предоставляет метод диагностирования по регистрации состоя-

ния /9/.

Этот метод диагностирования характеризуется тем, что неисправность или сбой локализуются по состоянию ЭВМ, зарегистрированному в момент

64

проявления ошибки и содержащему информацию о состоянии схем контроля, регистров ЭВМ, адресов микрокоманд, предшествующих моменту ошибки, и другую информацию. Место возникновения ошибки определяется по зарегистрированному состоянию путем прослеживания трассы ошибки от места ее проявления до места ее возникновения. Диагноз выполняется с помощью программных средств диагностирования самой ЭВМ, если диагностируется место возникновения сбоя, либо другой ЭВМ, если диагностируется отказ.

В ЭВМ, имеющих сервисные процессоры, диагноз может выполняться с помощью микропрограмм сервисного процессора.

Системы, использующие этот метод диагностирования, называются также системами прогнозирования отказов, так как отказам интегральных микросхем, как правило, предшествует их работа с ухудшенными характеристиками. Подобное (промежуточное между исправным и неисправным) состояние интегральной микросхемы выражается в увеличении числа сбоев. И лишь через определенное время ухудшение характеристик переходит в отказ. Локализация таких систем позволяет предотвратить их отказ путем замены ТЭЗ во время профилактических регламентных работ. Для диагностирования по регистрации состояния необходимо, чтобы система контроля ЭВМ обеспечивала:

1)непрерывность контроля;

2)блокировку распространения ошибок;

3)размещение точек контроля в узловых точках структуры;

4)регистрацию состояния ЭВМ в специальном буфере регистрации в момент появления ошибки;

5)сохранение предыстории микропрограммы в виде адресов и содержимого микрокоманд, выполненных после обнаружения ошибки и до момента регистрации;

6)однозначное соответствие между микрокомандой, на которой была обнаружена ошибка, и тактом останова ЭВМ для регистрации;

7)восстановление ЭВМ после сбоя путем повторения команд.

При выполнении этих требований ошибка, обнаруженная схемами контроля, оставляет след, начинающийся в месте возникновения ошибки и заканчивающийся в месте ее обнаружения. Этот след проявляется в виде несоответствия контрольных и информационных бит и единичного состояния триггеров ошибок.

Анализ состояния ЭВМ, зарегистрированного при обнаружении ошибки, позволяет выявить схемы, которые могут быть причиной ошибки. В том случае, когда ошибка могла распространиться разными путями, к анализу привлекается и код микрооперации, выполнявшейся в момент обнаружения ошибки. Это позволяет определить путь ее распространения и место возникновения. Поскольку одна и та же часть аппаратуры (в зависимости от выполнявшейся микропрограммы) может приводить к различным состояниям ЭВМ и, следовательно, к различному подмножеству подозреваемых средств, локализация ошибки может быть уточнена путем выполнения логических опера-

65

ций над подмножествами, содержащими названия аппаратурных средств (групп ТЭЗ).

Контрольные вопросы

1.Что включает в себя система автоматического диагностирования?

2.Объясните особенности тестового и функционального диагностиро-

вания.

3.В чем заключаются принципы раскрутки и функции средств тестового диагностирования?

4.Каково назначение сервисных процессоров?

5.Назовите методы функционального диагностирования и показатели качества систем диагностирования.

6.В чем заключается метод командного ядра?

7.Укажите особенности, достоинства и недостатки методов диагностирования с помощью схем встроенного контроля и самопроверяемого дублирования.

8.В чем заключается система прогнозирования отказов?

66

5.УРОВНИ ТЕСТИРОВАНИЯ СВТ

5.1.Этапы производства и контроля СВТ

Надежность СВТ во время эксплуатации закладывается на этапах ее разработки и изготовления. Выявление при изготовлении дефектов комплектующих изделий и производства, а также дефектов из-за ошибок разработки существенно способствует повышению надежности работы ЭВМ. В противном случае дефекты будут обнаруживаться во время эксплуатации. В данном случае понятия «дефект» и «неисправность» используются для обозначения одного и того же явления с тем лишь смысловым оттенком, что под дефектом понимается «врожденная» неисправность, оставшаяся в устройстве после его выпуска.

Для обнаружения дефектов и неисправностей СВТ подвергаются испытаниям - тестированию. Тестирование составляет основу диагностирования и профилактических испытаний /7,8,17/.

На рис.5.1 представлены основные этапы изготовления и ввода в эксплуатацию ЭВМ и соответствующие тесты.

Во время эксплуатации ЭВМ используются те же тесты, но обычно в обратной последовательности.

Испытания цифровых устройств могут быть статическими и динамическими. Статическими называются испытания, при которых частота тестового воздействия на проверяемое устройство намного меньше частоты реального воздействия при работе устройства в составе ЭВМ. Динамические - испытания, при которых частота тестовых воздействий соответствует рабочей частоте устройства.

Испытания делятся также на функциональные и параметрические. Функциональными называются испытания, проверяющие соответствие устройства заданному алгоритму его функционирования. При параметрических испытаниях контролируются ток, напряжение, форма импульсов, задержка распространения сигналов, длительность фронта и спада.

Объектами тестирования могут быть:

1)произвольные логические схемы, содержащиеся в ИС, СИС, БИС, СБИС, ТЭЗ;

2)устройства ЭВМ, такие как центральный процессор, каналы памяти;

3)архитектурные свойства ЭВМ;

4)совокупное функционирование всех устройств, т. е. системные свойства ЭВМ (рис.5.2).

Соответственно будем различать четыре уровня тестирования:

произвольных логических схем; устройств ЭВМ; архитектурных свойств ЭВМ; системных свойств ЭВМ.

67

|

Входной контроль |

Изготовление |

|

|

ИС(СИС,БИС) |

печатных плат |

|

Сборка ответных |

Сборка ТЭЗ |

Контроль печатных |

|

панелей |

плат |

||

|

|||

Проверка ответных |

Тестирование ТЭЗ |

Тесты ТЭЗ |

|

панелей |

|

|

|

|

Сборка центральной |

|

|

|

части ЭВМ |

|

|

|

Тестирование устройств |

Функциональные |

|

|

центральной части ЭВМ |

тесты |

|

|

Сборка системы |

Тест архитектурных |

|

|

|

||

|

|

свойств |

|

|

Тестирование системы |

|

|

|

Установка системы у |

Тесты ПУ,системный |

|

|

тест,контрольные |

||

|

пользователя |

||

|

задачи |

||

|

|

||

|

Тестирование системы |

|

|

|

на месте установки |

|

Рис. 5.1. Этапы изготовления и тестирования средств вычислительной техники

Тестирование системы |

Контрольные задачи, |

|

системный тест, тесты ПУ |

||

|

||

Тестирование |

Тест архитектурных |

|

архитектурных свойств |

свойств |

|

Тестирование |

Функциональные тесты |

|

устройств |

||

|

||

Тестирование |

Тесты ТЭЗ |

|

логических схем |

||

|

Рис. 5.2. Эксплуатационные тесты

При вычислении тестов каждого уровня используется описание (модель) устройств - объектов тестирования. Будем рассматривать следующие уровни описания дискретных устройств:

*схемный;

*функциональный или микрооперационный, или регистровых пе-

редач;

*алгоритмический или архитектурный;

68

*системный.

Каждый уровень имеет свой язык описания, а полное описание системы представляет собой многоуровневую иерархическую структуру, содержащую языковые конструкции разных уровней.

Большинство неисправностей, возникающих при эксплуатации, представляют собой короткое замыкание линий на землю или на линию напряжения питания, короткие замыкания между сигнальными линиями, обрывы, отсутствие резисторов, пробои транзисторов, низкий коэффициент усиления или чрезмерные задержки, причем такие неисправности могут быть одиночными и кратными. Для вычисления тестов физические неисправности должны быть представлены их логическими моделями. Уровень описания определяет модель неисправностей и методы вычисления тестов.

5.2. Уровень логических вентилей

На уровне логических вентилей описание модели объекта тестирования задается перечислением логических функций элементов и связей между ними. Используются следующие модели неисправностей:

1)константные неисправности (статические). Моделируют постоян-

ный 0 (К0) или 1 (К1) на сигнальных проводниках схемы. В дальнейшем неисправности К0 и К1 на линии а будем обозначать соответственно а/0 и а/1. Константные неисправности называют также статическими, так как они обнаруживаются при статическом тестировании ;

2)короткие замыкания (КЗ). Моделируют короткие замыкания между сигнальными проводниками схем. Модель КЗ требует введения дополнительной схемы, как показано на рис.5.3.

Чаще всего системы генерации тестов используют именно эти модели неисправностей, поскольку с их помощью можно описать большинство реальных дефектов ИС. Полноту покрытия тестом коротких замыканий и константных неисправностей можно вычислить различными сводящимися друг к другу методами /2, 6, 14, 15, 17/.

Одним из недостатков описания схем на уровне логических вентилей являются сложность и громоздкость. Этот недостаток становится все более очевидным по мере роста степени интеграции. Машинное время, необходимое для вычисления тестов и моделирования неисправностей, связано с чис-

лом вентилей следующей зависимостью:

t = k·n3 ,

где t - машинное время ; k - коэффициент пропорциональности ; n - число вентилей.

Это затрудняет вычисление тестов для больших схем. Кроме того, полнота проверки тестов, полученных с помощью систем генерации тестов, есть убывающая функция от числа вентилей. Из графика этой функции на рис.5.4 видно, что для схем, содержащих свыше 1000 вентилей, полнота проверки схемы падает ниже приемлемого уровня.

69

|

|

|

|

|

|

|

|

|

КЗ |

a |

1 |

|

|

|

|

|

|

a |

1 |

b |

|

|

g |

|

|

|

|

b |

g |

c |

|

|

|

|

|

c |

|

1 |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

d |

1 |

|

|

|

|

d |

|

|

1 |

|

|

|

|

|

|

|

|||

e |

|

|

h |

|

|

|

|

e |

h |

f |

|

|

|

|

|

|

|

f |

|

|

|

|

а) |

|

|

|

|

|

б) |

|

|

|

Входы |

|

|

Выходы |

|

||

|

a |

b |

c |

d |

e |

f |

g |

h |

|

|

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

Исправная схема |

|

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

Неисправная схема |

в)

Рис.5.3. Модель короткого замыкания:

а - исходная схема; б - модель КЗ; в - таблица входных и выходных параметров

% |

|

Полнота 90 |

|

проверки 80 |

|

70 |

|

1000 |

2000 |

Число вентилей в схеме |

|

Рис. 5.4. Зависимость полноты проверки от числа вентилей

5.3. Функциональный уровень

Другим недостатком описания схем на уровне логических вентилей является то, что часто детали структуры БИС, например, микропроцессорных БИС, не доступны разработчикам тестов. Поэтому применяется более высокий уровень описания устройств, в котором в качестве элемента описания применяют не вентиль, а функциональный узел. Этот уровень описания, называемый функциональным (микрооперационным, или регистровых передач), использует графовую модель процессора (микропроцессора) и других устройств. Модель устройства представляет собой граф, вершины которого соответствуют регистрам, сумматорам, функциональным преобразователям, информационному входу и выходу, а ребра определяют пути передачи информации.

Описание схем на функциональном уровне сокращает затраты на вычисление тестов. К достоинствам описания функционального уровня относит-

70

ся также возможность использования одних и тех же тестов для различной схемной реализации одних и тех же функциональных устройств.

Модели неисправности функционального уровня описания определяют множество функциональных неисправностей, идентичных по своим свойствам множеству константных неисправностей вентильной модели. Моделями неисправностей на функциональном уровне являются:

1) для дешифратора выборки регистров: f(Ri /0) - регистр Ri не выбирается; f(Ri /Rj) - вместо регистра Ri выбирается Rj; f(Ri /Ri +Rj) - кроме R выбирается еще и Rj;

2)для дешифраторов микроопераций: f(mi /0) - микрооперация mi не активизируется; f(mi /mj) - вместо микрооперации mi активизируется mj; f(mi /mi +mj) - кроме микрооперации mi активизируется еще и mj;

3)для регистров и трактов передачи данных: неисправность типа К0 и К1 триггеров и линий передач данных различного количества сочетаний.

5.4. Алгоритмический уровень

Следующим более высоким уровнем описания является архитектурный или алгоритмический уровень. Подобное описание задается на языке высокого уровня (например - описание принципов функционирования систем IBM 360 на языке APL) граф-схемой алгоритмов (ГСА) или граф-схемой выполнения команд.

Моделями неисправностей этого уровня служат неисправности аппаратуры и ошибки разработки, приводящие к неверному результату выполнения команд.

5.5. Системный уровень описания

Системный уровень описания характеризует совокупное поведение всех устройств системы, их взаимодействие во времени.

На алгоритмическом и системном уровнях перечисление неисправностей невозможно из-за большого их числа. Поэтому на этих уровнях практикуется вычисление тестов не для обнаружения конкретных неисправностей или их сочетаний, а для проверки правильности функционирования системы или алгоритма при возможных сочетаниях операндов. Так, на алгоритмическом уровне - это проверка правильности выполнения всех ветвей алгоритма. Классификация методов тестирования и их связи с методами генерации тестовых воздействий и анализа реакции испытываемых устройств представлены на рис.5.5.

Детерминированные методы генерации обеспечивают вычисление совокупности тестовых наборов для тестирования заданной схемы и состоят из следующих этапов: вычисление тестового набора для очередной неисправности из общего списка неисправностей, моделирование схемы на полученном тестовом наборе для выявления подмножества неисправностей, обнаруживае-