Учебное пособие 1484

.pdf

31

Высокий уровень, подаваемый на вход R, сбрасывает все триггеры регистра в состояние низкого уровня. Низкий уровень сигнала S устанавливает все триггеры регистра в состояние высокого уровня, если выбран полином 16-й степени.

В случае выбора полинома 12-й или 8-й степени в состояние высокого уровня устанавливаются только старшие 12 или 8 триггеров, остальные сбрасываются в состояние низкого уровня. Работа микросхемы синхронизируется внешним синхросигналом длительностью не менее 35 нс.

Временная диаграмма работы микросхемы КР1818ВЖ1 и значения динамических параметров приведены на рис.3.1,б. Микросхема полностью совместима по электрическим параметрам с микросхемами серий К589, К583, К155, К1533. Конструктивно микросхема оформлена в 14-выводной пластмассовый корпус. Основные электрические параметры микросхемы КР1818ВЖ1 приведены ниже:

Напряжение источника UCC, В . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 5 %

Ток потребления ICC, мА, не более . . . . . . . . . . . . . . . . . . . . . . . . 80

Входное напряжение, В:

низкого уровня UTL, не более . . . . . . . . . . . . . . . . . . . . . . . . . 0,8

высокого уровня UTH, не менее . . . . . . . . . . . . . . . . . . . . . . . 2,0

Входной ток низкого уровня IIL, мА, не более . . . . . . . . . . . . . . -0,4

Входной ток высокого уровня IIH, мА, не более . . . . . . . . . . . . . 50

Выходное напряжение низкого уровня UOL, В, не более . . . . . . 0,5

Выходное напряжение высокого уровня UOH, В, не менее . . . . 2,4

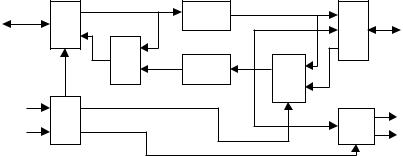

На рис.3.2 приведен пример использования микросхемы КР1818ВЖ1 для контроля ошибки в последовательном канале передачи цифровой информации. Устройство контроля содержит две микросхемы КР1818ВЖ1 (на выходе передатчика RG1 и входе приемника RG2), настроенные на один и тот же полином.

Пример использования БИС К1818ВЖ1

Передат- |

Шина передачи данных |

|

|

|

Прием- |

|

чик |

|

|

|

|

|

ник |

|

|

Шина синхронизации |

|

|

|

|

Код |

SE0SE0 |

|

|

|

SE0SE0 GCH DO |

|

поли- { |

GCH DO |

|

|

|||

SE0 |

|

|

|

SE0 |

|

|

нома |

|

|

|

|

||

|

|

& |

|

|

|

|

|

DI |

|

1 |

DI |

|

|

|

|

|

|

|

||

|

SYN |

|

& |

|

SYN |

|

|

COD |

ER |

'1' |

COD |

ER |

|

|

S |

|

|

|

S |

Шина |

|

R |

|

|

|

R |

|

COD |

|

|

|

|

|

сигнала |

|

|

|

|

|

ошибки |

|

S |

|

|

|

|

|

|

|

|

|

|

|

|

|

R |

|

|

|

|

|

|

Рис. 3.2. Пример использования БИС К1818ВЖ1

32

Передаваемая по каналу информация поступает на вход микросхемы RG1 и делится на выбранный полином. После прохождения информации и поступления сигнала COD остаток деления, содержащийся в RG1 и представляющий собой контрольный код, добавляется к основной информации. Вид остатка в RG1 зависит от каждого бита передаваемой информации, поступающей на его вход, и определяется передаваемой последовательностью. На приемном устройстве информация поступает на вход микросхемы контроля кода RG2. При отсутствии ошибки в принимаемой информации после прохождения данных и остатка, сформированного в RG1, все элементы памяти RG2 установятся в состояние низкого уровня; при этом на выходе ER будет сформирован низкий уровень сигнала. При наличии хотя бы однократной ошибки в принимаемых данных состояние элементов RG2 будет отлично от нулевого и на выходе ER появится высокий уровень сигнала ошибки в принятой информации.

3.2. Повышение надежности систем памяти

Увеличение плотности размещения запоминающих элементов улучшает ряд технико-экономических характеристик полупроводниковой памяти, но одновременно ведет к снижению достоверности хранения данных, вызванному увеличением интенсивности отказов и сбоев. Ряд технологических усовершенствований позволяет снижать интенсивность отказов БИС ЗУ, но уменьшение интенсивности сбоев является более сложной задачей, так как причины появления ошибок - ионизирующее излучение материалов корпуса и электрические помехи. Чем меньшие размеры имеет отдельный запоминающий элемент, тем меньше заряды емкостей в динамических и меньше перепады уровней сигналов в статических ОЗУ, что увеличивает возможность изменения состояния запоминающих элементов под воздействием внешних факторов. Поэтому в системах памяти современных микроЭВМ часто используются встроенные средства функционального и тестового диагностирования, позволяющие значительно повысить надежность хранения информации. Простейшим способом функционального диагностирования памяти является контроль хранящейся информации на четность (нечетность), позволяющий обнаруживать все однократные отказы и сбои. Схемы контроля четности могут быть реализованы на основе 9-разрядных микросхем ИП2, реализующих либо свертку по модулю 2 восьми информационных и контрольного бита (КБ) с выдачей результата этого сложения, либо свертку только восьми информационных разрядов с целью выработки контрольного. Микросхема ИП2 имеется в составе широко распространенной серии К155.

Эффективным способом обеспечения отказоустойчивости систем памяти является введение динамической избыточности, основанной на применении корректирующих кодов. Наибольшее распространение среди них в настоящее время имеют коды Хэмминга. Основными достоинствами кодов Хэмминга, обусловившими их популярность, являются возможность обнаружения и исправления ошибок, вызванных как отказами, так и сбоями элемен-

33

тов памяти, относительно низкая избыточность и простая реализация устройств кодирования/декодирования.

Для защиты 16-разрядных устройств памяти кодом Хэмминга предна-

значена ТТЛШ БИС обнаружения и исправления ошибок (ОИО) К555ВЖ1,

структура которой приведена на рис.3.3. БИС ОИО содержит коммутаторы К1 и К2 шин данных D (15-0) и контрольных битов/синдромов CB/S (5-0), формирователь контрольных битов CBG, формирователь синдромов SG, дешифратор ошибок DER, блок коррекции CL, схему формирования флагов сообщения об однократных (ER) и многократных (MER) ошибках, блок управления

CU /3,4,5/.

D(15-0) |

K1 |

|

CBG |

K1 |

CSB |

|

|

|

|

||

|

|

|

|

(5-0) |

|

|

|

|

|

|

|

|

|

CL |

DER |

|

|

|

|

|

SG |

|

|

|

|

|

|

|

|

U1 |

CU |

|

|

|

ER |

U2 |

|

|

FG |

||

|

|

|

MER |

||

|

|

|

|

Рис. 3.3. Структура БИС ОИО К555ВЖ1

Микросхема К555ВЖ1 позволяет исправлять одиночные и обнаруживать все двойные ошибки в ЗУ, определять преобладание долей ошибок малой кратности в общем числе ошибок. Контрольные разряды кода Хэмминга формируются в CBG путем сложения разрядов информационного слова, помеченных в табл. 3.2. Входы управления U1 и U2 позволяют задавать четыре режима работы БИС:

U1=L, U2=L - формирование КБ при записи информации в память; U1=H, U2=L - запись данных и КБ из ЗУ в БИС ОИО;

U1=H, U2=H - блокировка информации и разрешение флагов ошибки; U1=L, U2=H - выдача информационного слова из БИС ОИО.

Вцикле записи информации в память слово данных поступает на шину D (15-0) БИС ОИО, где формируются шесть контрольных разрядов, которые выдаются на шину CB/S (5-0) и записываются в специально отведенные разряды накопителя.

Вцикле чтения КБ восстанавливаются вместе с исходными данными. Для этого прочитанное слово данных снова сворачивается для получения новых КБ, которые сравниваются со старыми (прочитанными из ЗУ). Результат сравнения старого и нового контрольных слов (синдром) содержит информацию о наличии ошибки и ее месте. Если все разряды синдрома равны единице, то ошибок нет и флаги ER, MER не устанавливаются. Единичная ошибка в слове данных изменяет три бита контрольного слова, а ошибка в хранении КБ

Таблица 3.2 Формирование контрольных разрядов кода Хэмминга

34

Кон- |

|

|

|

|

|

|

|

Слово данных |

|

|

|

|

|

|||

троль- |

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ный |

D0 |

D1 |

D2 |

D3 |

D4 |

D5 |

D6 |

D7 |

D8 |

D9 |

D10 |

D11 |

D12 |

D13 |

D14 |

D15 |

|

||||||||||||||||

разряд |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CB0 |

X |

X |

- |

X |

X |

- |

- |

- |

Х |

Х |

Х |

- |

- |

Х |

- |

- |

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CB1 |

X |

- |

X |

X |

- |

X |

X |

- |

Х |

- |

- |

Х |

- |

- |

Х |

- |

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CB2 |

- |

X |

X |

- |

X |

X |

- |

X |

- |

Х |

- |

- |

Х |

- |

- |

Х |

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CB3 |

X |

X |

X |

- |

- |

- |

X |

X |

- |

- |

Х |

Х |

Х |

- |

- |

- |

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CB4 |

- |

- |

- |

X |

X |

X |

X |

X |

- |

- |

- |

- |

- |

Х |

Х |

Х |

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CB5 |

- |

- |

- |

- |

- |

- |

- |

- |

Х |

Х |

Х |

Х |

Х |

Х |

Х |

Х |

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

- только один. В любом из этих случаев будет установлен флаг однократной ошибки ER и произведена коррекция информации. Двойные ошибки вызывают установку флагов ER и MER. Тройные ошибки (и ошибки большей кратности) могут привести к тому, что БИС К555ВЖ1 не будет обнаруживать ошибок. Код синдрома однозначно указывает на место однократной ошибки, как это показано в табл. 3.3. Синдром расшифровывается в дешифраторе ошибок DER, который управляет блоком инверторов в узле коррекции CL. Коррекция слова данных производится путем инвертирования значения разряда, указанного дешифратором ошибки. Контрольные разряды не корректируются.

Микросхема К1804ВЖ1 - 16-разрядное устройство обнаружения и исправления ошибок (УОИО), предназначенное для работы в составе блоков оперативной памяти вычислительных систем. Структурная схема УОИО приведена на рис.3.4 и содержит четыре восьмиразрядных регистра данных (RD0, RD1, RB0, RB1), 7-разрядный регистр контрольных битов (RKB), 16-разрядный регистр режима диагностики (RRD), генератор контрольных битов (KBG), генератор признаков ошибки (SG), схему обнаружения ошибки (DER1), дешифратор одиночной ошибки (DER2), схему коррекции ошибки (KL), три 7- разрядных коммутатора (KA, KB, KC), 7-разрядный буфер признаков ошибки (BF) и устройство управления (CU).

Микросхема реализована на основе ТТЛШ-схемотехники и использует в магистралях D0-D15, DCOY0-DCOY5 выходные каскады с тремя состояниями, а на входах - входные каскады со стандартными ТТЛ-уровнями сигналов./3,4,5/.

Микросхема имеет 48 выводов, назначение которых описано в табл.3.4.

Таблица 3.3

35

Использование синдрома для указания места однократной ошибки

1 |

63 |

62 |

61 |

60 |

59 |

58 |

57 |

56 |

55 |

54 |

53 |

52 |

51 |

50 |

49 |

48 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2 |

HO |

CB |

CB |

- |

CB |

- |

- |

- |

CB |

- |

- |

D0 |

- |

D1 |

D2 |

- |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

47 |

46 |

45 |

44 |

43 |

42 |

41 |

40 |

39 |

38 |

37 |

36 |

35 |

34 |

33 |

32 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2 |

CB |

- |

- |

D3 |

- |

D4 |

D5 |

- |

- |

- |

D6 |

- |

D7 |

- |

- |

- |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2 |

CB |

- |

- |

D8 |

- |

D9 |

- |

- |

- |

D1 |

D1 |

- |

D1 |

- |

- |

- |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2 |

- |

D1 |

D1 |

- |

D1 |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Примечание. 1 - значение кода синдрома; 2 - номер помечаемого раз- |

|

||||||||||||||

ряда слова данных или контрольного слова; НО - нет ошибок. |

|

|

|||||||||||||

EZD0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

EZD1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

EWRDY |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

7 |

|

|

7 |

DER |

8 |

|

|

|

|

|

|

|

8 |

|

|

7 |

|

KB |

|

8 |

|

|

|||

D7-D0 |

|

|

|

|

|

|

1 |

|

|

RB0 |

|

||||

|

|

|

6 |

|

|

|

|

|

|

||||||

|

|

RD0 |

|

|

|

|

|

8 |

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

KL |

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

KBG |

|

|

|

|

16 |

|

|

|

|

|

|

|

|

8 |

|

|

|

|

|

|

|

|

|

|

|

|

D15-D8 |

|

|

8 |

|

7 |

|

|

|

|

|

|

|

|

8 |

|

|

|

|

|

|

|

|

|

|

|

8 |

|

||||

|

|

|

RD1 |

|

|

|

|

|

|

|

RB1 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

SG |

|

|

|

7 |

|

|

|

8 |

|

|

|

7 |

|

|

|

7 |

|

|

|

|

|

DC0Y6-DC0Y0 |

|

||

DC00-DC06 |

|

|

7 |

|

7 |

|

|

|

|

BF |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

RKB |

|

KA |

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

KC |

|

|

|

|

|

|

|

||

EWRD |

|

|

|

7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

7 |

|

DER |

ER |

|

|

EWRINS |

|

8 |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

RRD |

|

|

|

|

|

|

|

|

2 |

ERM |

|

|

|

|

7 |

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

INS0-INS2 |

|

|

|

|

|

Внутренние |

|

|

|

|

|

|

|

|

|

INS3-INS4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

CU |

управляющ ие |

|

|

|

|

|

|

|

|||

INS7 |

|

|

|

|

|

|

|

|

|

|

|

||||

INS6 |

|

|

|

|

|

сигналы |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

INS5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

EZDCOY |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 3.4. Структура УОИО К1804ВЖ1 |

|

|

|

||||||||

Микросхема УОИО позволяет обнаруживать и исправлять ошибки, возникающие при записи и считывании запоминающих устройств; исправляет все однобитовые ошибки, обнаруживает все двойные и некоторые тройные

36

ошибки, а также ошибки типа 00...00, допускает наращивание и побайтную работу, имеет встроенную диагностику для самоконтроля. Система команд УОИО обеспечивает девять режимов работы, из которых три являются диагностическими: начальная установка, прямая передача, генерация контрольных битов, обнаружение ошибки, диагностика обнаружения ошибки, диагностика коррекции ошибки, режим внутреннего управления.

Таблица 3.4

Назначение выводов микросхемы К1804ВЖ1

Обозначение |

Функциональное назначение |

D (0-15) |

Двунаправленная шина данных |

DCO (0-6) |

Шина контрольных данных |

INS (0-7) |

Шина управления |

DCOY (0-5) |

Шина контрольных данных |

EWRINS |

Разрешение записи микрокоманд |

EWRD |

Разрешение записи входных данных |

EWRDY |

Разрешение записи выходных данных |

EZD1 |

Разрешение выдачи данных: 1-й байт |

EZD0 |

Разрешение выдачи данных: 0-й байт |

EZDCOY |

Разрешение выдачи контрольных дан- |

|

ных |

ER |

Признак однократной ошибки |

ERM |

Признак многократной ошибки |

UCC |

Напряжение питания (+5 В) |

GND |

Напряжение питания (0 В) |

Микросхема функционирует следующим образом. Входные данные по шине данных D(0-15) загружаются в регистры данных RD0, RD1 под управлением сигнала EWRD (высокий уровень сигнала EWRD - состояние RD0, RD1 соответствует входам D(0-7), D(8-15), низкий уровень сигнала - сохранение предыдущего состояния RD0, RD1). Контрольные биты по шине DCO(0-6) загружаются в регистр контрольных битов (RKB) также под управлением сигнала EWRD, который определяет состояние RKB аналогично регистрам данных. В соответствии с модифицированным кодом Хэмминга генератор контрольных битов KBG вырабатывает контрольные биты под управлением сигнала INS6 (низкий уровень INS6 - KBG генерирует контрольные биты, высокий уровень - осуществляет режим обнаружения и коррекции ошибки). При этом KBG генерирует полный набор контрольных битов для 16-разрядного формата данных и часть - для 32-, 64-разрядных форматов и выдает их на магистраль контрольных битов DCOY. Генератор признаков ошибки SG генерирует признаки ошибки путем сравнения контрольных битов, считываемых с RKB с контрольными битами, генерируемыми KBG по данным, считанным с RD0, RD1. Признаки формируются схемой «исключающее ИЛИ» по двум наборам

37

контрольных битов, и при отсутствии ошибки все биты признаков находятся в состоянии логического «0»; при наличии ошибки один или несколько битов признаков будут находиться в состоянии логической «1». Схема обнаружения ошибки DER1 дешифрует биты признаков ошибки, вырабатываемых SG под управлением сигналов INS6 (при высоком уровне сигнала INS6 на выходах ER, ERM индуцируется тип ошибки, при низком - на выходах ER, ERM высокий уровень сигнала). При наличии хотя бы одной ошибки выход ER устанавливается в состояние низкого уровня, при наличии двух и более низкий уровень устанавливается и на выходе ERM.

Устройство управления CU является комбинационной схемой и управляет режимами работы микросхемы в соответствии с микрокомандами (табл. 3.5 - 3.8). В режиме внутреннего управления сигналы считываются из RRD, во всех остальных - с входов INS(0-5), INS7.

Таблица 3.5

|

|

Режимы работы УОИО |

|

|

|

|

|

INS4 |

INS3 |

Режим работы микросхемы |

|

0 |

0 |

Режим недиагностический, нормальная работа во всех ре- |

|

жимах |

|||

|

|

||

|

|

Режим диагностической генерации; содержимое RRD под- |

|

0 |

1 |

ставляется вместо нормально генерируемых контрольных |

|

битов; нормальная работа в режимах обнаружения и коррек- |

|||

|

|

||

|

|

ции ошибок |

|

|

|

Режим диагностического обнаружения или коррекции оши- |

|

1 |

0 |

бок; содержимое RRD подставляется вместо контрольных |

|

|

|

битов, нормально считываемых из RKB |

|

|

|

Режим начальной установки; выходы RD0, RD1 устанавли- |

|

1 |

1 |

ваются в нули, и контрольные биты вырабатываются для |

|

|

|

данных, состоящих из нулей |

Дешифратор одиночной ошибки DER2 дешифрирует биты признаков ошибки, вырабатываемых SG под управлением сигналов INS6, INS5, а также внутреннего сигнала типа ошибки, определяет разряд данных, в котором допущена однократная ошибка, преобразуя 7-разрядный код признаков ошибки в 16-разрядный код, который подается на KL. Дешифрация осуществляется при высоком уровне сигналов INS5, INS6 и отсутствии сигнала многократной ошибки. Схема коррекции ошибок KL принимает с RD0, RD1 16-разрядный код, а DER2 - 16-разрядный дешифрированный код местоположения ошибки. При наличии одиночной ошибки KL корректирует неверный бит путем его инвертирования. Скорректированные данные загружаются в регистры RB0, RB1 и затем выгружаются в шину данных. При обнаружении ошибки в контрольных битах KL не проводит коррекцию контрольных битов.

Регистры выходных данных RB0, RB1 используются для хранения результата коррекции и управляются сигналом EWRDY (при высоком уровне

38

сигнала EWRDY регистры RB0, RB1 работают в режиме прямой передачи, при низком уровне сохраняют предыдущее состояние). При наличии высокого уровня сигнала INS6, INS7 осуществляется прямая передача из RD0, RD1 в RB0, RB1, при низком уровне состояние RB0, RB1 не определяется. Выдача данных на магистраль D(0-15) осуществляется под управлением сигналов EZD0, EZD1: при низком уровне происходит выдача данных, при высоком магистраль отключена. Регистр режима диагностики загружается с шины данных под управлением сигнала EWRINS: при низком уровне состояние RRD соответствует шине данных, при высоком сохраняется предыдущее состояние. RRD используется также для хранения контрольных битов, применяемых в диагностических режимах, и внутренних управляющих сигналов INS(0-5), INS7, для управления и обеспечения контрольными битами в режиме диагностики.

Таблица 3.6

|

Работа УОИО в различных режимах |

||||

|

|

|

|

|

|

|

Вход в ди- |

Вход |

|||

Режим работы |

агностиче- |

||||

|

|

||||

|

ском режи- |

|

|

||

|

ме |

|

|

||

|

INS4 |

INS3 |

0 |

1 |

|

Нормальный |

0 |

0 |

Генерация |

Коррекция |

|

Диагностика гене- |

0 |

1 |

Диагностика гене- |

» |

|

рации |

|

|

рации |

|

|

Диагностика кор- |

1 |

0 |

Генерация |

Диагностика кор- |

|

рекции |

|

|

|

рекции |

|

Начальная установ- |

1 |

1 |

Начальная установка |

Начальная установ- |

|

ка |

|

|

|

ка |

|

Прямая передача |

При подаче на вход INS7 сигнала «1» обеспечивается |

||||

|

|

|

режим прямой передачи |

||

39

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Таблица 3.7 |

||

|

|

|

|

|

|

Варианты кода Хэмминга |

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

Разрядность слова |

|

|

|

Вариант кода Хэмминга |

|

|

||||||||||

|

|

|

|

16 / 22 |

|

|

32 / 39 |

|

|

64 / 72 |

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

Данные |

|

|

|

|

16 |

|

|

32 |

|

|

|

64 |

|

||

|

|

Контрольные биты |

|

|

|

6 |

|

|

7 |

|

|

|

8 |

|

||||

|

|

|

Всего битов: |

|

|

|

|

22 |

|

|

39 |

|

|

|

72 |

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Таблица 3.8 |

||

|

|

|

|

Выбор вариантов кода Хэмминга |

|

|

|

|||||||||||

|

|

|

|

|

|

|

||||||||||||

|

INS2 |

|

INS1 |

INS0 |

|

Код Хэмминга и выбранные байты данных |

|

|||||||||||

|

0 |

|

0 |

0 |

|

|

|

|

|

Код 16 / 22 |

|

|

|

|||||

|

0 |

|

0 |

1 |

|

|

|

|

Режим внутреннего управления |

|

|

|||||||

|

0 |

|

1 |

0 |

|

|

|

|

|

Код 32 / 39, байты 0 и 1 |

|

|

|

|||||

|

0 |

|

1 |

1 |

|

|

|

|

|

Код 32 / 39, байты 2 и 3 |

|

|

|

|||||

|

1 |

|

0 |

0 |

|

|

|

|

|

Код 64 / 72, байты 0 и 1 |

|

|

|

|||||

|

1 |

|

0 |

1 |

|

|

|

|

|

Код 64 / 72, байты 2 и 3 |

|

|

|

|||||

|

1 |

|

1 |

0 |

|

|

|

|

|

Код 64 / 72, байты 4 и 5 |

|

|

|

|||||

|

1 |

|

1 |

1 |

|

|

|

|

|

Код 64 / 72, байты 6 и 7 |

|

|

|

|||||

Временная диаграмма работы микросхемы приведена на рис.3.5, а ос- |

||||||||||||||||||

новные электрические параметры микросхемы ниже: |

|

|

|

|

|

|

||||||||||||

Напряжение источника UCC, В |

. . . |

. . . . . . . |

|

. . . . . |

. . . . . . . |

|

. . . . |

. . |

5 5 % |

|

||||||||

Выходное напряжение низкого уровня UOL, В, не более . . . . . |

. . |

0,5 |

|

|||||||||||||||

Выходной ток низкого уровня IOL, мА, не более . |

. . . . . . |

|

. . . . . |

. . |

8,0 |

|

||||||||||||

Выходное напряжение высокого уровня UOH, В, не менее . . . . |

. . |

2,4 |

|

|||||||||||||||

Выходной ток высокого уровня IOH, мА, . . . . . . . . . . . . . . . . . . . . |

-0,8 |

|

||||||||||||||||

Входной ток низкого уровня IIL, мА, не более: |

|

|

|

|

|

|

||||||||||||

|

для D (0-15) . . . . . . |

. . . . |

|

. . |

. . . . |

. . . . . . |

|

. . . . . . |

. . . . . . |

. |

. . . . |

. . |

-0,41 |

|

||||

|

остальные |

. . . . . . |

. . |

. . . |

|

. . . |

. . . . |

. . . . . |

|

. . . . . . . |

. . . . . . |

|

. . . . . |

. |

-0,36 |

|

||

Входной ток высокого уровня IIH, мкА, не более: |

|

|

|

|||||||||||||||

|

для D (0-15) . . . . . . . |

. . . |

|

. . |

. . . . |

. . . . . . |

|

. . . . . . |

. . . . . . |

. |

. . . . |

. . |

70 |

|

||||

|

остальные |

. . . . . . |

. . . |

. . |

|

. . . |

. . . . |

. . . . . |

|

. . . . . . . |

. . . . . . |

|

. . . . . |

. |

50 |

|

||

Ток потребления ICC, мА, не более . |

. . . . . |

|

. . . . . . . |

. . . . . . |

|

. . . . . |

. |

400 |

|

|||||||||

Время задержки распространения сигнала tp, нс, не более: |

|

|

|

|||||||||||||||

|

от DCO до D . . . . . . |

. . |

. |

. . |

. . . . |

. . . . . . |

|

. . . . . . |

. . . . . . |

|

. . . . . |

. |

61 |

|

||||

|

от DCO до ERM . . . . |

. . |

|

. . . |

. . . . |

. . . . . . |

|

. . . . . . |

. . . . . . |

|

. . . . . |

. |

50 |

|

||||

|

от D до ER (обнаружение) |

. . . . |

. . . . . |

|

. . . . . . . |

. . . . . . |

|

. . . . . |

. |

36 |

|

|||||||

|

от D до DCOY (генерация) . . . . |

. . . . . |

. |

. . . . . . |

. . . . . . |

|

. . . . . |

. |

35 |

|

||||||||

40 |

D15-D0 |

DC06-DC00 |

EWRD |

EWRINS |

EWRDI |

>0 |

INS2-INS0 |

>0 |

INS3-INS4 |

>0 |

INS6 |

>0 |

INS7 |

>0 |

INS5 |

Рис. 3.5. Временные диаграммы работы БИС К1804ВЖ1 |

Для проверки работоспособности блоков памяти часто используют тестовые методы диагностики, которые могут быть реализованы как программно, так и аппаратно. Имеются и микросхемы, обеспечивающие аппаратную поддержку методов тестового диагностирования.

БИС КР1828ВЖ1 предназначена для построения ядра схем тестового диагностирования ПЗУ, процессоров и контроллеров. Структура микросхемы приведена на рис.3.6, а, описание выводов дано в табл.3.9. БИС содержит: устройство управления (CU), управляющее на основе микрокоманды INS(4-0) и внешних сигналов работой всех узлов БИС; операционное устройство (AU), выполняющее необходимые преобразования данных; схему сравнения (CMP) для компарации полученных результатов с эталонными значениями; блок входного переноса (BCI), обеспечивающий работу БИС в режиме сигнатурного анализа; узел индикации (BI), предназначенный для формирования результатов тестирования в виде сигналов «Да» (Y), «Нет» (N) и секционного наращивания БИС.

БИС КР1828ВЖ1 имеет следующие режимы работы: генератор псевдослучайных кодов с максимальным периодом 255; генератор инкрементируемых и декрементируемых последовательностей; сигнатурный анализатор без сравнения или со сравнением с эталоном; счетчик числа переходов без сравнения или со сравнением с эталоном, сумматор со сравнением полученной и контрольной сумм /4/.

Таблица 3.9