Основы эксплуатации вычислительной техники. Афанасьев Л.А., Тюрин С.В

.pdf

21

Для пояснения процедуры формирования циклического кода и его декодирования введем следующие обозначения:

G(x) - информационный полином, соответствующий передаваемой информации длиной m бит. Он имеет степень не больше m-1;

P(x) - порождающий полином степени k, определяющий число контрольных бит, а также обнаруживающую и корректирующую способность циклического кода;

F(x) - кодовый полином, соответствующий передаваемому циклическому коду. Это полином степени m+k, делящийся без остатка на порождающий полином степени k.

Образование кодового полинома F(x) путем умножения информационного полинома G(x) на порождающий P(x) неудобно тем, что получающийся при этом код не будет систематическим ( контрольные биты не будут выделены). Вследствие этого применяется другой способ формирования кодового полинома, при котором старшие коэффициенты образуют информационные знаки, а младшие - контрольные. Информационный полином G(x) степени m- 1, который необходимо закодировать, умножается на xk , что соответствует сдвигу на k разрядов влево. Полученный таким образом полином xkG(x) делится на P(x) для определения остатка R(x) степени меньше k, что всегда возможно:

xk G(x) / P(x) = Q(x) |

R(x) / P(x). |

Из этого выражения следует: |

|

xk G(x) = Q(x) P(x) |

R(x); |

F(x) = Q(x) P(x) = xk G(x) R(x).

Полином F(x) делится на P(x) без остатка и поэтому является кодовым полиномом.

Остаток R(x) имеет степень меньше k, и xk G(x) имеет нулевые коэффициенты в k младших членах. Таким образом, m старших коэффициентов кода F(x) равны коэффициентам информационного полинома G(x) и представляют собой кодируемое сообщение, а младшие k коэффициентов кодового полинома F(x) представляют собой коэффициенты остатка R(x), т.е. контрольные биты. Из приведенного выше следует, что кодовый полином можно получить путем сдвига информационного полинома на k бит, деления его на порождающий полином F(x) и записи остатка в младшие k бит кодового полинома. Процедура кодирования, соответствующая этому алгоритму, реализуется с помощью сдвигового регистра с обратными связями, соответствующими виду порождающего полинома P(x).

Если полином, полученный при передаче сообщения, содержит ошибки, то он может быть представлен в виде

H(x) = F(x) E(x).

Это выражение означает, что если полином принятого сообщения H(x) не делится на P(x), то при передаче информации произошла ошибка E(x).

Выбор порождающего полинома P(x) зависит от характера ошибок при передаче. Можно записать правила выбора порождающего полинома для разных ошибок:

22

*ошибки в одном бите обнаруживаются, если порождающий полином содержит более одного члена;

*ошибки в двух битах обнаруживаются, если порождающий полином содержит три члена;

*ошибки в нечетном числе бит обнаруживаются, если порождающий полином содержит множитель x+1;

*пакеты ошибок длиной менее k+1 бит обнаруживаются, если порождающий полином содержит множитель х+1 и один множитель с тремя

членами и более (k+1 - число бит порождающего полинома). Этот же порождающий полином обнаруживает с вероятностью 1 - (1/2)k-1 пакеты ошибок длиной более k+1 бит, с вероятностью 1 - (1/2)k пакеты ошибок длиной более k+1 бит.

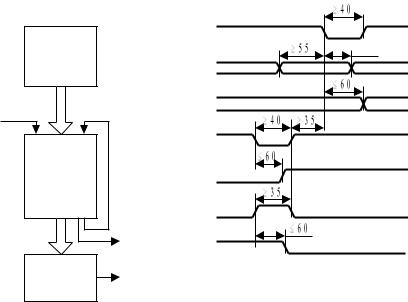

На рис. 2.2 показана схема сдвигового регистра с обратными связями и схемами сложения по модулю 2, реализующими схему деления на порождающий полином.

Важным преимуществом таких схем является возможность их применения для контроля передаваемой информации как при приеме, так и при генерации контрольных бит при передаче, что позволяет обойтись одной такой схемой в приемной и передающей аппаратуре.

G(x) или Н(х) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

F(x) |

Tr1 |

|

Tr2 |

Tr3 |

Tr4 |

ИЛИ |

|

||||

|

T |

|

|

T |

|

T |

|

T |

|

|

D |

M2 |

D |

D |

D |

& |

|

||||

|

|

|

|

|

|

|

||||

C |

|

|

C |

|

C |

|

C |

|

И 2 |

|

Сдвиг |

|

|

|

|

|

|

|

|

|

|

|

M2 |

1 |

X |

|

|

|

|

|

|

|

a |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

& |

|

|

|

|

|

|

|

|

|

|

И 1 |

|

|

|

|

|

|

|

|

|

|

b |

|

|

|

|

|

|

|

|

|

|

Рис.2.2. Схема формирования и декодирования циклического кода |

||||||||||

Рассмотрим в качестве примера схему (рис. 2.2), реализующую деление на порождающий полином P(x) = x4 + x + 1. Предположим, что передаются данные вида 11010011, которые представляются в виде полинома G(x) = x7 + +x6 + x4 + x + 1. Как было сказано, циклический код передаваемых данных образуется путем умножения информационного полинома G(x) на x4: x4G(x) = =x4 (x7 + x6 + x4 + x + 1), что эквивалентно сдвигу данных, соответствующих информационному полиному G(x), на 4 бит в сдвиговом регистре.

23

Как только первая единица (коэффициент при старшем члене полинома) сдвинется до конца регистра, т.е. появится на выходе триггера Tr4 при очередном сдвиге, будет выполнено вычитание делителя. Проследим за процессом деления x4 G(x) на P(x) и образования остатка:

|

|

|

|

x4 G(x) = 110100110000 |

|

|

|

|

|

P(x) = 10011 |

|

110100110000 |

10011 |

_ |

|

||

10011 |

_ |

|

110000111 - частное |

||

10010 |

|

|

|

|

|

10011 |

_ |

|

|

|

|

11100

10011 _

11110

10011_

11010

10011

1001 - остаток, т.е. R(x).

Втечение первых восьми тактов сдвига на входе а схемы И1 имеется разрешение. Данные, соответствующие информационному полиному, одновременно с передачей на выходе схемы ИЛИ поступают также и в сдвиговый регистр. К началу девятого такта разрешение со входа а снимается, а на вход b

схемы И2 подается разрешение, в результате чего на выход схемы поступает остаток R(x), накопившийся в сдвиговом регистре. Таким образом, на выходе схемы ИЛИ образуется последовательность бит, соответствующая кодовому полиному F(x) = 110100111001.

Втом случае, когда описанная схема используется для декодирования принятой информации (обнаружение ошибок), на ее вход поступает последовательность полинома H(x). Если после m+k сдвигов сдвиговый регистр находится в нулевом состоянии, это означает, что передача выполнена без ошибок.

Циклические (полиномиальные) коды получили широкое распространение благодаря высокой обнаруживающей способности и относительной простоте схем кодирования и декодирования.

2.8. Контроль арифметических и логических операций

Все рассмотренные выше коды использовались для контроля передачи информации. Особенностью подобного вида контроля является то, что с его помощью решается сравнительно несложная задача - убедиться в неизменности передаваемой информационной комбинации или восстановить эту информацию, если в ней произошли искажения. Совсем другие требования возникают при контроле обрабатываемой информации, которая не остается постоянной, а все время изменяется в процессе тех или иных операций. Следовательно, в этом случае необходимо обеспечить контроль правильности ее

24

преобразования, т.е. правильности выполнения этих операций. И если возникшая ошибка при передаче информации искажает одно число или отдельные числа, не связанные друг с другом, то та же ошибка при расчетах начинает распространяться в вычислительном процессе, поскольку исходные данные одной операции являются результатом предшествующих операций.

Из множества разработанных методов контроля арифметических операций наибольшее распространение получил контроль по модулю, который называют также контролем по остаткам или наименьшим вычетам. Суть организации такого контроля заключается в том, что каждому числу, участвующему в операции, ставится в соответствие контрольный код, который представляет собой остаток от деления контролируемого числа на некоторое заранее заданное целое число q, называемое модулем. Использование остатка в качестве контрольного кода возможно по той причине, что любое число А сравнимо с этим остатком.

При выполнении операций над числами та же операция выполняется над их контрольными кодами, после чего контрольный код результата основной операции сравнивается с результатом аналогичной операции над контрольными кодами исходных чисел. Это вытекает из теории чисел, которая говорит, что для произвольных целых чисел А и В справедливо равенство (в случае операции сложения)

|

R(A+B) = R [ R(A)+R(B) ], |

(2.1) |

||

где R(X) означает остаток числа Х по модулю q. |

|

|||

|

Если сравнение указанных результатов дает совпадение, операция счи- |

|||

тается выполненной правильно, при несовпадении фиксируется ошибка. |

||||

|

Представим каждое из чисел А и В в виде |

|

||

|

А = q |

+ ; B = q + , |

|

|

где |

и - частные от деления соответственно А на q и В на q (целые числа), а |

|||

и |

- остатки чисел А и В по модулю q, т.е. |

=R(A), =R(B). Тогда сумма чи- |

||

сел |

|

|

|

|

|

A+B = (q + |

+ q + |

= q( + )+( |

+ ). |

Разделим правую и левую части равенства на q: (А+В) / q = ( + ) + ( + ) / q.

Значение + представляет собой целую часть от деления А+В на q, т.е. частное. Следовательно, остаток от суммы А+В

представляет собой целую часть от деления А+В на q, т.е. частное. Следовательно, остаток от суммы А+В

R(A+B) = R( + ),

что совпадает с выражением (2.1).

Рассуждая подобным же образом, можно убедиться в справедливости рассмотренного положения и для других операций (умножение, деление).

Значение q выбирается с таким условием, чтобы: 1) любая одиночная ошибка приводила к нарушению условия сравнимости результатов по модулю q; 2) операция деления для определения остатка была заменена более простыми действиями и осуществлялась по сравнительно несложным признакам делимости; 3) аппаратура, реализующая контроль по модулю, была проще, а это

25

возможно при меньших значениях q, когда контрольные коды имеют малое число разрядов.

Из первого условия следует, что в качестве основания нельзя выбирать числа типа 2n (n - целое число), поскольку при этом одиночные ошибки в старших разрядах не нарушают сравнимости по модулю q и, следовательно, не могут быть обнаружены. Этому условию удовлетворяют прежде всего основания типа 2n+1. Если принять во внимание, что вероятность появления двойных ошибок крайне мала, эффективность контроля при разных основаниях типа 2n 1 будет отличаться незначительно. Следовательно, целесообразно остановиться на основании 22-1 = 21+1 = 3, т.е. на контроле по модулю 3, позволяющем наиболее просто и экономично реализовать схему контроля.

Для нахождения остатка от деления двоичного числа на модуль 3 достаточно просуммировать цифры разрядов контролируемого числа по модулю 3 с учетом знаков четных и нечетных разрядов, что удовлетворяет второму условию.

Одиночная ошибка в одном из разрядов двоичного числа соответствует его изменению на 2i. Для возможности обнаружения ошибки необходимо, чтобы контрольные коды чисел А и А 2i не совпадали, т.е. нужно выполнить условие

R(A) R(A 2i)

|

|

|

|

|

|

|

|

|

|

|

A+B |

|

|

|

|

|

|

А |

|

|

|

Основной |

Схема |

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

формирования |

|

|

|||

В |

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

сумматор |

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

остатков |

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

R(A+B) |

|

|

|

|

|

|

|

Схема |

R(A) |

|

|

|

|

|

|

|

Сигнал |

|||

|

|

|

|

|

формирования |

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ошибки |

||

|

|

|

|

|

остатка |

|

|

|

Сумматор |

R [ R(A)+R(B) ] |

Схема |

||||||

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

остатков |

|

|

|

|

сравнения |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

Схема |

R(B) |

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

формирования |

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

остатка |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

Рис. 2.3. Структурная схема сумматора с контролем по модулю 3.

Поскольку 2i не делится на 3 без остатка, последнее условие всегда выполняется. Кроме одиночных ошибок контроль по модулю 3 выявляет все двойные ошибки, для которых справедливо указанное условие.

На рис. 2.3 приведена структурная схема сумматора с контролем по модулю 3, общая логика работы которого ясна из рисунка.

Контроль логических операций, в частности таких поразрядных операций, как логическое сложение (ИЛИ), логическое умножение (И) и исключающее ИЛИ, не имеет такой структуры, как контроль арифметических опе-

26

раций. Объясняется это тем, что в отличие от арифметических логические операции выполняются поразрядно и результат операции в каждом конкретном разряде определяется только состоянием соответствующих разрядов операндов, не связанных с другими разрядами чисел. Следовательно, для большинства логических операций невозможно найти общие контрольные разряды, которые оказались бы совместными с данной операцией. Реализация же поразрядного схемного контроля в принципе возможна, но неэкономична, так как это потребует резкого увеличения контрольной аппаратуры.

По этой причине наиболее целесообразным является осуществление контроля логических операций путем их повторения, т.е. путем использования временной избыточности. При этом увеличение времени исполнения таких операций не является столь критичным, поскольку в целом выполнение логических операций занимает сравнительно небольшую часть общего времени выполнения программы.

Другим методом контроля является одновременное выполнение двух разных логических операций с последующим сравнением результатов по модулю 3. Для этих целей используют некоторые соотношения между результатами двух различных логических операций над операндами А и В и их алгеб-

раической суммой А+В. |

|

|

|

Примером таких соотношений могут служить выражения |

|

||

( A |

B ) + ( A |

B ) = A + B; |

(2.2) |

2 ( A |

B ) + ( A |

B ) = A + B. |

(2.3) |

Подставив любые значения отдельных разрядов Аi и Вi, нетрудно убедиться, что оба слагаемых в левой части равенств (2.2) и (2.3) будут содержать вместе столько же единиц, сколько и в правой части обоих выражений, что подтверждает справедливость обоих равенств.

Для контроля выбирают то равенство, в которое входит контролируемая операция (например, для контроля операции неравнозначности выбирается второе соотношение). После этого одновременно выполняются обе логические операции, входящие в левую часть равенства. Затем определяются сумма контрольных кодов операндов А и В (по модулю 3) и сумма контрольных кодов результатов обеих логических операций (по тому же модулю), после чего обе суммы контрольных кодов (операндов и результатов логических операций) сравниваются. Неравенство сумм вырабатывает сигнал ошибки.

27

2.9. Сравнительные характеристики избыточных

кодов

Сравнение кодов между собой производится по двум основным характеристикам: относительной избыточности R и корректирующей способности (потенциальной эффективности) K.

Относительная избыточность кодов позволяет оценивать их с точки зрения объема контрольной аппаратуры, которая усложняется с ростом R. Правда, здесь не существует линейной зависимости, и многое определяется алгоритмом реализации работы данного вида кода. Поэтому указанная оценка является приближенной.

Потенциальная эффективность кода характеризует способность данного кода обнаруживать (или обнаруживать и исправлять) ошибки, возникающие в информации при ее передаче или обработке, т. е. показывает степень уменьшения вероятности появления необнаруженных ошибок при использовании данного кода для контроля информации в машине.

Значение K также является ориентировочным, так как рассчитано из условия, что возникновение ошибок в отдельных разрядах информационной комбинации можно считать независимым случайным событием, имеющим равную вероятность (биномиальный закон распределения ошибок, справедливый при параллельной передаче и обработке информации), что не всегда справедливо.

Кроме того, сам по себе выбор системы контроля для машины зависит от многих факторов, о которых говорилось ранее. Поэтому не существует единых рецептов по применению методов и средств контроля, следовательно, и оценку применимости того или иного кода в тех или иных случаях следует воспринимать как ориентировочную /4-9/.

Код с проверкой четности и код Хэмминга, очевидно, целесообразно применять в случае, если предполагается контролировать передачу информации параллельным кодом (внутренние передачи информации в машине), когда справедлив биномиальный закон распределения ошибок. При увеличении вероятности появления групповых ошибок эффективность, например, кода четности снижается несущественно, если контрольным знаком снабжается каждый блок информационной комбинации (в современных машинах это байты, в каждом из которых девятый разряд является контрольным).

Однако код с проверкой четности только фиксирует ошибку, которая часто устраняется путем повторной передачи данных. Если повторная передача затруднена, обычно используются коды, исправляющие ошибки.

При работе с такими ЗУ, как магнитная лента, диски, барабаны, в некоторых системах применяется дублирование записей. При отсутствии такого дублирования и повышенных требованиях к достоверности целесообразно применять код Хэмминга, а там, где это возможно, - его циклический вариант, требующий более простой контрольной аппаратуры. Следует также отметить

28

применение кода Хэмминга в оперативных запоминающих устройствах (ОЗУ) ЭВМ.

Все известные методы повышения достоверности передачи дискретной информации нашли свое отражение в системах передачи без обратной связи и с обратной связью. Системы передачи без обратной связи используют симплексный канал связи и подразделяются на системы передачи простым кодом, системы с кодом, исправляющим ошибки, и системы с повторением передачи информации.

Для реализации систем с обратной связью требуется дуплексный канал связи (обратный и прямой). Они подразделяются на системы с обратной информационной связью и решающей обратной связью.

Контрольные вопросы

1.Понятие информационной избыточности и минимального кодового расстояния.

2.Равномерные коды.

3.Равновесные коды.

4.В чем достоинства и недостатки кодов с проверкой четности?

5.Особенности кодов с простым повторением.

6.Корреляционный код.

7.Код Хэмминга. Контроль и исправление одиночных ошибок.

8.Циклические коды. Области использования и особенности кодирования. Код ―2 из 5‖.

9.Как осуществляется контроль арифметических и логических опера-

ций?

10.В чем заключается принцип временной избыточности?

11.Как вы понимаете характеристики относительной избыточности R

икорректирующей способности К кодов?

12.Назовите области использования кодов с проверкой четности и кода Хэмминга.

13.В чем суть метода контроля арифметических операций по модулю?

14.Какие методы контроля логических операций Вы знаете?

15.Относительная избыточность и потенциальная эффективность ко-

дов.

29

3. АППАРАТНЫЕ СРЕДСТВА ОБНАРУЖЕНИЯ И ИСПРАВЛЕНИЯ ОШИБОК

3.1. Микросхема КР1818ВЖ1 и контроль передачи

Важнейшими устройствами современных ВС, определяющими надежность их работы и достоверность функционирования, являются устройства контроля и диагностики ошибок. Основным требованием для таких устройств, вследствие непрерывности процесса обнаружения ошибок, является минимальное влияние на производительность ЭВМ. Обычно функции диагностики ошибок возлагаются на быстродействующие аппаратные средства контроля, которые позволяют совместить во времени выполнение основных и контрольных операций./3,4/

Одним из наиболее простых и удобных кодов, позволяющих обнаруживать в передаваемой информации одиночные ошибки и ошибки высокой кратности, является циклический избыточный код. Данный код легко формируется при кодировании информации на основе регистра сдвига с обратными связями. Комбинация обратных связей выбирается такой, чтобы генерируемая последовательность двоичных символов являлась последовательностью максимальной длины. Для обнаружения ошибки с вероятностью Р=0,98 достаточно использовать для кодирования информации 16-разрядный сдвиговый регистр с обратными связями.

Микросхема КР1818ВЖ1 - устройство обнаружения ошибок (УОО) в информации, передаваемой по последовательным каналам передачи данных.

Структурная схема БИС КР1818ВЖ1 приведена на рис.3.1,а и состоит из следующих функциональных узлов: программируемой логической матрицы PLM, управляющей выбором одной из восьми конфигураций цепей обратной связи регистра сдвига RG; 16-разрядного сдвигового регистра RG, выполненного на основе элементов памяти, тактируемых фронтом сигнала и имеющих на входах схему «сумма по модулю 2», управляемую сигналами PLM; детектора ошибки DE; магистрали управления SE0 - SE2; входа DI; выхода DO; входа синхронизации SYN; входов установки, сброса и управления вводом данных S, R, COD; выхода ошибки ER.

Микросхема выполнена на основе маломощной транзисторнотранзисторной логики с диодами Шоттки (ТТЛШ) и содержит выходные ТТЛ буферные каскады с активным выходом и входные буферные каскады на основе p-n-p-транзистора со стандартными ТТЛ-уровнями сигнала.

Функционирование микросхемы основано на делении потока данных, который можно интерпретировать как бинарный полином H(X), на полином регистра сдвига P(X):

H(X) = Q(X)·P(X) + R(X),

где Q(X) - частное; R(X) - остаток, представляющий собой содержимое регистра после выполнения операции деления. Остаток R(X) является контрольной суммой при передаче данных. Вид полинома регистра сдвига P(X)

30

определяется конфигурацией цепей обратной связи, которая определяется кодом, подаваемым на магистраль управления SE0 - SE2.

SE0  SE1

SE1  SE2

SE2

COD

S

DI

DI

SYN  R

R

|

SYN |

|

PLM |

>0 |

|

DI,COD |

||

|

||

|

DO,ER |

|

|

S |

|

RG |

DO,ER |

|

|

R |

|

|

DO |

|

|

DO,ER |

|

DE |

ER |

|

|

a) |

b) |

Рис. 3.1. Структурная схема (а) и временная диаграмма работы (б) БИС К1818ВЖ1

Для микросхемы КР1818ВЖ1 возможен набор из восьми полиномов, представленный в табл. 3.1 для формирования контрольного кода. Поток данных вводится в микросхему в последовательной форме через вход DI по заднему фронту синхросигнала SYN при условии, что на вход COD подан высокий уровень сигнала. Низкий уровень сигнала на входе COD запрещает прием информации со входа DI, и содержимое регистра RG выдается на выход DO. Контроль содержимого регистра RG осуществляется по входе ER детектора ошибки.

|

|

|

Таблица 3.1 |

|

|

Набор функций, выполняемых БИС КР1818ВЖ1 |

|||

|

|

|

|

|

SE2 |

SE1 |

SE0 |

Полином |

|

0 |

0 |

0 |

X16 + X15 + X2 + 1 |

|

0 |

0 |

1 |

X16 + X14 + X + 1 |

|

0 |

1 |

0 |

X16 + X15 + X13 + X7 + X4 + X2 + X +1 |

|

0 |

1 |

1 |

X12 + X11 + X3 + X2 + X + 1 |

|

1 |

0 |

0 |

X8 + X7 + X5 + X4 + X + 1 |

|

1 |

0 |

1 |

X9 + 1 |

|

1 |

1 |

0 |

X16 + X12 + X5 + 1 |

|

1 |

1 |

1 |

X16 + X11 + X4 + 1 |

|