- •Список скорочень

- •1.Основні теоретичні відомості про лічильникові схеми

- •1.1 Визначення та класифікація лічильників

- •1.2 Способи організації перенесень між розрядами лічильника. Синхронні й асинхронні лічильники

- •1.3 Схеми асинхронних двійкових підсумовуючих і віднімаючих лічильників на синхронних і асинхронних тригерах

- •1.4 Двійково-десяткові коди і двійково-десяткові лічильники

- •1.5 Організація перенесень між десятковими розрядами в двійково- десяткових лічильниках

- •Синтез підсумовуючого синхронного десяткового лічильника з довільним порядком лічення, що працює в коді 4221

- •2.1 Побудова кодованої таблиці переходів синхронного лічильника

- •2.2 Побудова кодованої таблиці функцій збудження тригерів заданого типу

- •2.3 Одержання функцій збудження тригерів лічильника в досконалій формі

- •Спільна мінімізація функцій збудження підсумовуючого лічильника

- •Побудова схеми синхронного підсумовуючого лічильника

- •Синтез підсумовуючого асинхронного десяткового лічильника з довільним порядком лічення, що працює в коді 4221

- •3.1 Суть метода проектування асинхронного лічильника

- •3.2 Побудова часової діаграми роботи лічильника

- •3.3 Визначення по часовій діаграмі функцій синхронізації тригерів

- •3.4 Спрощення функцій керування асинхронного лічильника по функціях збудження синхронного лічильника

- •Синтез реверсивного синхронного десяткового лічильника, що працює в коді 4221

- •4.2 Побудова кодованої таблиці функцій збудження тригерів для рсЛч

- •4.3 Одержання функцій збудження тригерів лічильника в досконалій формі

- •Спільна мінімізація функцій збудження реверсивного лічильника

- •Список використаної літератури

Міністерство освіти і науки України

Київський коледж комп’ютерних технологій та економіки

Національного авіаційного університету

Випускова комісія спеціальності 123 «Комп’ютерна інженерія»

КУРСОВИЙ ПРОЕКТ

з Комп’ютерної схемотехніки

на тему «Синтез та дослідження схем лічильників з довільним модулем

та порядком лічення»

Студента 3 курсу групи

Галузь знань 12 «Інформаційні технології»

Спеціальності 123 «Комп’ютерна інженерія»

Керівник проекту -

Члени комісії _________ _________________

(прізвище та ініціали)

_________ _________________

(прізвище та ініціали)

_________ _________________

(прізвище та ініціали)

_________ Оцінка

Київ 20

Зміст

Зміст

Список скорочень 4

Вступ 5

Завдання на проектування 6

1.Основні теоретичні відомості про лічильникові схеми 8 1.1 Визначення та класифікація лічильників 8 1.2 Способи організації перенесень між розрядами лічильника.

Синхронні й асинхронні лічильники 10 1.3 Схеми асинхронних двійкових підсумовуючих і віднімаючих лічильників на синхронних і асинхронних тригерах 11 1.4 Двійково-десяткові коди і двійково-десяткові лічильники 14 1.5 Організація перенесень між десятковими розрядами в

двійково - десяткових лічильниках 16 2. Синтез підсумовуючого синхронного десяткового лічильника з довільним порядком лічення, що працює в коді 4221 18 2.1 Побудова кодованої таблиці переходів синхронного лічильника 19 2.2 Побудова кодованої таблиці функцій збудження тригерів заданого типу

20 2.3 Одержання функцій збудження тригерів лічильника в

досконалій формі 21 2.4 Спільна мінімізація функцій збудження підсумовуючого

лічильника 22 2.5 Побудова схеми синхронного підсумовуючого лічильника 22

3. Синтез підсумовуючого асинхронного десяткового лічильника з довільним порядком лічення, що працює в коді 4221 23 3.1 Суть метода проектування асинхронного лічильника 24 3.2 Побудова часової діаграми роботи лічильника 25

3.3 Визначення по часовій діаграмі функцій синхронізації тригерів 25 3.4 Спрощення функцій керування асинхронного лічильника по функціях збудження синхронного лічильника 26

3.5 Побудова схеми асинхронного лічильника 26

3.6 Налагодження роботи лічильника на лабораторному стенді, усунення

несправностей у роботі лічильника 26

4. Синтез реверсивного синхронного десяткового лічильника,

що працює в коді 4221 27 4.1 Побудова кодованої таблиці переходів реверсивного лічильника 27

4.2

Побудова кодованої таблиці функцій

збудження тригерів для

реверсивного

синхронного лічильника

27

4.3

Одержання функцій збудження тригерів

лічильника в досконалій

4.2

Побудова кодованої таблиці функцій

збудження тригерів для

реверсивного

синхронного лічильника

27

4.3

Одержання функцій збудження тригерів

лічильника в досконалій

формі 28 4.4 Спільна мінімізація функцій збудження реверсивного лічильника 29 4.5 Побудова часової діаграми роботи реверсивного синхронного лічильника 31

4.6 Побудова схеми реверсивного лічильника 31 Висновки 32

Список використаних джерел 33

Додатки 34

Додаток А - Схема принципова синхронного лічильника, що працює в коді 4221 35

Додаток Б - Схема принципова асинхронного лічильника, що працює в коді 4221 36

Додаток В - Схема принципова реверсивного лічильника,

що працює в коді 4221 37

Список скорочень

ЛЧ – лічильник

У0 - установка в нуль (скидання в нуль) У1 - установка в одиницю АЛЧ - асинхронний лічильник СЛЧ - синхронний лічильник РСЛЧ - реверсивний синхронний лічильник ВД - тимчасова діаграма ГІ - генератор імпульсів ГОІ - генератор одиночних імпульсів ДВ - діаграма Вейча ДДК - двійково-десятковий код ДЕ - десятковий еквівалент ДДНФ - досконала диз'юнктивна нормальна форма ДКНФ - досконала кон'юнктивна нормальна форма КТФЗ - кодована таблиця функцій збудження ЛЕ - логічний елемент ЛУ - логічна умова МДНФ - мінімальна диз'юнктивна нормальна форма ОФ - операторна форма СП - сигнал перенесення СЧ - система числення ТІ - таблиця істинності ТКСП - таблиця кодів сигналів перенесення ТФВ - таблиця функцій збудження УТП - умовна таблиця переходів ЕА - елементарний автомат (тригер)

ВСТУП

При

вивченні типових пристроїв цифрової

техніки важливе місце займають питання

експериментального дослідження їх

структури, архітектури, а також питання

автоматизованого логічного і схематичного

проектування визначених пристроїв на

рівні тригерів. Метою даного  курсового

проекту є робота, яка ознайомлює студента

зі способами організації базової логіки

ЕОМ, зі способами занесення, зберігання,

переведення і видачі машинного коду. В

даному випадку лише на переведенні

десяткового коду в заданий ДДК. Фактично

отримана в результаті схема повинна

відображати спільні концепції перетворення

чисел допустимих в розумінні людської

логіки в коди, які сприймає машина.

курсового

проекту є робота, яка ознайомлює студента

зі способами організації базової логіки

ЕОМ, зі способами занесення, зберігання,

переведення і видачі машинного коду. В

даному випадку лише на переведенні

десяткового коду в заданий ДДК. Фактично

отримана в результаті схема повинна

відображати спільні концепції перетворення

чисел допустимих в розумінні людської

логіки в коди, які сприймає машина.

Основні цілі, що переслідуються при виконанні студентами курсового проекту з дисципліни “Комп’ютерна схемотехніка”, полягають в наступному: закріпити, розширити і узагальнити теоретичні знання, отримані при вивченні теоретичної частини курсу; прищепити студентам навички роботи зі спеціальною технічною і довідковою літературою, а також ознайомити їх з основними вимогами ДЕСТ і стандартів ЄСКД; навчити студентів вибирати найбільш прийнятний варіант структурної, функціональної і принципової схем;

прищепити студентам навички, необхідні для виконання дипломного

проекту.

Метою даного курсового проекту є вивчення способів організації перенесень в лічильниках за допомогою синтезу і дослідження простого

синхронного лічильника з довільним модулем і порядком лічення, а також

синтезу і дослідження відповідного асинхронного і реверсивного лічильників, придбання навиків в збірці, наладці і експериментальному дослідженні різних схем лічильників.

Завдання

на проектування:

Завдання

на проектування:

Вивчити різноманітні схеми та засоби організації перенесень у

лічильниках;

2. Оволодіти методами синтезу синхронних, асинхронних та реверсивних

лічильників;

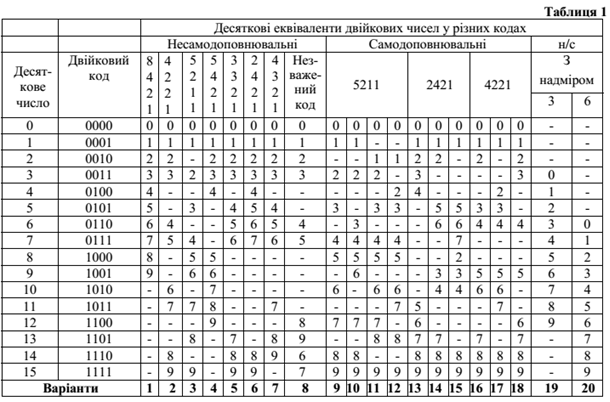

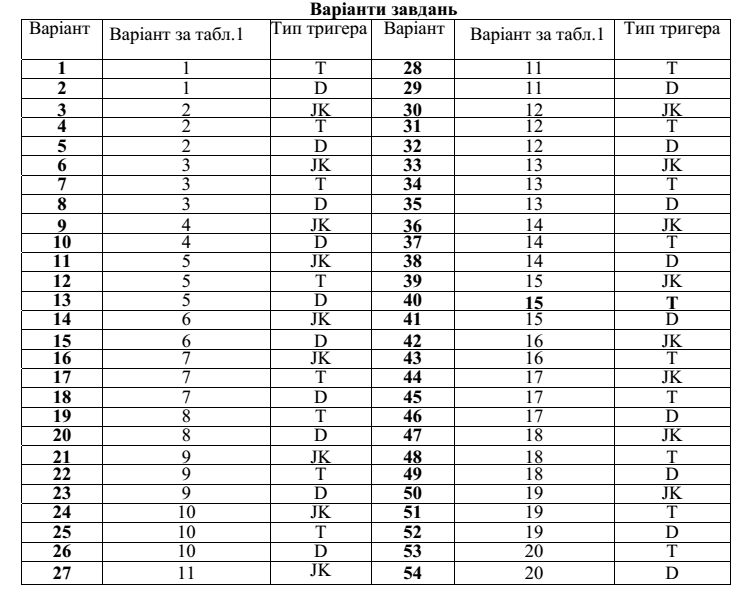

3. Набути навичок у складанні, налагодженні та експериментальному дослідженні різноманітних схем лічильників. Вихідні дані: Варіант завдання № 42; Номер коду 16 по таблиці 1 ;

Тип тригера – JK.

Таблиця

1

Таблиця

1