лабы / Metodicheskie_ukazania_k_Laboratornym_rabotam_ALTIUM_DESIGNER

.pdf

2. Сделайте видимым только слой Top Layer, удалите с него земляной полигон.

Откройте панель PCB, выберите режим Nets и

выберите класс LCD_DB[7..0], выделите все его цепи

(это можно сделать на панели PCB), удалите их.

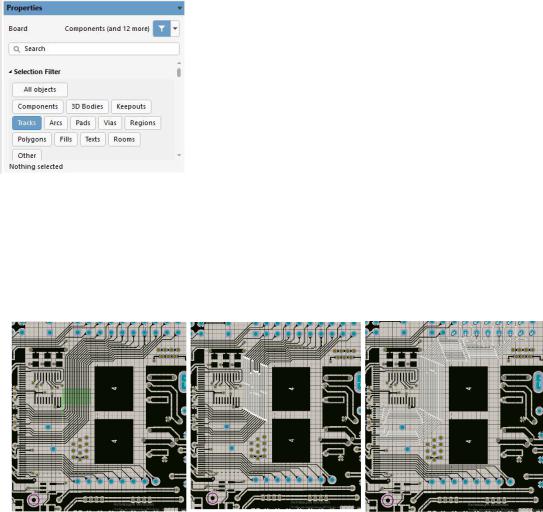

Теперь на панели Properties выберите во вкладке

Selection Filter только объекты Tracks (рис.7.1).

Рис.7.1.

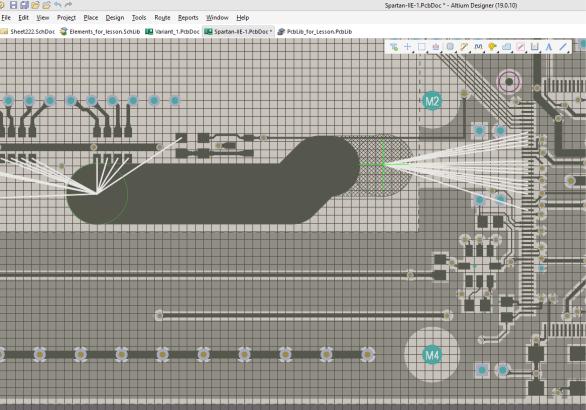

3. Найдите на плате цепи HB5…HB15, двигая мышь справа налево, выделите зелёным прямоугольником сегменты этих цепей; однократно нажав клавишу Tab

выделите цепи целиком и удалите их (рис.7.2). Теперь плата готова к повторной трассировке.

Рис.7.2.

4. Откройте панель PCB ActiveRoute (все панели открываются в нижней правой части экрана). На панели укажите слой трассировки Top Layer, на плате выделите по одному контакту каждой из цепей класса LCD_DB[7..0], предварительно перенастроив фильтр отбора на все объекты. На панели ActiveRoute выберите пункт

Route Guide и укажите примерный путь, где вы планируете проложить трассы

(рис.7.3). Первую точку пути укажите недалеко от начала группы цепей,

а последнюю – немного не доходя до конечной цели. В результате получится следующая схема.

71

Рис.7.3.

5.Нажмите кнопку ActiveRoute или комбинацию клавиш Shift+A, тогда цепи автоматически страссируются. Используя панель PCB ActiveRoute, можно оперативно менять правила трассировки для выбранных цепей (их ширину и зазор между ними).

6.Аналогичным способом трассируйте цепи HB5…HB15.

7.Сохраните полученный файл топологии на диске под новым именем.

8.Снова удалите цепи HB5…HB15 и попытайтесь трассировать их в режиме

Interactive Multi-Routing. Обратите внимание на отличие результатов трассировки.

Этот файл тоже сохраните, но уже под другим именем.

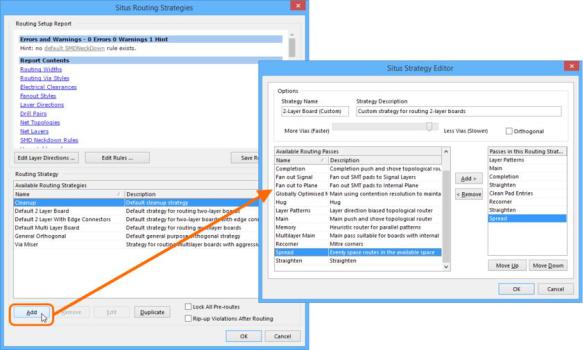

9. Снова удалите цепи HB5…HB15 и цепи класса LCD_DB[7..0]. Настройте автотрассировщик и запустите автоматическую трассировку удалённых ранее цепей.

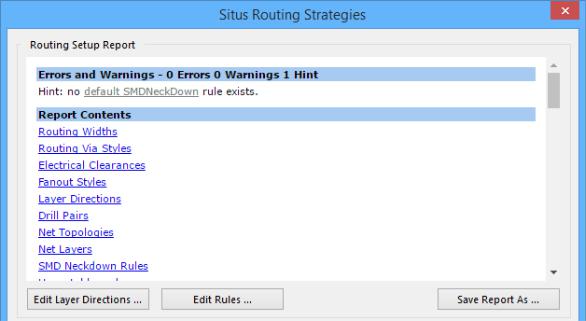

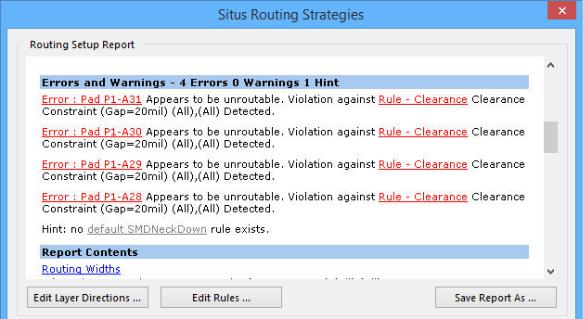

Для этого заблокируйте уже страссированные цепи с помощью параметра Lock All Pre-routes в диалоговом окне Situs Routing Strategies. В этом же окне укажите направления трассировки для слоёв во вкладке Layer Directions. Проверка правил

72

проектирования (DRC) перед запуском автотрассировки является паиболее важным шагом. Команда Situs проводит собственный предварительный анализ и представляет его результаты в виде отчета в диалоговом окне Situs Routing Strategies, при использовании команд Route\Auto Route \Setup или Route\Auto Route\All.

Рис.7.4.

Отчет включает в себя следующую информацию (рис.7.4):

правила проектирования, определённые в проекте, которые будут использоваться автотрассировщиком, и количество объектов, на которые действует каждое правило: цепи, компоненты, контактные площадки;

направления трассировки, определённые для всех сигнальных слоёв;

определения пар сверловки.

В отчёте отображается список потенциальных проблем, которые могут повлиять на эффективность трассировки. Там, где возможно, будут предоставлены подсказки для лучшей подготовки проекта к автотрассировке.

Перед запуском трассировки внимательно изучите все ошибки, предупреждения,

подсказки и при необходимости внесите соответствующие изменения в правила проектирования. Перед запуском автотрассировки важно исправить все нарушения правил проектирования, относящихся к трассировке. Они могут не только помешать трассировке в месте нарушения, но и значительно замедлить процесс из-за

73

постоянных попыток автотрассировщика провести трассировку в неисправной области.

Рис.7.5.

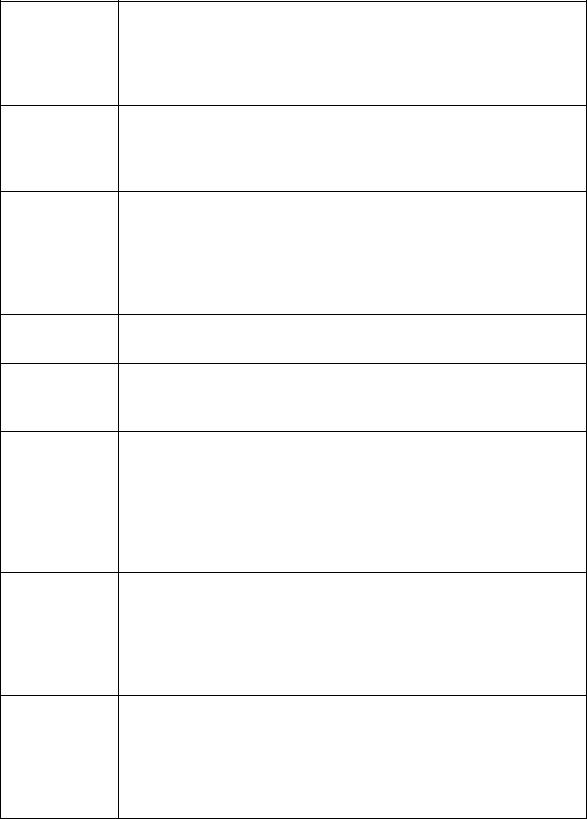

Советы по запуску трассировщика:

команды автотрассировщика находятся в меню Route\Auto Route (рис.7.5);

команды Route\Auto Route\All и Route\Auto Route\Setup открывают диалоговое окно Situs Routing Strategies; разница между ними состоит в том, что при выборе команды All диалоговое окно будет включать в себя кнопку Route All

(трассировать всё);

не бойтесь экспериментировать. Если результат неприемлем, измените подход трассировщика. Добавьте промежуточные проходы очистки и выравнивания, оставьте больше пространства вокруг плотных областей или измените направления слоёв;

экспериментируя с трассировщиком, создавая собственные стратегии для управления порядком проходов, изменения количества переходных отверстий, смены направлений трассировки, ограничения трассировки только ортогональными трассами и т.д., делайте заметки о комбинациях, которые вы пробуете. Таким образом вы сможете найти и повторно использовать конфигурации, которые наилучшим образом работают с вашими проектами;

74

отдельно запустите процесс создания «фэнаута» и оцените качество результата. Возможно, понадобится вручную создать «фэнауты» в проблемных областях.

Определённые на данный момент стратегии трассировки приведены в нижней части окна Situs Routing Strategies. Нажмите кнопку Add, чтобы открыть вкладку

Situs Strategy Editor, в которой можно указать проходы для их включения в новую стратегию (рис.7.6).

Рис.7.6.

Стратегии, определённые пользователем, можно отредактировать в любой момент, в отличие от стратегий по умолчанию, которые изменить нельзя: Cleanup,

Default 2 Layer Board, Default 2 Layer With Edge Connectors, Default Multi Layer

Board, General Orthogonal, Via Miser.

Доступны следующие проходы трассировки (табл.7.1), их можно использовать в любом порядке. В качестве руководства изучите существующую стратегию и её порядок проходов.

75

Таблица 7.1.

Наименование |

Описание прохода |

|

|||

|

|

|

|

||

Adjacent |

Проход трассировки на |

уровне |

соединений. Используется для |

||

трассировки соседних выводов одной цепи, требующих создания |

|||||

Memory |

|||||

«фэнаута», простым U-образным шаблоном |

|

||||

|

|

||||

|

|

||||

|

Проход трассировки на уровне соединений. Повторно трассирует |

||||

Clean |

от центра каждой контактной площадки вдоль её наиболее длинной |

||||

оси. Если в проекте есть компоненты с контактными площадками |

|||||

Pad Entries |

|||||

разных размеров по осям X и Y, то всегда включайте проход Clean |

|||||

|

|||||

|

Pad Entries после прохода Memory |

|

|||

|

|

||||

|

Проход трассировки на уровне соединений. По сути аналогичен |

||||

|

проходу Main, с разницей в стоимости разрешения конфликтов и |

||||

Completion |

завершения сложных соединений. Примеры разницы в стоимости: |

||||

переходные отверстия оцениваются как более «дешёвые», |

|||||

|

|||||

|

неправильно проложенные трассы оцениваются как |

более |

|||

|

«дорогие» |

|

|

|

|

|

|

||||

|

Проход трассировки на уровне компонентов, основанный на |

||||

|

настройках, определённых правилом Fanout Control. Проверяет |

||||

|

шаблоны расположения контактных площадок, учитывает зазоры, |

||||

Fanout Signal |

ширину трассировки и стиль переходных отверстий, затем |

||||

|

выбирает подходящий стиль расположения «фэнаутов» (линейно, |

||||

|

в шахматном порядке и т.д.) в соответствии с требованиями в |

||||

|

правиле. «Фэнауты» переходят только на сигнальные слои |

|

|||

|

|

||||

|

Проход трассировки на уровне компонентов, основанный на |

||||

|

настройках, определённых правилом Fanout Control. Проверяет |

||||

|

шаблоны расположения контактных площадок, учитывает зазоры, |

||||

Fanout to Plane |

ширину трассировки и |

стиль |

переходных отверстий, |

затем |

|

выбирает подходящий стиль расположения «фэнаутов» (линейно, |

|||||

|

|||||

|

в шахматном порядке и т.д.) в соответствии с требованиями в |

||||

|

правиле. «Фэнауты» переходят только на внутренние экранные |

||||

|

слои |

|

|

|

|

Проход трассировки на уровне соединений. Обеспечивает оптимальную трассировку. Игнорирует конфликты и нарушения на первой итерации. Затем повторно трассирует соединения, с

Globally повышением стоимости конфликтов, пока нарушений не Optimized Main останется. Этот проход, в сочетании с включённым параметром Orthogonal, может обеспечить аккуратно трассированные шаблоны. Добавьте в стратегию проход Recorner для создания

скошенных изломов

76

Продолжение таблицы 7.1.

Проход трассировки на уровне соединений, который повторно трассирует каждое соединение, следуя существующим трассам с Hug минимально возможным зазором. Этот проход используется для максимального увеличения свободного для трассировки

пространства. Этот проход работает очень медленно

Layer Patterns Проход трассировки на уровне соединений. Трассирует только соединения, соответствующие направлению слоя (в пределах допуска). Использует высокую стоимость огибания и следования существующей трассировки для максимизации пространства

Main Проход трассировки на уровне соединений. Использует топологическое распределение для поиска пути трассировки, затем

– «расталкивание» трассировки для преобразования пути в трассу. В стратегии трассировки должен присутствовать только один проход типа «Main»: Main, Multilayer Main или Globally Optimized

Main

Memory Проход трассировки на уровне соединений. Ищет два вывода разны омпонентов на одном слое с одной координатой X или Y

Multilayer Main Проход трассировки на уровне соединений. Аналогичен проходу Main, но со стоимостью, оптимизированной для многослойных плат

Recorner Проход трассировки на уровне соединений. Используется для создания скосов у изломов трасс. Этот проход нужен, если в стратегии включен параметр Orthogonal, по сути, переопределяя его и скашивая изломы каждой трассы. Если параметр Orthogonal отключён в используемой стратегии, то нет необходимости добавлять проход Recorner, поскольку автотрассировщик добавляет скосы по умолчанию

Spread Проход трассировки на уровне соединений. Повторно трассирует каждое соединение, пытаясь равномерно распределить трассировку для использования всего свободного пространства и провести трассировку на равных расстояниях при проходе между фиксированными объектами (такими, как контактные площадки компонентов). Этот проход работает очень медленно

Straighten Проход трассировки на уровне соединений. Пытается сократить число изломов. Следует вдоль трассы до излома, затем выполняет поиск другой точки трассировки цепи в горизонтальном, вертикальном, в +45 , в 45 . направлении. Если эта точка будет найдена, то происходит проверка: уменьшает ли новый путь длину трассировки

77

10. В случае неудовлетворительного результата трассировки самостоятельно проанализируйте причины неудач и откорректируйте режимы работы трассировщика.

Сохраните ещё один вариант топологии платы. Сравните результаты трассировки одних и тех же цепей разными способами.

11. Предъявите преподавателю три варианта топологии платы, полученные активной интерактивной трассировкой, групповой интерактивной трассировкой и автотрассировкой, ответьте на контрольные вопросы.

Контрольные вопросы

1. Что представляет собой активная трассировка? Опишите принцип её работы,

её достоинства и недостатки.

2.Что представляет собой режим Interactive Multi-routing? Опишите принцип его работы, его достоинства и недостатки.

3.На какие основные типы по принципу работы можно разделить автотрассировщики печатных плат? Опишите принципы их работы.

4.К какому типу относится автотрассировщик, входящий в состав пакета Altium Designer 19? Опишите его достоинства и недостатки.

5.Какие функции выполняет процедура Route Guide?

6.Какие параметры трассировки можно менять во время работы в режиме

ActiveRoute?

7.Можно ли автотрассировщику запретить или разрешить трассировку только

вкаком-то одном слое?

8.Какие этапы (фазы) трассировки можно применять при автотрассировке?

9.В каких случаях наиболее эффективны те или иные методы трассировки.

10.Можно ли с помощью автотрассировки получить такую топологию платы,

вкоторой в одной и той же цепи будут присутствовать переходные отверстия разных типов, и ширина проводников также будет отличаться на разных участках цепи?

78

Лабораторная работа № 8 Оптимизация топологии

Цель работы: изучение методов оптимизации топологии печатной платы перед передачей её на изготовление. Изучение инструментов оптимизации топологии.

Изучение требований к топологии при подготовке плат к серийному изготовлению

и автоматизированной сборке.

Продолжительность работы: 4 часа.

Задание: создать полностью готовую к производству топологию печатной платы.

Ожидаемый результат: электрические схемы устройства, выполненные |

в |

соответствии с требованиями стандартов ЕСКД и IPC и готовые для передачи |

в |

топологический редактор.

Защита работы: предъявить на экране компьютера готовую топологию платы,

ответить на контрольные вопросы.

Теоретические сведения

В процессе проектирования печатной платы, как правило элементы топологии неоднократно перемещаются на ней, электрические связи также перемещаются

иперетрассируются. Когда, наконец, все элементы размещены по своим местам,

ивсе электрические соединения созданы, кажется, что вся работа выполнена, однако,

это не так. Необходимо произвести оптимизацию полученной топологии.

У неё две основных цели: улучшение параметров изделия (электрических,

механических, надёжностных) и облегчение процесса изготовления изделия, так называемое DFM (Design for Manufacturability) проектирование.

Для улучшения параметров разработанного изделия на этапе оптимизации производят следующие действия:

сглаживают электрические цепи, т.е. уменьшают число изломов и переходных отверстий, суммарную длину проводников, убирают петли и «антенны»;

расширяют по возможности цепи питания и сильноточные цепи;

заливают металлическими областями (полигонами) свободные участки платы;

79

осуществляют электрическое экранирование областей и отдельных цепей на печатной плате;

создают каплевидные контактные площадки для уменьшения отражения сигналов и повышения технологичности изготовления.

Для облегчения изготовления и сборки печатной платы производят следующие

действия:

модифицируют топологический рисунок платы таким образом, чтобы сократить число узких мест, т.е. мест, где обнаруживаются минимально допустимые технологические зазоры или минимально допустимая ширина проводника и т.д.;

размещают на плате дополнительные надписи и обозначения;

размещают на плате реперные знаки, т.е. знаки, необходимые автоматическим устройствам для точного позиционирования на плате при установке элементов;

убирают неиспользуемые контактные площадки во внутренних слоях около отверстий.

Лабораторное задание

1.Загрузите ваш проект и откройте топологию платы.

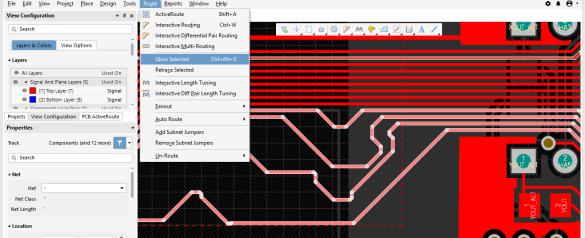

2.Выделите группу цепей на плате любым известным вам способом. Для сглаживания топологии электрических цепей выберите из верхнего меню команду

Route\Gloss selected или нажмите комбинацию клавиш Ctrl+Alt+G.

Рис.8.1.

80