- •Лекция 1 – Полупроводники. Собственная и примесная проводимости полупроводников.

- •Часть 1. Полупроводники

- •Часть 2. Собственная проводимость полупроводников

- •Часть 3. Примесная проводимость полупроводников

- •Лекция 2 Полупроводниковые диоды

- •Общие сведения

- •Прямое включение p-n перехода

- •Обратное включение p-n перехода

- •Вольтамперная характеристика p-n перехода

- •Барьерная ёмкость p-n перехода

- •Пробой p-n перехода

- •Разновидности диодов

- •Лекция 4. Полевой транзистор.

- •Общие сведения.

- •Классификация:

- •Полевые транзисторы с управляющие p-n-переходом

- •Лекция №5. Полупроводниковые выпрямители.

- •Лекция 6. Тиристоры

- •7 Лекция Полупроводниковые управляемые выпрямители

- •Однофазный двухполупериодный управляемый выпрямитель

- •Трёхфазный двухполупериодный управляемый выпрямитель

- •Трёхфазный двухполупериодный управляемый выпрямитель

- •8 Лекция Операционные усилители Общие сведения

- •Общие сведения

- •Общие сведения

- •Основные характеристики и параметры оу

- •Основные характеристики оу

- •Основные характеристики оу

- •Основные характеристики оу

- •Основные характеристики оу

- •Основные параметры оу

- •Основные параметры оу

- •Основные параметры оу

- •Классификация оу

- •Применение операционных усилителей

- •10 Лекция Операционный усилитель (часть 3) Применение оу. Компараторы. Мультивибраторы

- •Лекция 12. Алгебра логики. Приоритет логических операций. Таблица истинности. Законы алгебры логики. Логические связи. Синтез логических схем.

- •Приоритет логических операций и таблицы истинности:

- •Операция Инверсия (отрицания)

- •Операция Конъюнкция (логического умножения)

- •Операция Дизъюнкция (логического сложения)

- •Логическая связь не (логическое отрицание)

- •Логическая связь или – сложение (дизъюнкция) высказываний

- •Логическая связь и (конъюнкция высказываний)

- •Логическая связь отрицание дизъюнкции (операция Пирса)

- •Логическая связь отрицание конъюнкции (операция Шеффера)

- •Логическая связь отрицание равнозначности (операция или-или)

- •Импликация

- •Логическая равнозначность (эквивалентность)

- •Синтез логических схем

- •14 Лекция. Триггеры. Цифровые устройства. Логистические устройства.

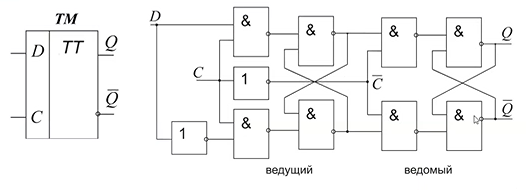

- •Двухступенчатый d-триггер

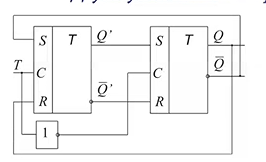

- •Двухступенчатый т-триггер (асинхронный)

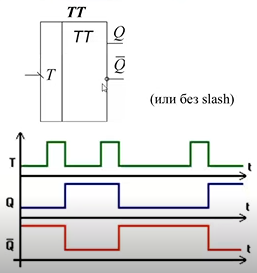

- •Синхронный т-триггер

- •Синхронный jk-триггер

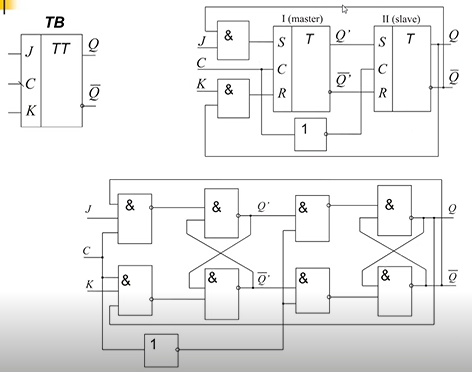

- •Двухступенчатый jk-триггер.

Двухступенчатый d-триггер

При последовательном соединении двух D-триггеров пропадает их прозрачность для входного сигнала. Для передачи входных сигналов на выход схемы триггеры тактируются взаимно дополняющей парой синхросигналов, как в случае синхронного RS-триггера. Выходной сигнал ведущего D-триггера Q повторяет входной сигнал до тех пор, пока сигнал С=1. В это время ведомый триггер остаётся закрытым. Как только сигнал С становится равным 0, первый D-триггер запирается и выходной сигнал второго триггера Q повторяет сигнал на выходе ведущего триггера Q'.

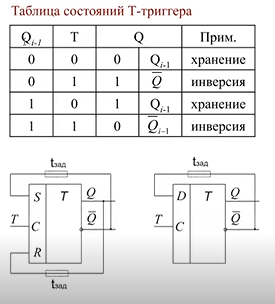

Т-триггер

Т-триггер или счётный триггер, изменяет своё состояние на противоположное по каждому активному логическому сигналу на информационном входе Т.

Р еализация

данного режима работы с использованием

простейшего элемента памяти требует

подачи на последний для каждого

последующего переключения инверсных

значений входных сигналов. Такой режим

обеспечивается введением в RS-

или D-триггер цепей

дополнительной обратной связи.

еализация

данного режима работы с использованием

простейшего элемента памяти требует

подачи на последний для каждого

последующего переключения инверсных

значений входных сигналов. Такой режим

обеспечивается введением в RS-

или D-триггер цепей

дополнительной обратной связи.

Однако, используя только один RS- или D-триггер реализовать Т-триггер невозможно, так как тогда он должен быть одновременно и источником информации, и её приёмником. Приём новой информации автоматически означает потерю старой, даже если вводится звено задержки.

Для получения надёжного Т-триггера необходимо либо использовать дополнительный элемент памяти, запоминающий новые значения сигналов R, S или D и подающий их на информационные входы основного элемента памяти только после снятия активного сигнала со входа Т, либо искусственно ограничивать длительность сигнала Т.

Двухступенчатый т-триггер (асинхронный)

Принцип работы ничем не отличается от двухступенчатых RS- и D-триггеров.

Новая информация формируется сначала на выходе ведущего триггера при сохранении старой информации в ведомом. Когда новое состояние на выходе ведущего сформировано и снят активный уровень сигнала Т, происходит её перезапись в ведомый триггер.

Синхронный т-триггер

Используется крайне редко. Как правило строится на основе триггера с динамическим управлением. Изменение выходного сигнала происходит только когда изменение входного сигнала синхронизировано с чем-то. То есть будет изменяться сигнал, когда на вход С подана логическая 1, и при этом на Т вход тоже подана 1.

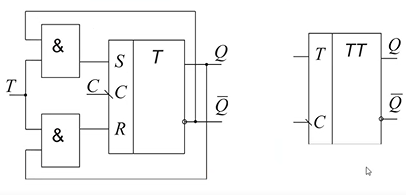

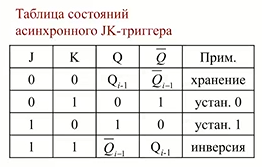

JK-триггер.

Очень похож на RS-триггер. Но в отличие от него JK-триггер не имеет запрещённых комбинаций входных сигналов.

JK-триггер может быть одноступенчатым и двухступенчатым, со статическим и динамическим переключением.

Логическое

выражение для асинхронного JK-триггера:

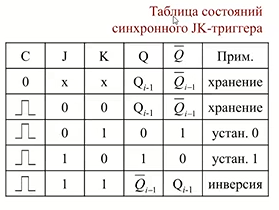

Обычно JK-триггеры делаются синхронными.

Логическое выражение для синхронного JK-триггера:

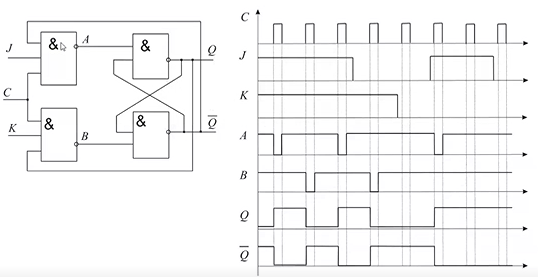

Синхронный jk-триггер

Импульсы С должны быть достаточно короткими, чтобы исключить повторное срабатывание триггера. Поэтому JK-триггеры делаются двухступенчатыми или с динамическими входами.

Двухступенчатый jk-триггер.

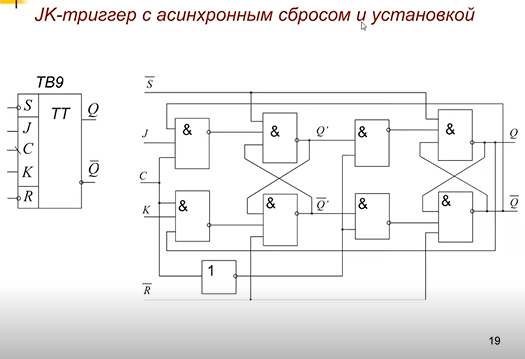

Ниже JK-триггер с асинхронным сбросом и установкой. Имеется больше входов.

Особенности эксплуатации синхронных триггеров со статическим управлением:

Во время действия тактового импульса С состояния управляющих входов RS, D, или JK не должны меняться. В противном случае может произойти ложное срабатывание.

Проблемы:

1) Проскок помехи – при неизменных состояниях входа на управляющих входа RS, D, JK состояние на выходе триггера изменяется сразу после прихода помехи. Триггер срабатывает без нашего ведома.

2) Захват помехи – при неизменных состояниях входа на управляющих входа RS, D, JK состояние на выходе триггера изменяется по тактовому импульсу.