- •Лабораторная работа интегральные логические элементы

- •Подготовка к работе

- •Рабочее задание

- •1. Реализация функции не (инверсии)

- •2. Реализация функции и (конъюнкции)

- •3. Реализация 3-х входовой схемы и

- •Рабочее задание

- •1. Реализация функции полусумматора

- •2. Реализация функции сравнения (цифрового компаратора)

- •3. Реализация функции дешифратора (декодера)

Рабочее задание

1. Реализация функции полусумматора

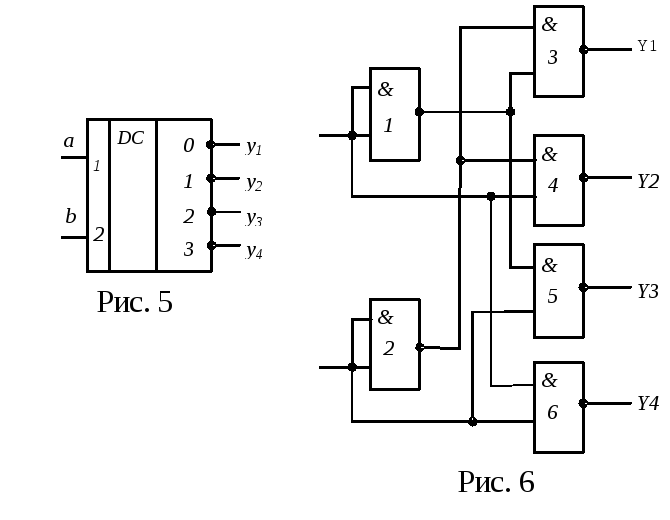

Полусумматор – это узел, имеющий два входа и два выхода и выполняющий операцию арифметического сложения двух одноразрядных чисел a и b. Выход p ‑ сигнал переноса.

Условное графическое обозначение

элемента показано на рис. 1. На наборном

поле собрать схему согласно рис. 2. Выходы

s и pсоединить с любыми гнездами индикатора

на вспомогательном устройстве. Свечение

светодиода свидетельствует о наличии

на выходе сигнала логической ”1”.

Подключая входы“a”и “b” к гнездам “0”

и “1” на вспомогательном устройстве,

подать на входы следующие комбинации

сигналов![]()

Все значения входных и выходных сигналов занести в таблицу истинности 1.

|

a |

b |

s |

p |

|

|

|

|

|

Таблица 1

Написать аналитическое выражение для s и p и составить временную диаграмму работы.

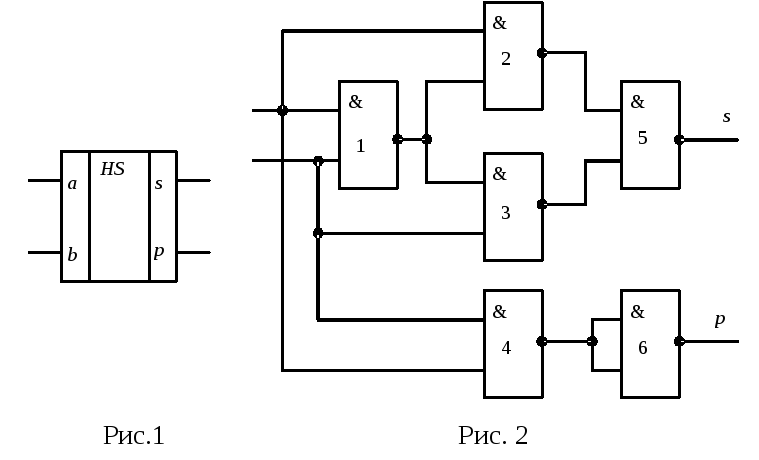

2. Реализация функции сравнения (цифрового компаратора)

Сравнивающее устройство –

узел, имеющий два входа и три выхода и

выполняющий операцию сравнения двух

одноразрядных чисел a

и b.

Условное графическое изображение

показано на рис. 3. На лабораторном поле

собрать схему согласно рис. 4. Выходы

![]() соединить с любыми гнездами индикатора

на вспомогательном блоке. Свечение

светодиода свидетельствует о наличии

на выходе сигнала логической “1”.

Подключая входы “a”

и “b”

к гнездам “0” и “1” на вспомогательном

устройстве, подать на входы следующие

комбинации сигналов

соединить с любыми гнездами индикатора

на вспомогательном блоке. Свечение

светодиода свидетельствует о наличии

на выходе сигнала логической “1”.

Подключая входы “a”

и “b”

к гнездам “0” и “1” на вспомогательном

устройстве, подать на входы следующие

комбинации сигналов

![]()

Все значения входных и выходных сигналов занести в таблицу истинности 2.

|

a |

b |

a>b |

a=b |

a<b |

|

|

|

|

|

|

Таблица 2

Написать аналитическое

выражение для

![]() и

составить временную диаграмму работы.

и

составить временную диаграмму работы.

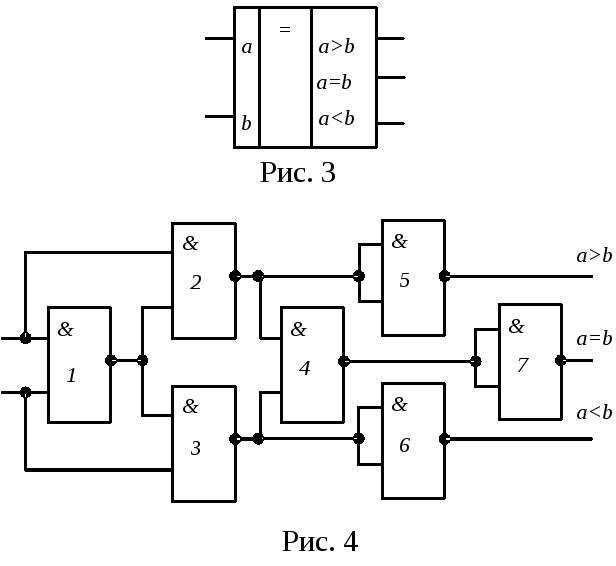

3. Реализация функции дешифратора (декодера)

Дешифратор – цифровой узел, выполняющий операцию преобразования m элементов входного кода в сигнал “1” (дешифратор высокого уровня), либо в сигнал “0” (дешифратор низкого уровня) на одном из выходов.

Условное графическое

обозначение дешифратора с двумя входами

и четырьмя выходами показано на рис. 5

(дешифратор низкого уровня). На наборном

поле собрать схему согласно рис. 6. Выходы

Y1,Y2,Y3,Y4

соединить с любыми гнездами индикатора

на вспомогательном устройстве. Свечение

светодиода свидетельствует о наличии

на выходе сигнала логической “1”.

Подключая входы “a”

и “b”

к гнездам “0” и “1” на вспомогательном

устройстве, подать на входы следующие

комбинации сигналов:

![]()

![]() .

Все значения входных и выходных сигналов

занести в таблицу истинности 3.

.

Все значения входных и выходных сигналов

занести в таблицу истинности 3.

Таблица 3

|

a |

b |

Y1 |

Y2 |

Y3 |

Y4 |

|

|

|

|

|

|

|

Написать аналитическое

выражение для функции

![]() где

где

![]() Построить временную диаграмму работы

дешифратора.

Построить временную диаграмму работы

дешифратора.