- •Contents

- •1.2 Overview of Volume 2A and 2B: Instruction Set Reference

- •1.3 Notational Conventions

- •1.3.1 Bit and Byte Order

- •1.3.2 Reserved Bits and Software Compatibility

- •1.3.3 Instruction Operands

- •1.3.4 Hexadecimal and Binary Numbers

- •1.3.5 Segmented Addressing

- •1.3.6 Exceptions

- •1.3.7 A New Syntax for CPUID, CR, and MSR Values

- •1.4 Related Literature

- •2.1.1 Instruction Prefixes

- •2.1.2 Opcodes

- •2.1.3 ModR/M and SIB Bytes

- •2.1.4 Displacement and Immediate Bytes

- •2.2.1 REX Prefixes

- •2.2.1.1 Encoding

- •2.2.1.2 More on REX Prefix Fields

- •2.2.1.3 Displacement

- •2.2.1.5 Immediates

- •2.2.2 Additional Encodings for Control and Debug Registers

- •3.1 Interpreting the Instruction Reference Pages

- •3.1.1 Instruction Format

- •3.1.1.1 Opcode Column in the Instruction Summary Table

- •3.1.1.2 Instruction Column in the Opcode Summary Table

- •3.1.1.4 Compatibility/Legacy Mode Column in the Instruction Summary Table

- •3.1.1.5 Description Column in the Instruction Summary Table

- •3.1.1.6 Description Section

- •3.1.1.7 Operation Section

- •3.1.1.9 Flags Affected Section

- •3.1.1.10 FPU Flags Affected Section

- •3.1.1.11 Protected Mode Exceptions Section

- •3.1.1.14 Floating-Point Exceptions Section

- •3.1.1.16 Compatibility Mode Exceptions Section

- •Intel Sales Offices

ABOUT THIS MANUAL

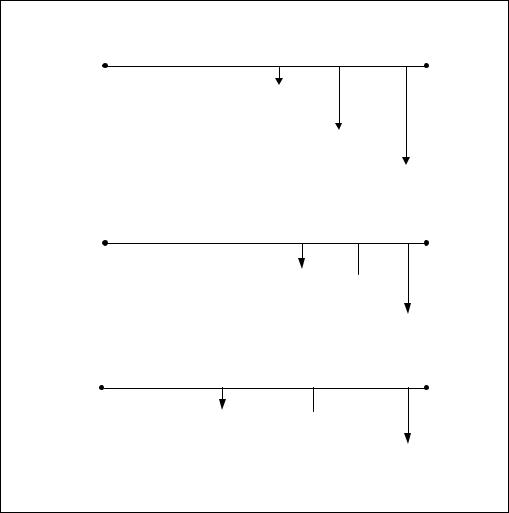

&38,' ,QSXW DQG 2XWSXW

&38,' + (&; 66( >ELW @

6RPH LQSXWV UHTXLUH YDOXHV LQ ($; DQG (&; 7KLV LV UHSUHVHQWHG DV &38,' ($; Q (&; Q ,I RQO\ RQH YDOXH LV SUHVHQW ($; LV LPSOLHG

2XWSXW UHJLVWHU DQG IHDWXUH IODJ RU ILHOG

QDPH ZLWK ELW SRVLWLRQ V

9DOXH RU UDQJH RI RXWSXW

&RQWURO 5HJLVWHU 9DOXHV

&5 26);65>ELW @

([DPSOH &5 QDPH  )HDWXUH IODJ RU ILHOG QDPH

)HDWXUH IODJ RU ILHOG QDPH

ZLWK ELW SRVLWLRQ V

9DOXH RU UDQJH RI RXWSXW

0RGHO 6SHFLILF 5HJLVWHU 9DOXHV

,$B0,6&B(1$%/(6 (1$%/()23&2'(>ELW @

([DPSOH 065 QDPH  )HDWXUH IODJ RU ILHOG QDPH ZLWK ELW SRVLWLRQ V

)HDWXUH IODJ RU ILHOG QDPH ZLWK ELW SRVLWLRQ V

9DOXH RU UDQJH RI RXWSXW

20

Figure 1-2. Syntax for CPUID, CR, and MSR Data Presentation

1.4RELATED LITERATURE

Literature related to Intel 64 and IA-32 processors is listed on-line at: http://developer.intel.com/products/processor/index.htm

Some of the documents listed at this web site can be viewed on-line; others can be ordered. The literature available is listed by Intel processor and then by the following literature types: applications notes, data sheets, manuals, papers, and specification updates.

Vol. 2 1-7

ABOUT THIS MANUAL

See also:

•The data sheet for a particular Intel 64 or IA-32 processor

•The specification update for a particular Intel 64 or IA-32 processor

•Intel® C++ Compiler documentation and online help http://www3.intel.com/cd/software/products/asmo-na/eng/index.htm

•Intel® Fortran Compiler documentation and online help http://www3.intel.com/cd/software/products/asmo-na/eng/index.htm

•Intel® VTune™ Performance Analyzer documentation and online help http://www3.intel.com/cd/software/products/asmo-na/eng/index.htm

•Intel® 64 and IA-32 Architectures Software Developer’s Manual (in five volumes) http://developer.intel.com/products/processor/manuals/index.htm

•Intel® 64 and IA-32 Architectures Optimization Reference Manual http://developer.intel.com/products/processor/manuals/index.htm

•Intel® Processor Identification with the CPUID Instruction, AP-485 http://www.intel.com/support/processors/sb/cs-009861.htm

•Developing Multi-threaded Applications: A Platform Consistent Approach http://cache-www.intel.com/cd/00/00/05/15/51534_developing_multithreaded _applications.pdf

•Using Spin-Loops on Intel Pentium 4 Processor and Intel Xeon Processor MP http://www3.intel.com/cd/ids/developer/asmona/eng/dc/threading/knowledgebase/19083.htm

More relevant links are:

•Software network link: http://softwarecommunity.intel.com/isn/home/

•Developer centers: http://www3.intel.com/cd/ids/developer/asmo-na/eng/dc/index.htm

•Processor support general link: http://www.intel.com/support/processors/

•Software products and packages: http://www3.intel.com/cd/software/products/asmo-na/eng/index.htm

•Hyper-Threading Technology (HT Technology): http://developer.intel.com/technology/hyperthread/

1-8 Vol. 2

CHAPTER 2

INSTRUCTION FORMAT

This chapter describes the instruction format for all Intel 64 and IA-32 processors. The instruction format for protected mode, real-address mode and virtual-8086 mode is described in Section 2.1. Increments provided for IA-32e mode and its submodes are described in Section 2.2.

2.1INSTRUCTION FORMAT FOR PROTECTED MODE, REAL-ADDRESS MODE, AND VIRTUAL-8086 MODE

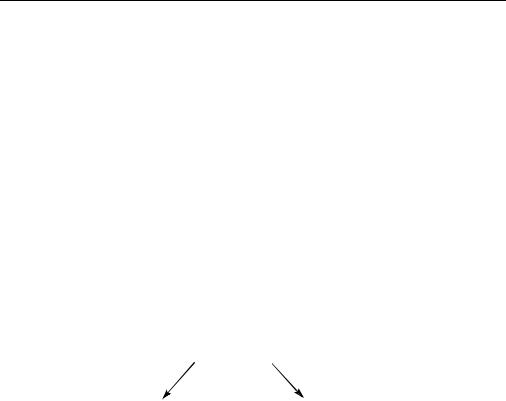

The Intel 64 and IA-32 architectures instruction encodings are subsets of the format shown in Figure 2-1. Instructions consist of optional instruction prefixes (in any order), primary opcode bytes (up to three bytes), an addressing-form specifier (if required) consisting of the ModR/M byte and sometimes the SIB (Scale-Index-Base) byte, a displacement (if required), and an immediate data field (if required).

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Instruction |

|

|

Opcode |

|

|

ModR/M |

|

|

|

SIB |

|

Displacement |

Immediate |

|

|||||||

|

Prefixes |

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

Up to four |

1-, 2-, or 3-byte 1 byte |

|

1 byte |

|

|

|

Address |

|

|

Immediate |

|

||||||||||

|

prefixes of |

opcode |

(if required) |

(if required) |

displacement |

data of |

|

|||||||||||||||

|

1 byte each |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

of 1, 2, or 4 |

1, 2, or 4 |

|

|||

|

(optional) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

bytes or none |

bytes or none |

|

|||

|

|

7 |

|

6 5 |

|

3 2 |

0 |

7 |

6 5 |

|

3 2 |

0 |

|

|

|

|||||||

|

|

|

|

Mod |

|

Reg/ |

|

R/M |

|

|

|

Scale |

|

Index |

|

Base |

|

|

|

|

||

|

|

|

|

|

Opcode |

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Figure 2-1. Intel 64 and IA-32 Architectures Instruction Format

Vol. 2 2-1

INSTRUCTION FORMAT

2.1.1Instruction Prefixes

Instruction prefixes are divided into four groups, each with a set of allowable prefix codes. For each instruction, one prefix may be used from each of four groups (Groups 1, 2, 3, 4) and be placed in any order.

•Group 1

—Lock and repeat prefixes:

•F0H—LOCK

•F2H—REPNE/REPNZ (used only with string instructions; when used with the escape opcode 0FH, this prefix is treated as a mandatory prefix for some SIMD instructions)

•F3H—REP or REPE/REPZ (used only with string instructions; when used with the escape opcode 0FH, this prefix is treated as an mandatory prefix for some SIMD instructions)

•Group 2

—Segment override prefixes:

•2EH—CS segment override (use with any branch instruction is reserved)

•36H—SS segment override prefix (use with any branch instruction is reserved)

•3EH—DS segment override prefix (use with any branch instruction is reserved)

•26H—ES segment override prefix (use with any branch instruction is reserved)

•64H—FS segment override prefix (use with any branch instruction is reserved)

•65H—GS segment override prefix (use with any branch instruction is reserved)

—Branch hints:

•2EH—Branch not taken (used only with Jcc instructions)

•3EH—Branch taken (used only with Jcc instructions)

•Group 3

•66H—Operand-size override prefix (when used with the escape opcode 0FH, this is treated as a mandatory prefix for some SIMD instructions)

•Group 4

•67H—Address-size override prefix

2-2 Vol. 2