- •Национальный исследовательский университет «Московский энергетический институт» Институт Автоматики и вычислительной техники Кафедра Прикладной

- •Актуальность работы

- •Постановка задачи

- •Исследование современных подходов в области JTAG тестирования

- •Общая схема функционального тестирования

- •Требования к разрабатываемому комплексу

- •Общая архитектура комплекса

- •Выбор одноплатной ЭВМ

- •Состав аппаратной части комплекса

- •Состав программного обеспечения комплекса

- •Режимы работы тестового программного обеспечения комплекса

- •Архитектура разработанного программного обеспечения

- •Список разработанных тестов для СБИС

- •Блок схема теста блока самотестирования памяти MBIST

- •Пример работы разработанного ПО

- •Обнаруженные в результате тестирования ошибки

- •Результаты работы

- •Перспективы разработки

- •Спасибо за внимание!

Состав программного обеспечения комплекса

Тестовое программное обеспечение на языке программирования Python

OpenOCD (OpenSource)

libftdi (OpenSource)

Rasbrian (OpenSource)

Слайд №11

Режимы работы тестового программного обеспечения комплекса

Интерактивный

режим

Возможность запуска одного из разработанных для СБИС тестов

Запись/чтение регистров

Не

интерактивный

режим

Последовательный запуск всех разработанных тестов

Запись в логфайл отладочной информации

Слайд №12

Архитектура разработанного программного обеспечения

Reg_property.py |

Reg_base.py |

Test_base.py |

Reg_map.py |

Reg_*.py |

Test_*.py |

Testsuite_base.py

Testsuite_shema6.py

Framework.py

OpenOCD

Слайд №13

Список разработанных тестов для СБИС

1907КХ018

Тест ID кода и ID производителя микросхемы Тест высокоскоростных каналов

Тест генераторов/приемников PRBS

Тест шины I2C

Тест внутренних генераторов/приемников пакетов Тест блока самотестирования памяти MBIST

Слайд №14

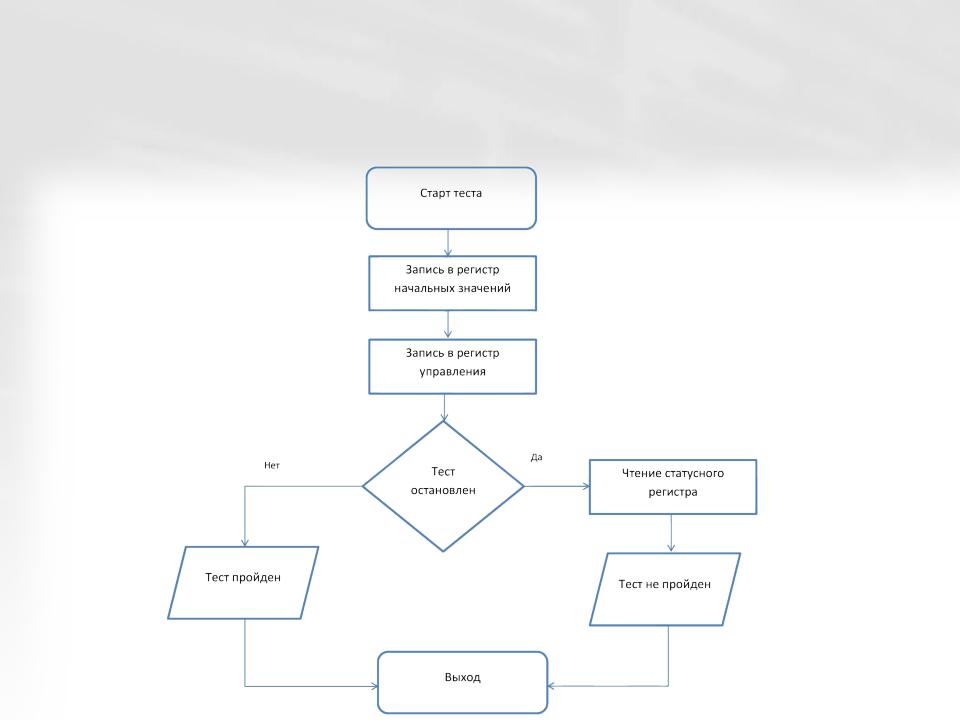

Блок схема теста блока самотестирования памяти MBIST

Слайд №15

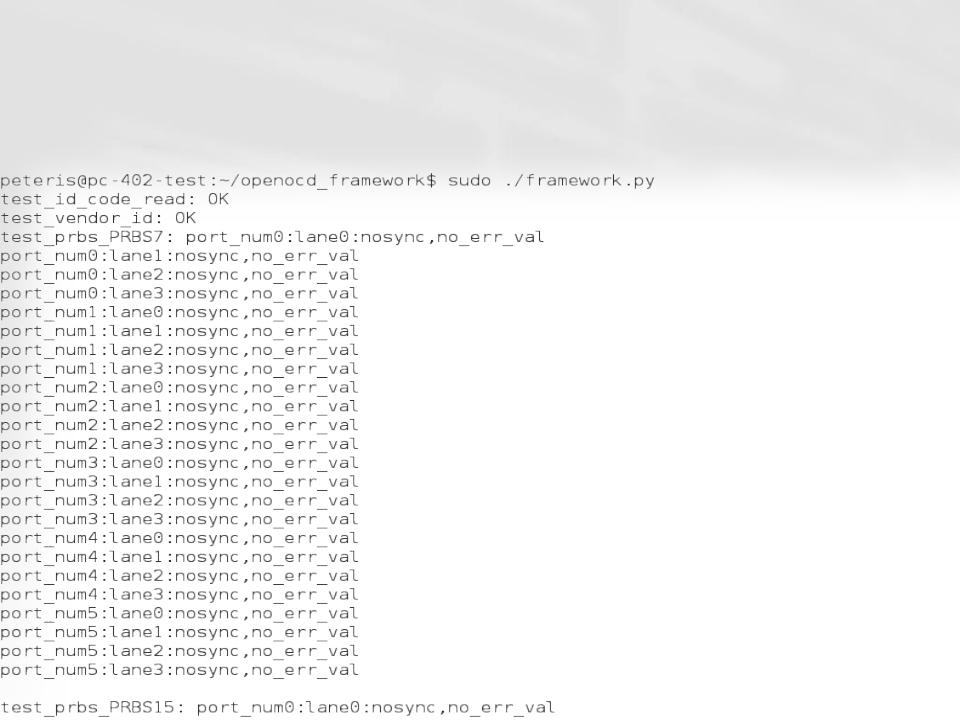

Пример работы разработанного ПО

Слайд №16

Обнаруженные в результате тестирования ошибки

|

Тестирование |

Тестирование |

Тестирование |

|

Запуск каждого |

блока MBIST |

генераторов и |

шины I2C |

|

• На одной из |

приемников |

• Шина I2C работала |

||

из тестов |

памятей не |

PRBS |

не полностью |

|

производился |

проходил не один |

• Работали лишь 4 из |

соответствуя |

|

лишь после |

из алгоритмов |

официальному |

||

заявленных 8 в |

||||

чтения ID кода |

тестирования. |

документации |

алгоритму. |

|

микросхемы. |

|

режимов. |

|

Слайд №17

Результаты работы

Разработана общая архитектура комплекса на основе сформулированных требований

Разработано тестовое программное обеспечения с двумя режимами работы.

Реализована предложенная архитектура, собранные воедино компоненты системы прошли функциональную проверку на работоспособность.

Описаны полученные в результате тестирования СБИС коммутатора Rapid IO 19007KX018 ошибки

Составлена инструкция по эксплуатации системы

Слайд №18

Перспективы разработки

В перспективе предполагается адаптировать разработанную систему для работы с более чем одним устройством в JTAG цепочке, а так же увеличивать тестовый набор для функционального тестирования логических блоков других интегральных схем.

Слайд №19