- •Национальный исследовательский университет «Московский энергетический институт» Институт Автоматики и вычислительной техники Кафедра Прикладной

- •Актуальность работы

- •Постановка задачи

- •Исследование современных подходов в области JTAG тестирования

- •Общая схема функционального тестирования

- •Требования к разрабатываемому комплексу

- •Общая архитектура комплекса

- •Выбор одноплатной ЭВМ

- •Состав аппаратной части комплекса

- •Состав программного обеспечения комплекса

- •Режимы работы тестового программного обеспечения комплекса

- •Архитектура разработанного программного обеспечения

- •Список разработанных тестов для СБИС

- •Блок схема теста блока самотестирования памяти MBIST

- •Пример работы разработанного ПО

- •Обнаруженные в результате тестирования ошибки

- •Результаты работы

- •Перспективы разработки

- •Спасибо за внимание!

Национальный исследовательский университет «Московский энергетический институт» Институт Автоматики и вычислительной техники Кафедра Прикладной математики

Магистерская диссертация на тему

«Разработка программно-аппаратного комплекса для JTAG тестирования»

Студент: Алексан П.А. Группа А1308 Научный руководитель: доц., к.т.н. Сидорова Н.П.

Москва, 2014

Актуальность работы

JTAG-порт микросхемы и

ячейки периферийного

сканирования.

•В настоящее время на рынке

существует несколько

решений для функционального

тестирования систем на базе технологии граничного

сканирования JTAG.

•Все рассмотренные в рамках исследования системы предоставляют доступ к стандартным функциям JTAG, в то время как в процессе

отладки СБИС разработки

НИИСИ РАН требуется доступ к специализированным функциям.

Постановка задачи

• |

Задачей магистерской |

|

диссертации стала |

|

разработка программно- |

|

аппаратного комплекса, |

|

позволяющего производить |

|

специализированное |

|

функциональное |

|

тестирование логических |

|

блоков СБИС разработки |

|

НИИСИ РАН, в том числе |

|

Rapid IO коммутатора |

Структурная схема микросхемы |

1907KX018 |

коммутатора Rapid IO 1907kx018 |

|

|

Слайд №3 |

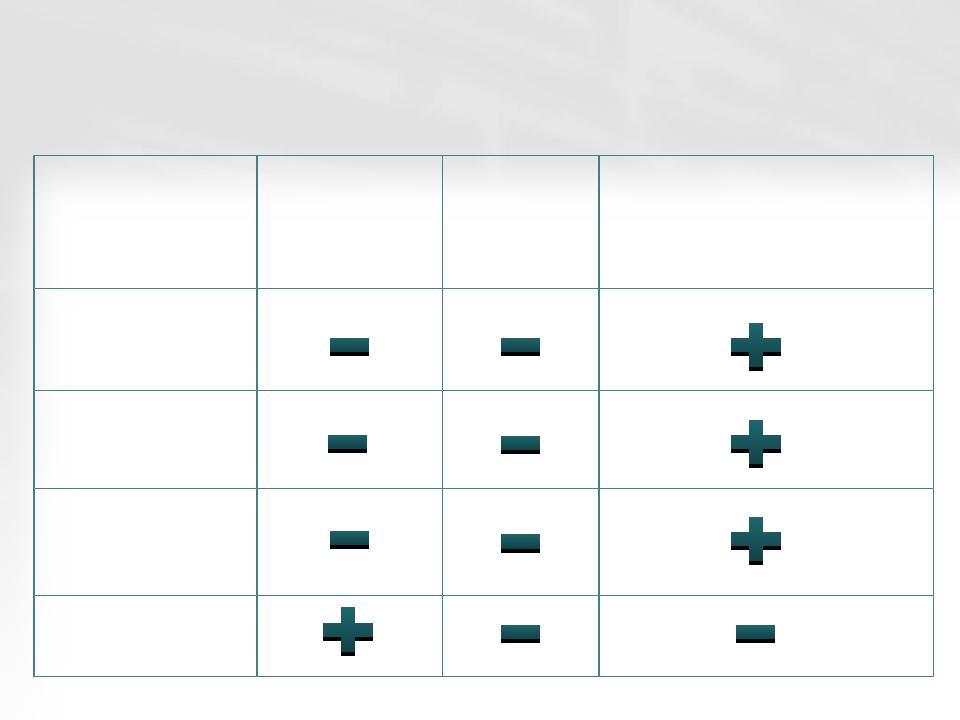

Исследование современных подходов в области JTAG тестирования

Наименование |

Возможность |

Открытый |

Поддержка |

стандартных |

|

удаленной |

исходный |

языков программирования |

|

|

работы |

код |

|

|

JTAG Live Studio

JTAG ProVision

XJTAG Professional

Блок БЗР 680

Слайд №4

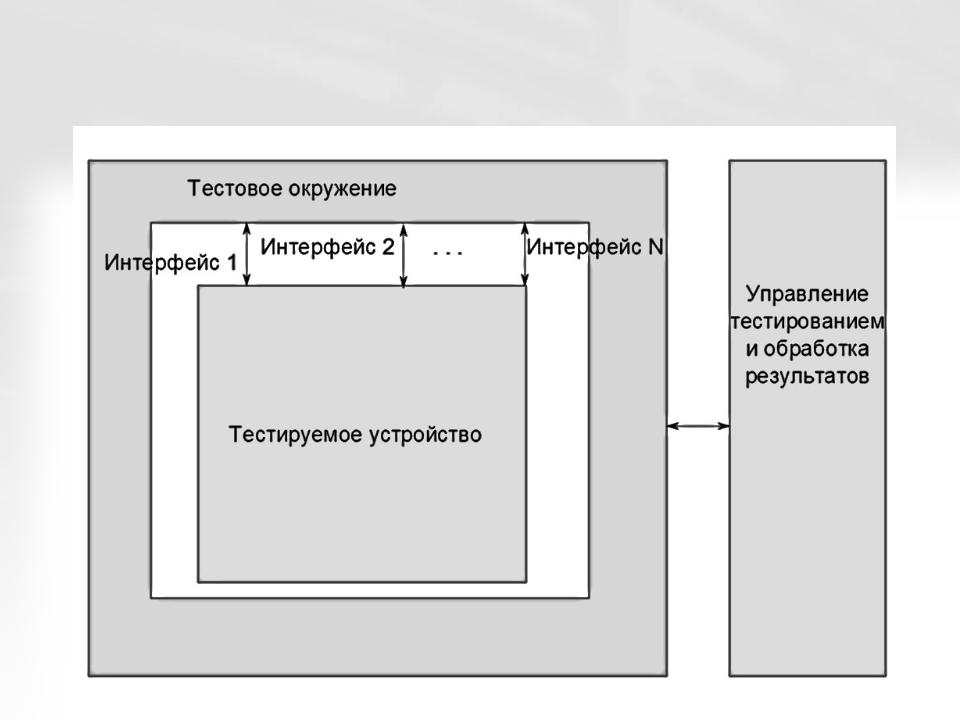

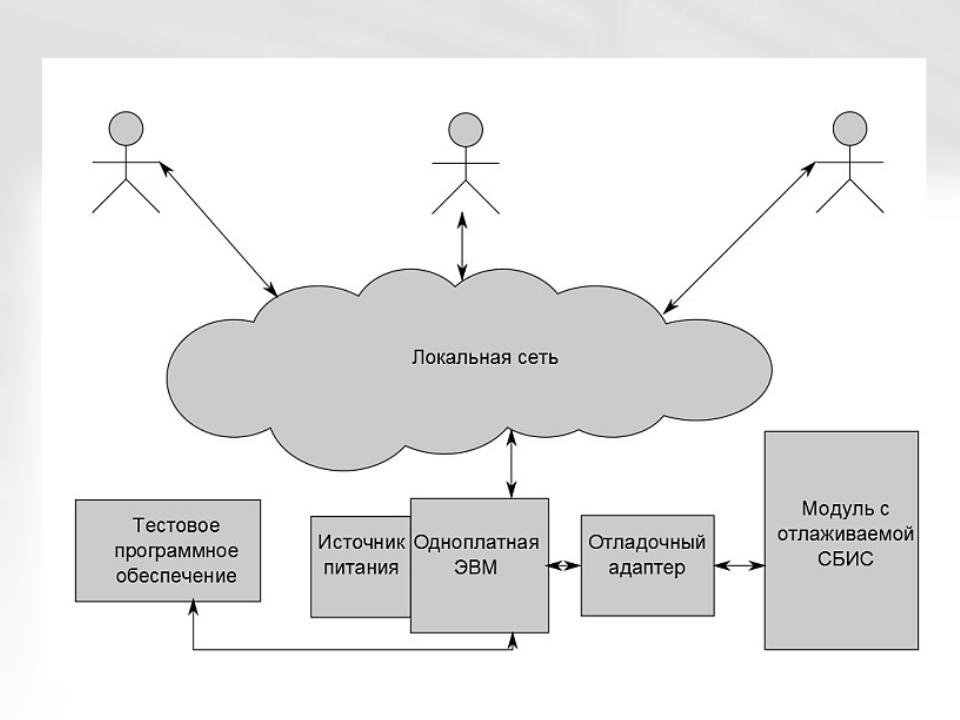

Общая схема функционального тестирования

Слайд №5

Требования к разрабатываемому комплексу

Функциональные требования к комплексу

•Взаимодействие с тестируемым устройством через интерфейс JTAG

•Возможность разработки тестового набора для логических блоков тестируемого устройства

•Возможность обработки полученных результатов с помощью комплекса

Нефункциональные требования к комплексу

•Удаленный доступ к комплексу

•Открытый исходный код компонентов тестового программного окружения

•Питание от 220В

Слайд №6

Общая архитектура комплекса

Слайд №7

Выбор одноплатной ЭВМ

• |

700MHz |

• |

|

• |

памяти SD/MMC/SDIO объемом до 32 Гб |

• |

порта |

• |

Мбит |

• |

A8 1Ghz |

• |

|

• |

встроенной NAND флешпамяти |

• |

|

• |

Мбит |

• |

A7 Dual Core 1 Ghz |

• |

|

• |

встроенной NAND флэшпамяти, SD карты до 64Гб, SATA диски до 2Tб |

• |

порта |

• |

Мбит |

Слайд №8

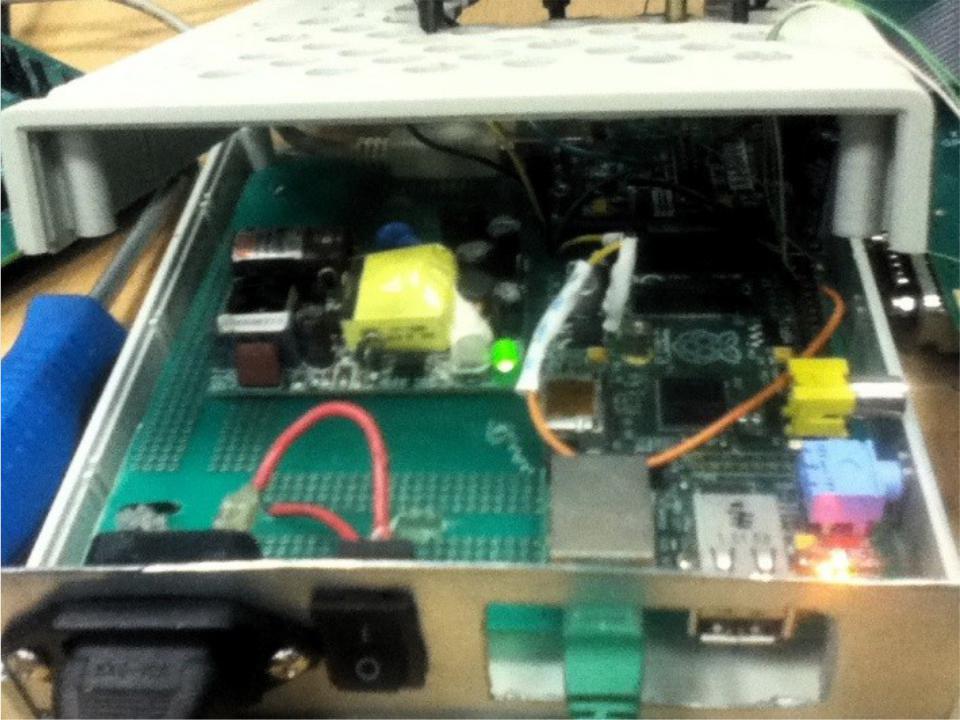

Состав аппаратной части комплекса

Модуль с одноплатной ЭВМ Rasberry Pi model B

Отладочный адаптер марки FTDI на базе ft2232c со встроенным MPSSE устройством

Источник питания с выходным напряжением в 5В

СБИС 1907KX018

Слайд №9