- •Аннотация

- •Глава 3 посвящена разработке программно-аппаратного комплекса, сборке аппаратной части и разработке программного окружения.

- •Глава 4 содержит в себе описание тестируемой сбис, а так же результаты ее тестирования с применением разработанного программно-аппаратного комплекса.

- •Глава 1. Исследование методов jtag тестирования сбис.........6

- •Глава 2. Архитектура комлекса jtag тестирования....................19

- •Глава 3. Аппаратное и программное обеспечение комплекса.......................................................................................................32

- •Глава 4 исследование сбис 1907кх018..................................................59

- •Глава 1. Исследование методов jtag тестирования сбис

- •Глава 2. Архитектура комплекса jtаg тестирования.

- •2.1 Общая архитектура комплекса

- •2.2 Аппаратная часть комплекса jtag тестирования

- •2.3 Программная часть комплекса jtag тестирования.

- •2.4 Выводы к главе

- •Глава 3. Аппаратное и программное обеспечение комплекса

- •3.1 Разработка аппаратной части комплекса

- •3.2 Разработка программного обеспечения для jtag тестирования

- •3.2.1 Выбор операционной системы

- •Глава 4. Исследование сбис 1907кх018

- •Регистр i2c_ctrl_2

- •Регистр i2c_stat_1 (1a020h)

- •Регистр i2c_stat_2

Глава 4. Исследование сбис 1907кх018

После успешной реализации компонентов комплекса, необходимо проверить работоспособность системы в процессе исследования СБИС 1907КХ018.

4.1 Краткое описание тестируемой СБИС

Интегральная микросхема 1907КХ018 (далее по тексту – микросхема) предназначена для построения высокопроизводительных вычислительных комплексов для систем управления перспективных образцов вооружения, включая системы авиационного и космического базирования.

Центральным элементом комплексов управления образцов вооружения и военной техники космического, авиационного и наземного применения являются высоконадежные многопроцессорные системы. Основной функцией таких систем являются прием/передача данных с каналов связи, их обработка в режиме реального времени и выдача управляющих и информационных команд. Широкое применение в таких системах находит последовательный интерфейс RapidIO 1х/4х LP-Serial. Канал RapidIO представляет собой последовательный дуплексный интерфейс типа «точка-точка».

Микросхема представляет собой коммутатор последовательных каналов RapidIO, предназначенный для организации связи между устройствами с интерфейсом RapidIO. 1907КХ018 использует неблокируемый режим коммутации. Конфигурация коммутатора может производиться через интерфейс RapidIO с помощью служебных пакетов или через интерфейс I2C.

Технические характеристики.

Микросхема 1907КХ018 имеет следующие технические характеристики:

шесть каналов RapidIO 1х/4х;

скорость передачи по каналу RapidIO 1.25 Гбит/с;

поддержка до 256 номеров устройств (ID);

номинальное значение напряжения питания UCC = 2,5 В;

допустимые отклонения напряжения питания от номинального ±5%;

Микросхема 1907КХ018 включает в себя:

шесть контроллеров последовательных каналов RapidIO 1х/4х;

блок коммутации;

таблицы маршрутизации;

блок регистров;

систему контроля производительности для каждого порта RapidIO;

контроллер интерфейса I2C;

контроллер интерфейса JTAG;

Микросхема коммутатора RapidIO предназначена для организации связи между устройствами с интерфейсом RapidIO. Микросхема коммутатора содержит шесть портов последовательного RapidIO 1х/4х, работающих со скоростью 1,25 Гбит/с [8].

На рисунке 16 показана структурная схема коммутатора.

Рис. 16 Структурная схема микросхемы коммутатора RapidIO.

Микросхема имеет блок внутренних регистров, используемых для управления работой коммутатора. Доступ к регистрам возможен через любой порт RapidIO с использованием служебных пакетов, а также через интерфейсы JTAG и i2c.

Также возможна начальная загрузка регистров и таблиц маршрутизации из внешней микросхемы EEPROM с интерфейсов i2c.

4.2 Описание разработанных тестов

В данном разделе рассмотрим разработанные тесты для отлаживаемой в рамках работы СБИС.

Тест ID кода и ID производителя микросхемы.

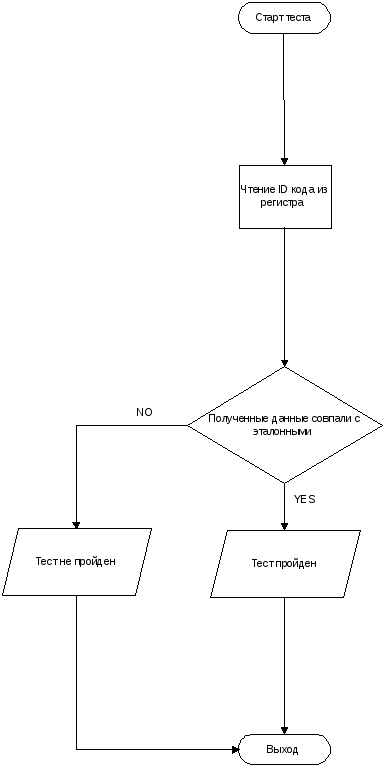

Данный тест предназначен, в первую очередь, для проверки корректности работы цепи. Принцип работы теста заключается в считывании регистра, содержащего ID код микросхемы, сравнении полученного значения с эталонным. При совпадении результатов выдается сообщение об успешном прохождении теста. На рисунке 17 приведена логическая структура данного теста.

Рис. 17 Блок схема алгоритма теста ID кода СБИС.

Тест генераторов/приемников PRBS.

Управляя с помощью чтения и записи в соответствующие регистры тестовым генератором приемопередатчика RapidIO, считываем и сравниваем полученные данные из регистра, отвечающего за приемник PRBS. Тест считается пройденным, если на приемник приходят корректные данные, то есть те, которые были заданы генератору PRBS.

Регистры управления генераторами PRBS.

Управление генераторами PRBS возможно через интерфейс JTAG. Для каждой линии каждого интерфейса RapidIO имеются два регистра:

PRBS_xy_CTL_REG0 и PRBS_xy_CTL_REG1, где x – номер порта (0-5), y – линия (0-3).

Регистр PRBS_xy_CTL_REG0 предназначен для установки режима работы генератора

Регистр PRBS_xy_CTL_REG1 предназначен для получения информации о состоянии работы генератора/приемника PRBS. В фазе CPATURE регистр защелкивает состояние блока PRBS.

После фазы UPDATE загруженное в регистр значение сигналов подается на блок PRBS для считывания и сброса состояния об ошибках. На рисунке 18 приведена логическая структура теста PRBS.

Рис. 18 Блок схема алгоритма теста PRBS

Тест блока самотестирования памяти MBIST

Для каждого блока памяти используется свой блок самотестирования, управление которыми осуществляется одним блоком управления. Блоки самотестирования работают параллельно. Доступ к блоку управления осуществляется через JTAG. Могут тестироваться блоки памяти с числом портов не более двух.

Блок самотестирования способен выполнять следующие тесты памяти: маршевый (алгоритмы: March LR, March C–, MATS++), адресный, “бегущая единица”, “бегущий ноль”, однократная запись, однократное чтение.

Блок управления имеет следующие регистры: регистр управления (CR), регистр начальных значений (SVR), статусный регистр SR.

Регистр управления задает запускаемые тесты, кроме того, он содержит разряд разрешения проведения теста, разряд запуска теста [0]/статусный разряд окончания операции, разряд запуска теста [1]/статусный разряд ошибки. Также в этом регистре определяются блоки памяти, для которых будет проводиться самотестирование и содержится статусная информация о результатах прохождения теста для каждого блока памяти.

Регистр начальных значений задает адрес и данные. Регистр состоит из двух частей: адрес, данные (адрес соответствует старшим разрядам регистра, данные - младшим). Регистр задает адрес и данные, используемые в следующих тестах: однократная запись, однократное чтение, “бегущая единица”, “бегущий ноль”.

Статусные регистры содержат информацию о блоках памяти, при тестировании которых произошла ошибка. Для каждого блока памяти используется свой статусный регистр. В регистрах содержится: номер порта, номер теста, номер этапа (для маршевого теста), номер чтения (для маршевого теста), адрес и данные.

Тест запускается в режиме с контролем информации об ошибках. Если во время теста произошла ошибка, то тест остановится и в статусный регистр запишется информация, позволяющая произвести диагностику. После считывания статусной информации можно запустить тест на дальнейшее выполнение. На рисунке 19 приведена блок схема теста блока самотестирования памяти.

Рис. 19 Блок схема алгоритма теста блока самотестирования памяти MBIST

Тест шины i2c. Алгоритм проведения теста был подробно описан в главе 3.

Далее рассмотрим режимы работы системы.

4.3 Режимы работы системы

Режим полной проверки логических блоков СБИС. В данном режиме необходимо обеспечить последовательное проведение всех тестов, для выявления проблемных логических блоков СБИС. Причем процесс проведения тестов всегда должен начинаться с теста ID кода СБИС. Данный режим предлагается запускать по умолчанию, то есть при запуске программного окружения без параметров (рис.20).

Рис.20 Режим полной проверки логических блоков СБИС

Режим запуска отдельных тестов. Пользователю системы предлагается выбрать один из множества тестов. Для запуска системы в данном режиме необходимо использовать при запуске параметр -i (рис.21).

Рис.21 Режим запуска отдельных тестов

Режим чтения отдельных регистров. В данном режиме пользователь имеет возможность прочитать любой доступный из списка регистр. Для запуска системы в данном режиме нужно так же, как и в режиме 2, использовать параметр -i, а затем выбрать режим чтения регистров (r). Пример работы режима предоставлен на рисунке 22.

Р ис.22

Режим чтения отдельных регистров

ис.22

Режим чтения отдельных регистров

4.4 Результаты тестирования

Реализованный программно-аппаратный комплекс позволяет работать со СБИС на частоте 1КГц. То есть при частоте TCK в 3МГц имеется возможность обрабатывать порядка 1000 тестовых последовательностей в секунду.

Благодаря разработанному комплексу удалось, за счет повышения уровня абстракции, улучшить качество тестирования СБИС, и, как следствие, снизить риски выпуска некачественных образцов. Улучшение качества тестирования произведено также за счет увеличения тестового покрытия, что влечет за собой увеличение количества обнаруженных ошибок. Благодаря использованию стандартных языков программирования в разработке тестов, сокращено время на их разработку и сопровождение, а так же на адаптацию пользователей к данной системе.

В результате тестирования СБИС 1907KX018 были выявлены следующие ошибки:

Ошибки при тестировании блока MBIST. На одной из памятей не проходил не один из алгоритмов тестирования памятей.

Ошибки при тестировании блока PRBS. Работали не все заявленные в документации режимы.

При тестировании шины i2c обнаружились некоторые замечания. Шина i2c работала корректно, однако не полностью соответствуя официальному алгоритму.

Все остальные разработанные тесты прошли без ошибок.

4.5 Выводы к главе

В данной главе были приведены основные результаты работы.

Изучена тестируемая СБИС, указаны ее основные характеристики и особенности.

Разработаны тесты для функционального тестирования СБИС 1907КХ018.

Приведены доступные режимы работы реализованного программного обеспечения.

Подсчитан показатель частоты обращений по интерфейсу JTAG к тестируемой СБИС

Описаны полученные в результате проведения разработанных тестов ошибки.

ЗАКЛЮЧЕНИЕ

Магистерская диссертация была посвящена разработке программно-аппаратного комплекса JTAG для тестирования специализированных СБИС разработки НИИСИ РАН.

Был произведен анализ предметной области, включающий в себя следующие этапы:

рассмотрен интерфейс JTAG, его особенности и определена его специфика;

произведен анализ существующих программно-аппаратных решение в области JTAG тестирования, выявлены их достоинства и недостатки;

сформулированы требования к разрабатываемому комплексу.

В результате выполнения данных задач была выявлена потребность в разработке нового подхода для функционального тестирования СБИС 1907КХ018 SRIO коммутатора разработки НИИСИ РАН.

Далее были рассмотрены вопросы архитектуры разрабатываемого комплекса и выбора его компонентов.

Разработана архитектура комплекса, удовлетворяющая всем поставленным требованиям к разработке,

Обоснованно выбраны комплектующие для аппаратной части комплекса, а именно одноплатный ПК Rasberry Pi model B, JTAG адаптер на базе FT2232С и источник питания AC/DC c выходным показателем напряжения в 5В.

Представлена архитектура программной части комплекса.

На следующем этапе был рассмотрен процесс реализации компонентов программно-аппаратного комплекса.

В рамках сборки аппаратной базы комплекса была реализована предложенная в главе 2 архитектура, собранные воедино компоненты системы прошли функциональную проверку на работоспособность.

В качестве ОС была выбрана специализированная система Rasbrian.

Разработано программное обеспечение на языке Python, позволяющее тестировать доступные по интерфейсу JTAG блоки СБИС.

Составлена инструкция по установке и настройке системы, а так же приведен пример использования языка TCL для доступа к СБИС, интерпретатор которого встроен в систему OpenOCD.

После реализации всех компонентов комплекса было проведено испытание системы.

Изучена тестируемая СБИС, указаны ее основные характеристики и особенности.

Дано описание разработанных тестов для функционального тестирования СБИС 1907КХ018.

Приведены доступные режимы работы реализованного программного обеспечения.

Подсчитан показатель частоты обращений по интерфейсу JTAG к тестируемой СБИС

Описаны полученные в результате проведения разработанных тестов ошибки.

В перспективе предполагается адаптировать разработанную систему для работы с более чем одним устройством в JTAG цепочке, а так же продолжить использование комплекса в рамках функционального тестирования других СБИС.

СПИСОК ИСПОЛЬЗОВАННОЙ ЛИТЕРАТУРЫ

Кольский Н.Интерфейс JTAG: тестирование плат, программирование и отладка - "Печатный монтаж". Выпуск #1/2009

Рустинов В., Городецкий А. Разделяй и властвуй – принцип граничного сканирования.- Chip News. http://chipnews.gaw.ru/html.cgi/arhiv/01_06/stat3.htm

Стандарт IEEE 1149.6 - www.jtag-test.ru/JTAGUniversity/index.php.

Parker K. The Boundary-Scan Handbook. Analog and Digital - KAP, 2003.

Городецкий A., Курилан Л. Регистры и команды граничного сканирования, часть 2 - «Производство электроники» 2007, №6.

OpenOCD User's Guide - http://openocd.sourceforge.net/doc/html/, 2009

Указания по эксплуатации и применению БЗР 680 - http://doc.cs.niisi.ras.ru/pages/viewpage.action?pageId=14647355, 2013

Плата исследовательская FCS_1907KX018 - http://doc.cs.niisi.ras.ru/pages/viewpage.action?pageId=45813088, 2013

Compiling OpenOCD Linux - http://www.tincantools.com/wiki/Compiling_OpenOCD_Linux, 2013

Программно-Аппаратный комплекс XJTAG - http://www.xjtag.com/ru/xjtag-products.php, 2012

JTAG Live Studio - https://www.jtaglive.com/ru/content/jtag-live-studio, 2013

JTAG ProVision - http://www.jtag.com/ru/content/jtag-provision, 2013

Марк Лутц — Изучаем Python 4-е издание - “Символ-Плюс”, 2013

Марк Лутц — Программирование на Python. Том 2 - “Символ-Плюс”, 2011

ПРИЛОЖЕНИЕ А. Тестирование блока MBIST

mbist_diver.tcl

proc MBIST_Driver_CmdSeq {M0 M1 test_mask} {

return [expr {$M1 << 13 | $M0 << 12 | $test_mask << 4}]

}

proc MBIST_Driver_ReadStatus {cmd_seq} {

set full_cmd [expr {$cmd_seq | 0xD}]

set result [WriteReadSeq 0x10 $full_cmd 44]

return "0x"$result

}

proc MBIST_Driver_Reset {} {

jtag_ntrst_delay 100

reset_config trst_and_srst separate trst_push_pull srst_open_drain

jtag_reset 1 1

jtag_reset 0 0

}

proc MBIST_Driver_Init {} {

# initial reset

MBIST_Driver_Reset

# setup jtag clock from TCK

WriteReadSeq 0x0D 0x3 2

}

proc MBIST_Driver_Start {cmd_seq} {

#WriteReadSeq 0x10 0x180F 44

set full_cmd [expr {$cmd_seq | 0xF}]

WriteReadSeq 0x10 $full_cmd 44

}

proc MBIST_Driver_Continue {cmd_seq} {

#WriteReadSeq 0x10 0x180B 44

set full_cmd [expr {$cmd_seq | 0xB}]

WriteReadSeq 0x10 $full_cmd 44

# wait test to start

for {set i 0} {$i < 10} {incr i} {

MBIST_Driver_ReadStatus $cmd_seq

}

}

proc MBIST_Driver_ReadSpecificStatus {select} {

switch $select {

"M0" {return [WriteReadSeq 0x12 0x0 103]}

"M1" {return [WriteReadSeq 0x13 0x0 26]}

default {puts "ERROR: unknown select $select"}

}

}

proc MBIST_Driver_SingleAccess {M0 M1 port_num addr data operation} {

set seq [expr {$data << 13 | $port_num << 8 | $addr}]

WriteReadSeq 0x11 $seq 89

switch $operation {

"w" {set test_mask 0x1}

"r" {set test_mask 0x2}

default: {puts "ERROR: wrong operation $operation"}

}

set cmd_seq [MBIST_Driver_CmdSeq $M0 $M1 $test_mask]

MBIST_Driver_Start $cmd_seq

return [MBIST_Driver_ReadStatus $cmd_seq]

}

proc MBIST_Driver_Initial_Values_Reg {port addr} {

set seq [expr {$port << 8 | $addr}]

WriteReadSeq 0x11 $seq 89

}

mbist_err_stat_012.tcl

proc MBIST_ErrStatus012_PortNum {status} {

set port_str [string range $status 24 25]

set port_value [format "0x%s" $port_str]

return [expr {$port_value & 0x1F}]

}

proc MBIST_Decode_PortNum_M012 {port_num} {

switch $port_num {

0 {return "Port_0/SRIO_OutputBufferTop/SRIO_OutputBuffer/ram1"}

1 {return "Port_0/SRIO_InputBufferTop/SRIO_InputBuffer/ram1"}

2 {return "Port_1/SRIO_OutputBufferTop/SRIO_OutputBuffer/ram1"}

3 {return "Port_1/SRIO_InputBufferTop/SRIO_InputBuffer/ram1"}

4 {return "Port_2/SRIO_OutputBufferTop/SRIO_OutputBuffer/ram1"}

5 {return "Port_2/SRIO_InputBufferTop/SRIO_InputBuffer/ram1"}

6 {return "Port_3/SRIO_OutputBufferTop/SRIO_OutputBuffer/ram1"}

7 {return "Port_3/SRIO_InputBufferTop/SRIO_InputBuffer/ram1"}

8 {return "Port_4/SRIO_OutputBufferTop/SRIO_OutputBuffer/ram1"}

9 {return "Port_4/SRIO_InputBufferTop/SRIO_InputBuffer/ram1"}

10 {return "Port_5/SRIO_OutputBufferTop/SRIO_OutputBuffer/ram1"}

11 {return "Port_5/SRIO_InputBufferTop/SRIO_InputBuffer/ram1"}

default {return "Unknown port $port_num"}

}

}

proc MBIST_ErrStatus012_Test {status} {

set test_str [string index $status 24]

set test_value [format "0x%s" $test_str]

return [expr {($test_value & 0xE) >> 1}]

}

proc MBIST_ErrStatus012_Stage {status} {

set stage_str [string index $status 23]

set stage_value [format "0x%s" $stage_str]

return [expr {$stage_value & 0x7}]

}

proc MBIST_ErrStatus012_NumRead {status} {

set num_read_str [string index $status 23]

set num_read_value [format "0x%s" $num_read_str]

return [expr {($num_read_value & 0x8) >> 3}]

}

proc MBIST_ErrStatus012_Digit {status} {

set digit_str [string range $status 20 22]

set digit_value [format "0x%s" $digit_str]

return [expr {$digit_value & 0x7F}]

}

proc MBIST_ErrStatus012_Addr {status} {

set addr_str [string range $status 19 21]

set addr_value [format "0x%s" $addr_str]

return [expr {($addr_value & 0x7F8) >> 3}]

}

proc MBIST_ErrStatus012_Data {status} {

set data_str [string range $status 0 19]

return "$data_str\[#>>3\]"

}

proc MBIST_PrintErrorStatus_M012 {status} {

set st_port_num [MBIST_ErrStatus012_PortNum $status]

set st_port_decode [MBIST_Decode_PortNum_M012 $st_port_num]

# append result "FAIL at $st_port_decode"

append result "FAIL at port $st_port_num"

append result " raw_st $status"

set st_test [MBIST_ErrStatus012_Test $status]

set st_test_decode [MBIST_Decode_Test $st_test]

append result " test $st_test $st_test_decode"

set test_marsh [MBIST_Decode_TestMarsh $st_test]

set test_runnung_01 [MBIST_Decode_TestRunnung01 $st_test]

if {$test_marsh} {

set st_stage [MBIST_ErrStatus012_Stage $status]

set st_stage_decode [MBIST_Decode_Stage $st_stage]

append result " tstage $st_stage: $st_stage_decode"

set st_nrd [MBIST_ErrStatus012_NumRead $status]

append result " num_read $st_nrd"

}

if {$test_runnung_01} {

set st_digit [MBIST_ErrStatus012_Digit $status]

append result " digit $st_digit"

}

set st_addr [MBIST_ErrStatus012_Addr $status]

append result [format " addr 0x%X" $st_addr]

set st_data [MBIST_ErrStatus012_Data $status]

append result " read data $st_data"

return $result

}

mbist_test_decode.tcl

proc MBIST_Decode_TestMarsh {st_test} {

if {[expr {$st_test == 5 || $st_test == 6 || $st_test == 7}]} {

return 1

}

return 0

}

proc MBIST_Decode_TestRunnung01 {st_test} {

if {[expr {$st_test == 3 || $st_test == 4}]} {

return 1

}

return 0

}

proc MBIST_Decode_Test {test} {

switch $test {

0 {return "SINGLE WRITE"}

1 {return "SINGLE READ"}

2 {return "ADDR_EN"}

3 {return "RUNNUNG ONE"}

4 {return "RUNING ZERO"}

5 {return "MARCH LR"}

6 {return "MARCH C-EN"}

7 {return "MARCH ++_EN"}

default {return "unknown"}

}

}

proc MBIST_Decode_Stage {stage} {

return "M$stage"

}

ПРИЛОЖЕНИЕ Б. Описание регистров теста шины i2c.

Регистр I2C_CTRL_1 (1A018h)

Адрес – 1A018h.

Регистр 1 управления шины I2C:

Таблица 4.Регистр I2C_CTRL_1 (1A018h)

Разряды

Название

Начальное состояние

Описание

Доступ

31

I2C_ADV_FORMAT

0h

Разряд определяет формат EEPROM:

1 – расширенный формат EEPROM (ускоренная загрузка регистров по последовательным адресам;

0 – совместимый формат EEPROM

R/W

30:26

Reserved

0h

Зарезервировано

R

25:24

PA_SIZE

1h

Разряды определяют размер адреса внешнего устройства на шине I2C:

00b – адрес не используется;

01b – 8-и разрядный адрес (младшие разряды поля PADDR регистра I2C_CTRL_2);

10b – 16-и разрядный адрес (поле PADDR регистра I2C_CTRL_2);

11b – зарезервировано

R/W

23:10

Reserved

0000h

Зарезервировано

R

9

I2C_DIS

Не определено

Состояние внешнего сигнала I2C_DIS

R

8

I2C_SEL

Не определено

Состояние внешнего сигнала I2C_SEL

R

7

Reserved

0h

Зарезервировано

R

6:0

DEV_ADDR

50h

Адрес внешнего устройства на шине I2C. По включению питания или после сброса младшие разряды [2:0] устанавливаются в соответствии с состоянием входных сигналов I2C_ID и I2C_SEL. Если I2C_SEL равен нулю, то значения разрядов DEV_ADDR[2:0] соответствуют значению на входных линиях I2C_ID[2:0]. Если I2C_SEL равен нулю, то значения разрядов DEV_ADDR[2:0] устанавливаются в ноль. Все разряды доступны для записи

R/W