- •Двухполюсные элементы электрической цепи.

- •Резистивный элемент. Вольт-амперные характеристики резистивных элементов.

- •Независимые источники напряжения и тока.

- •Управляемые(зависимые) источники.

- •Идеальные операционные усилители. Модели оу в линейном и нелинейном режимах. Примеры расчёта типовых схем на интегральных оу.

- •Характеристики эквивалентного двухполюсника. Передача энергии от эквивалентного двухполюсника нагрузке. Режим согласованной нагрузки.

- •Теорема об эквивалентном двухполюснике(Теорема Тевенина и Нортона). Метод эквивалентного генератора. Примеры расчёта (мост Уитстона)

- •Причины возникновения переходных процессов. Законы коммутации. Независимые начальные условия.

- •Переходные процессы в rc-цепях первого порядка. Постоянная времени. Реакция при нулевом входе и нулевом начальном состоянии. Порядок расчёта.

- •Переходные процессы в rl-цепях первого порядка. Постоянная времени. Порядок расчёта.

- •Интегрирующие и дифференциальные цепи.

- •Единичная ступенчатая и единичная импульсная функции. Переходная и импульсная характеристика цепи. Связь между переходной и импульсной характеристикой.

- •12. Двухполюсные элементы в электрической цепи в установившемся синусоидальном режиме.

- •Метод комплексных амплитуд. Комплексное сопротивление и проводимость. Закон Ома для комплексных амплитуд.

- •Мощности в цепи синусоидального тока. Активная, реактивная, полная и комплексная мощности. Коэффициент мощности.

- •Резонанс в электрических цепях. Резонанс напряжений. Частотные характеристики последовательного и резонансного токов.

- •Резонанс токов. Параллельный колебательный контур.

- •Комплексные передаточные функции (комплексные частотные характеристики). Амплитудно частотные и фазо-частотные х-ки. Логарифмические х-ки.

- •Трехфазные цепи. Технико-экономические преимущества трехфазных цепей. Способы соединения генератора и нагрузки в трехфазной цепи.

- •Цепи периодического несинусоидального тока. Ряд Фурье в комплексной форме. Комплексный частотный спектр.

- •Полупроводниковые диоды. Принцип действия. Характеристики.

- •Специальные типы диодов.

- •Применение диодов. Источники вторичного электрического питания.

- •Двухполупериодные выпрямители. Сглаживающие фильтры.

- •Биполярные транзисторы. Схемы включения. Режим работы.

- •Вольт-амперные характеристики биполярных транзисторов.

- •Простейшие модели Биполярных транзисторов.

- •Типовые схемы усилителей на биполярных транзисторах.

- •Усилительный каскад на биполярном транзисторе, включенном по схеме с общим эмиттером и отрицательной обратной связью.

- •Эмиттерный повторитель

- •Полевые транзисторы с управляющим p–n- переходом

- •Полевые транзисторы с изолированным затвором (моп-транзисторы)

- •Усилители основные определения и характеристики

- •Обратные связи в усилителях. Влияние отрицательной обратной связи на хар-ки усилителя.

- •Дифференциальные усилители. Принцип действия и характеристики на биполярных и моп-транзисторах.

- •Операционные усилители. Структура и характеристики оу на биполярных и моп-транзисторах.

- •Базовые логические элементы интегральных схем. Логический инвертор.

- •Инвертор на биполярном транзисторе. Анализ в статическом и динамическом режимах.

- •Кмоп-логика. Принцип построения элементов.

- •Логические элементы на основе биполярных и моп-транзисторов. БиКмоп-логика

- •Основные параметры цифровых микросхем.

- •Цифроаналоговые преобразователи

- •Аналого-цифровые преобразователи

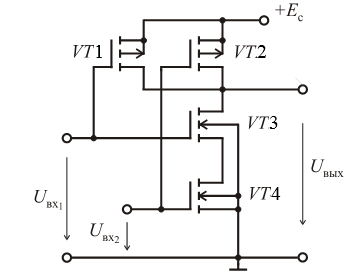

Кмоп-логика. Принцип построения элементов.

Общая

закономерность построения таких

элементов заключается в том, что

параллельное соединение транзисторов

с каналами p-типа сопровождается

последовательным соединением транзисторов

с каналами n-типа и наоборот. схема

КМОП-элемента, реализующего операцию

2И-НЕ. p-канальные транзисторы VT1 и VT2

соединены параллельно, а n-канальные

транзисторы VT3 и VT4 – последовательно.

Подложки и истоки VT1 и VT2 соединены с

положительным зажимом источника питания,

поэтому

,

,

.

.

Пусть на

обоих входах действует напряжение

низкого уровня:

.

Поскольку

.

Поскольку

,

,

,

транзисторы VT3 и VT4 закрыты. При этом

,

транзисторы VT3 и VT4 закрыты. При этом

и транзисторы VT1 и VT2 открыты. Упрощенно

цепь на рис. 13.17 можно представить

эквивалентной схемой, показанной на

рис. 13.18, а. Напряжения на открытых

транзисторах VT1 и VT2 пренебрежимо малы,

и выходное напряжение

и транзисторы VT1 и VT2 открыты. Упрощенно

цепь на рис. 13.17 можно представить

эквивалентной схемой, показанной на

рис. 13.18, а. Напряжения на открытых

транзисторах VT1 и VT2 пренебрежимо малы,

и выходное напряжение

.

.

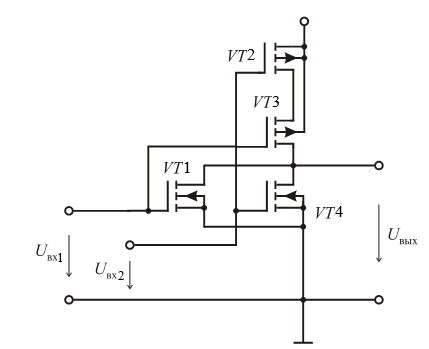

2ИЛИ -НЕ

Здесь

p-канальные транзисторы включены

последовательно, а n-канальные –

параллельно. КМОП-элементы ИЛИ-НЕ

занимают на кристалле значительно

большую площадь, чем элементы И-НЕ. Это

объясняется тем, что последовательно

соединенные p-канальные транзисторы

должны иметь большую ширину канала, чем

при параллельном соединении. Действительно,

два последовательно соединенных

p-канальных транзистора можно рассматривать

как один с каналом длиной 2L. Для

согласования с n-канальными транзисторами

они должны иметь канал шириной

.

Поэтому в схемах высокой степени

интеграции для экономии площади кристалла

целесообразно использовать элементы

И-НЕ.

.

Поэтому в схемах высокой степени

интеграции для экономии площади кристалла

целесообразно использовать элементы

И-НЕ.

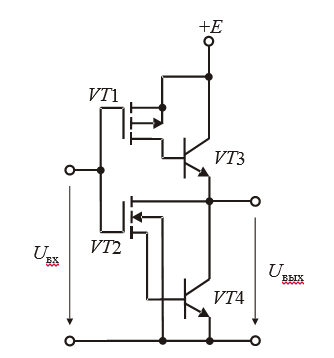

Логические элементы на основе биполярных и моп-транзисторов. БиКмоп-логика

Достоинства КМОП-элементов – низкое

потребление, высокие входное сопротивление

и помехоустойчивость. Недостатком

является малый ток, отдаваемый

МОП-транзисторами в нагрузку. Это

ограничивает скорость заряда нагрузочной

емкости

и соответственно увеличивает время

переключения. Биполярные транзисторы

имеют большую передаточную проводимость,

чем МОП-транзисторы, поэтому их способность

отдавать ток в нагрузку гораздо выше.

Это свойство биполярных транзисторов

использовано при создании БиКМОП-логических

элементов, совмещающих на одном кристалле

биполярные и МОП-транзисторы с необходимыми

электрическими характеристиками.

и соответственно увеличивает время

переключения. Биполярные транзисторы

имеют большую передаточную проводимость,

чем МОП-транзисторы, поэтому их способность

отдавать ток в нагрузку гораздо выше.

Это свойство биполярных транзисторов

использовано при создании БиКМОП-логических

элементов, совмещающих на одном кристалле

биполярные и МОП-транзисторы с необходимыми

электрическими характеристиками.

Простейшая схема БиКМОП-инвертора

Основные параметры цифровых микросхем.

Быстродействие ИС,определяется средней задержкой сигнала tcp, равной среднему арифметическому задержек включения и выключения одного инвертора. При определении средней задержки в качестве границ временных интервалов обычно берут точки на фронтах, соответствующие половине перепада напряжения, или точки, соответствующие уровням 0,1 и 0,9 этого перепада. По средней задержке логические ИС делятся на сверхбыстродействующие (tcp <5 нс), быстродействующие (tcp =5-10 нс), среднего быстродействия (tcp = 10-100 нс), низкого быстродействия (tcp >100 нс). Схемы ТТЛ-типа относятся к схемам среднего быстродействия. Для них типична средняя задержка 5-50 нс. Наибольшее быстродействие имеют транзисторные логические схемы с эмиттерными связями. Для них средняя задержка составляет 1-10 нс.

Потребляемая мощность логических ИС обычно зависит от того, какие сигналы поданы на входы этой ИС. Поэтому потребляемую мощность принято оценивать средней мощностью ( Р ср ), потребляемой типовым логическим элементом во включенном и выключенном состояниях. Чем выше быстродействие схем, тем больше средняя потребляемая ими мощность. Для схем ЭСЛ Рср составляет 20 - 80 мВт, для схем ТТЛ это 2-40 мВт, для КМОП 1-100 мкВт. В процессе переключения логических ИС средняяпотребляемая мощность выше средней статической мощности вследствие всплесков тока в переходных режимах. Это заметно в ИС с малым потреблением. для них обычно указывается потребляемая мощность в динамическом режиме при определенной тактовой частоте. снижение средней задержки логических схем сопровождается ростом потребляемой ими мощности, то находит применение параметр, называемый работой переключения (или добротностью), равный произведению средней мощности, потребляемой ИС, и средней задержки. Для первых поколений ИС этот показатель лежал в диапазоне 50-100 пДж. Последующие разработки позволили снизить его до 0,5-5 пДж.

Статическая помехоустойчивость - это наименьшее постоянное напряжение, которое, будучи добавлено (при самом неблагоприятном сочетании обстоятельств) к полезному входному сигналу, вызовет ошибку по всей последующей цепи логических схем. Статическая помеха наблюдается в тех случаях, когда относительно велико сопротивление проводников, подводящих к ИС напряжение питания. Падения напряжения на "земляной" шине, разные для разных ИС, будут суммироваться со входными сигналами и могут приводить к сбоям. Для исключения подобных ситуаций необходимо увеличивать сечение проводников, подводящих напряжения питания. для того, чтобы возник сбой, импульсная помеха, как правило, должна быть больше, чем статическая. Поэтому при одинаковой статической помехоустойчивости схемы с меньшей средней задержкой сильнее подвержены действию импульсных помех. Наименьшую помехоустойчивость имеют схемы ЭСЛ, В. В схемах ТТЛ помехоустойчивость выше благодаря наличию смещающих р-n-переходов на входах инверторов. Допустимая статическая помеха для этих схем равна 0,4-1,1 В. Для логических схем на КМОП-транзисторах величина U ст может достигать 2-3 В, что объясняется большими логическими перепадами напряжения в этих схемах.

Коэффициент объединения по входу - это максимальное число входов, которое может иметь логический элемент. Чаще всего коэффициент объединения по входу не превышает восьми, что отчасти определяется ограниченным числом выводов ИС.

Коэффициент разветвления по выходу, или нагрузочная способность, определяется числом схем этой же серии, входы которых могут быть присоединены к выходу данной схемы без нарушения ее работоспособности. Нагрузочная способность ИС в значительной степени определяется типом примененного в них инвертора. Для простейшего инвертора, состоящего из одного транзистора, коэффициент разветвления по выходу равен чаще всего 2-4. Для сложных инверторов нагрузочная способность достигает 10-20 и более. В схемах на основе КМОП-транзисторов входы последующих схем в статическом режиме практически не нагружают выходов предыдущих. Возможен большой коэффициент разветвления по выходу. в динамическом режиме емкости присоединенных входов затягивают переходный процесс и увеличивают ток, потребляемый от данной схемы.

Устойчивость против внешних воздействий характеризует возможность применения ИС при изменении температуры, влажности, радиации и т. д. В значительной степени этот параметр логических ИС определяется типом используемого корпуса. Что касается электрических цепей ИС, то наименее устойчивы к воздействию температуры интегральные схемы ЭСЛ. Более устойчивы схемы КМОП, ТТЛ. Наиболее широкий температурный диапазон для выпускаемых серийно отечественных ИС - от -60 до +l25°C. Для схем общепромышленного применения этот диапазон обычно определяется границами -10 и + 70 °С.Степень интеграции элементов ИСхарактеризует достигнутый при производстве этих ИС технологический уровень. Численное значение степени интеграции определяется округленным до большего целого числа значением десятичного логарифма числа элементов в одном кристалле. Надежность ИСмалой степени интеграции определяется в значительной мере отказами соединений между контактными площадками на кристалле и выводами корпуса. Для схем большой степени интеграции определяющими могут оказаться отказы элементов и соединений внутри самого кристалла. Интенсивность отказов ИС при хорошо отработанном технологическом процессе их изготовления может не превышать 10-7 ч-1, что примерно соответствует интенсивности отказов хороших дискретных транзисторов.