- •Verilog & system verilog

- •I бөлім. Жобалау

- •Сандық жүйелердің жүзеге асырылулар

- •Сандық жүйелерді жасауға арналған аппараттық құралдар

- •Сандық жүйелердің технологиялық шешімдері (конструктивы)

- •Сандық жүйелерді тестілеу және жасау технологиясы

- •1.5. Аппараттың сипатталу тілдері

- •1.5 1. SoC жобалауы мен верификациясының тілдері.

- •1.5.2. Tlm әдістемесінің негізі.

- •1.6. SoC жүзеге асыру технологиялары бойынша қорытындылар

- •1.7. SoC компоненттерінің hdl-модельдерін верификациялау және тестілеу

- •1.8. Бағдарламалық-аппараттық өнімдердің тестқа жарамдылығы

- •1.13 Сурет. Бағдарламалық-аппараттық комплекстың өмірлік циклының графигі

- •1.14 Сурет. Валидация және верификация процесстерінің әрекеттестігі

- •1.16 Сурет. Жобаны верификациялау ортасы

- •1.17 Сурет. Жобаның верификациясы үшін ассерцияларды қолдану технологиясы

- •1.18 Сурет. Жобаның верификация маршруты

- •1.10. Верификация инфрақұрылымының аналитикалық моделі

1.5. Аппараттың сипатталу тілдері

VHDL - ағылшынша VHSIC Hardware Discription Language аббревиатурасын білдіреді. Өз кезегінде, VHSIC - Very High Speed Integrated Circuit (жоғары жылдамдықты интегралды сұлбалар) бағдарламасының атауынан туындаған. Бұл бағдарлама, АҚШ-ның Қорғаныс Министрлігімен қаржыландырылып, жаңа заманғы жоғары жылдамдықтағы интегралды сұлбаларды дамытуды мақсат еткен. 1985 жылы тілдің алғашқы нұсқасы пайда болып, стандарттауды жүргізу үшін IEEE қоғамына берілді. 1987 жылы бұл тіл IEEE 1076-1987 стандарты ретінде бекітілді. Бес жылдан кейін, қайта қаралып, нәтижесінде 1076-93 жаңа нұсқасы қосымша мүмкіндіктер тізбегімен толықтырылды. Сол кезден бері, VHDL тілі электронды жүйелердің автоматты жобалауымен айналысатын мамандар арасында ең танымал тілге айналды. Алғашқы VHDL- қосымшасы 90-жылдардың басында пайда болды. Ал синтездеу үшін IEEE 1194 пакеті дайындалды. Практикада әрбір автоматты жобалау жүйесін өндіруші VHDL тілін қолдайды. Тіл сонымен қатар академиялық бағытқа ие, жоғары оқу орындарының зертханаларына да танымал.

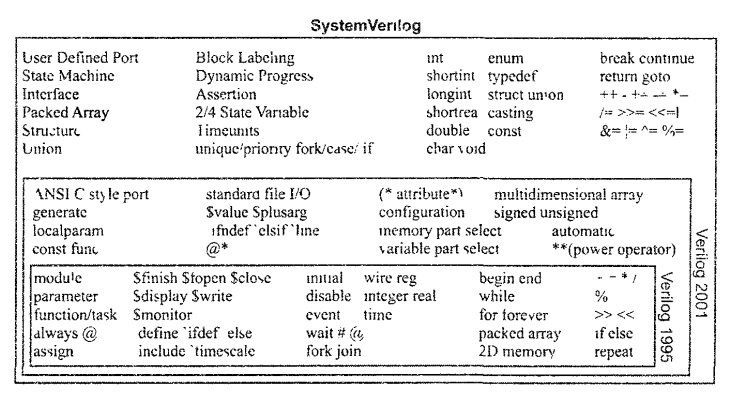

VHDL жүйеге әр түрлі деңгейде сипаттама береді. Ол азаймалы жобалаудың әдіснамасын орындайды, онда жүйе алдымен жоғары деңгейде сипатталады және модельдеу амалдарының көмегімен тестілеу жүргізіледі. Ары қарай кезеңделіп, нақты аппаратты жүзеге асырылуға негізделген құрылымдық сипаттамаға беріледі. VHDL тілі технологияның алуан түрлілігін жүзеге асыруға қатысты инвариантты болып табылады. Егер VHDL –да сипатталатын қандай да бір жоба нақты элекрондық технологияда өткізілген болса, онда берілген VHDL – сипаты жаңа технологиялардығы құрылғыларды жүзеге асырудың бастапқы түрі ретінде қолданылуы мүмкін. Verilog немесе Verilog HDL - аппаратураны сипаттау тілдері. 1985 жылы Филипп Мурби (Philip Moorby) сандық сұлбаны, модельдеуді және олардың жұмыс істеуін сипаттаудың қарапайым, көрнекті және әсерлі тәсілдеріне мұқтаж болғандықтан Verilog-ті ойлап тапқан. Бұл тіл Gateway Design Automation-нің, кейін Cadence Design Systems-тің жеке меншігіне айналады. Алғашқа Verilog стандарты 1995 жылы IEEE –да пайда болады. Тілдің соңғы толықтырулары 2005 жылы орындалды. Verilog EDA нарығында өз орны бар және ASIC –құрылғыларын жобалау өнеркәсіптерінде VHDL-ға қарағанда атақты болып келеді. 1.9-суретте Verilog-ге оның даму барысында енгізілген өзгерістердің құрылымдық сұлбасы көрсетілген. 1995 стандарты бойынша ядро ретінде оның базалық элементі алынған. Яғни осы жерде Verilog-жобасының негізгі массасы құрылады.

1.9 - сурет. System Verilog тілінің құрылымдық сұлбасы

Ары қарай, ядроның кеңейтілуіне жататын құрылымдармен толықтырылады, бұл құрылымдар 2001 жылдың Verilog 1364-2001 стандартымен орындалған. Және соңғы бөлімге - System Verilog тілін қалыптастырушы құрылымы кіреді. Бұл элементтер күрделі ирархиялық жобаларды жасауға арналған, сонымен қатар, мәліметтер мен Си тілінің операторларының қосымша типтерін сипаттайды. System Verilog жобалар көлемінің әр кез артып отырған уақыттарда пайда болып, жүйелік деңгейдің құрылғыларына сипаттама беру үшін жүзеге асырылды.