- •Введение

- •Архитектура микроконтроллера.

- •1.1 Структурная организация микроконтроллера i8051.

- •Назначение выводов микроконтроллера 8051.

- •1.2 Память

- •Память программ

- •Масочная память

- •Однократно программируемая память

- •Репрограммируемая память

- •Память с электрическим стиранием

- •Флэш-память

- •Память программ микроконтроллера 8051 (пзу).

- •Память данных

- •Статическая память

- •Память с электрическим стиранием

- •Память данных микроконтроллера 8051 (озу).

- •Специализированные ячейки флэш-памяти

- •Работа с внешней памятью микроконтроллера 8051.

- •1.3 Процессорное ядро

- •Регистр инструкций

- •Программный счетчик

- •Арифметико-логическое устройство

- •Арифметико-логическое устройство микроконтроллера 8051.

- •Регистры общего назначения

- •Регистр состояния

- •Регистр флагов (psw) микроконтроллера 8051.

- •Регистры ввода/вывода, специальные регистры.

- •1.4 Тактовый генератор

- •1.5 Система сброса

- •Источники сброса

- •1.6 Система прерываний

- •Алгоритм обработки прерываний

- •Система прерываний микроконтроллера 8051.

- •Регистр масок прерывания (ie).

- •Регистр приоритетов прерываний (ip).

- •Выполнение подпрограммы прерывания.

- •Вектора прерываний

- •1.7 Порты ввода/вывода организация ввода/вывода

- •Алгоритмы обмена данными

- •Асинхронный обмен

- •Симплексный обмен

- •Устройство портов.

- •Особенности электрических характеристик портов.

- •1.8 Таймеры-счетчики.

- •Таймеры-счетчики микроконтроллеров семейства 8051.

- •1.9 Последовательный порт микроконтроллера 8051.

- •Регистр управления/статуса приемопередатчика scon.

- •Функциональное назначение бит регистра управления/статуса приемопередатчика scon.

- •Скорость приема/передачи информации через последовательный порт.

- •Регистр управления мощностью pcon.

- •1.10 Режимы работы микроконтроллера 8051 с пониженным энергопотреблением.

- •Режим хх.

- •Режим внп.

- •1.11 Устройства ввода/вывода дискретных сигналов

- •1.12 Устройства ввода/вывода аналоговых сигналов

- •Интегрирующий преобразователь

- •Сигма-дельта преобразователь

- •1.13 Устройства обмена данными с другими микроконтроллерами

- •2. Программирование микроконтроллера

- •2.1 Система команд Мнемонические обозначения

- •Типы команд

- •Типы операндов

- •Группы команд.

- •Oбозначения, используемые при описании команд.

- •Команды пересылки данных микроконтроллера 8051.

- •Команды арифметических операций 8051.

- •Команды логических операций микроконтроллера 8051.

- •Команды операций над битами микроконтроллера 8051.

- •Команды передачи управления микроконтроллера 8051.

- •2.2 Язык ассемблера

- •Операнды

- •Операторы

- •Директивы ассемблера.

- •Командная строка

- •2.3 Особенности программирования микроконтроллеров общие особенности.

- •Типы инструментальных средств разработки и отладки программ для микроконтроллеров.

- •Внутрисхемные эмуляторы.

- •Классификация внутрисхемных эмуляторов.

- •Функциональные возможности внутрисхемных эмуляторов.

- •Достоинства и недостатки внутрисхемных эмуляторов.

- •Программные симуляторы.

- •Платы развития.

- •Отладочные мониторы.

- •Эмуляторы пзу.

- •Типичные функциональные модули средств разработки и отладки.

- •Отладчик.

- •Узел эмуляции микроконтроллера.

- •Эмуляционная память.

- •Подсистема точек останова.

- •Процессор точек останова.

- •Трассировщик.

- •Профилировщик.

- •Интегрированная среда разработки.

Устройство портов.

Каждый из портов содержит регистр-защелку (SFR P0 — SFR P3), выходную цепь и входной буфер.

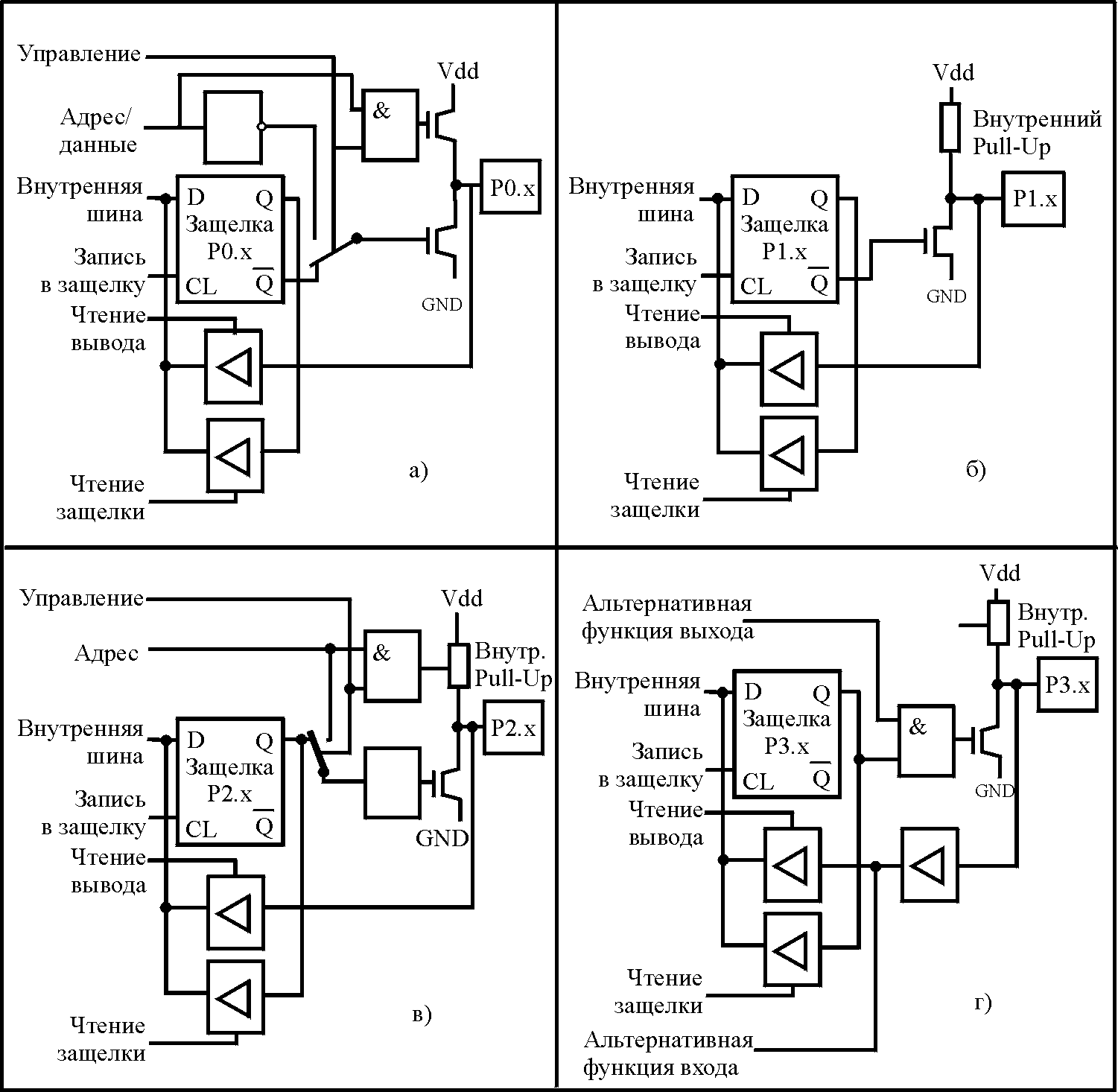

Рисунок 1.6 Устройство портов микроконтроллера 8051.

На рисунке изображены функциональные схемы регистров-защелок и буферов ввода-вывода всех портов микроконтроллера 8051. Каждый из разрядов регистра-защелки SFR является D-триггером, информация в который заносится с внутренней шины данных микроконтроллера по сигналу «Запись в SFR Pх» (х= 0, 1, 2, 3) от центрального процессорного элемента (CPU). С прямого выхода D-триггера информация мажет быть выведена на внутреннюю шину по сигналу «Чтение SFR Pх» от CPU, а с вывода микросхемы («из внешнего мира») по сигналу «Чтение выводов Pх». Одни команды активизируют сигнал «Чтение SFR PI», другие - «Чтение выводов РI».

Особенности электрических характеристик портов.

Выходные каскады триггеров SFR портов Р1 — РЗ выполнены на полевых транзисторах с внутренней нагрузкой, в то время как аналогичные каскады триггеров SFR P0—на транзисторах с открытым стоком. Каждая линия любого из портов может независимо использоваться как для ввода, так и для вывода информации (для линий портов P0 и Р2 это справедливо тогда, когда они не используются для обращения к внешней памяти).

Для перевода любой линии портов Р1 — РЗ в режим ввода информации необходимо в соответствующий разряд SFR занести 1. При этом выходной полевой транзистор отключается. Внутренний нагрузочный резистор как бы «подтягивает» потенциал вывода к напряжению питания, в то время как внешняя нагрузка может сделать его нулевым. Выходные каскады порта P0 имеют иную структуру. Нагрузочный полевой транзистор линии порта включен только тогда, когда порт выводит 1 при обращении к внешней памяти. В остальных случаях нагрузочный транзистор отключен. Таким образом, при работе в режиме обычного ввода-вывода информации (как, например, порт Р1) выходные каскады порт» P0 представляют собой ступени на транзисторах с открытым стоком. Запись 1 в соответствующий бит SFR отключает и второй транзистор, что приводит к тому, что вывод БИС оказывается под «плавающим» потенциалом. Это позволяет использовать линии порта P0 как выводы с высоко импедансным состоянием.

Поскольку выходные каскады портов P1 — P3 имеют внутреннюю нагрузку, при переводе в режим ввода информации они становятся источниками тока для микросхемы или транзистора, нагруженных на данный.

1.8 Таймеры-счетчики.

Большинство задач управления решаются в реальном времени. При этом микроконтроллер должен в определенные моменты времени выполнять определенные действия с объектом. Типовыми задачами такого плана считаются:

подсчет числа импульсов сигнала за фиксированный интервал времени;

формирование интервалов времени определенной длительности;

формирование периодических сигналов заданной частоты;

формирование широтно-модулированных сигналов;

формирование временных задержек;

измерение времени и др.

Любая из этих задач может выполнена программно, но в этом случае процессорное ядро вынуждено заниматься только подсчетом времени и все остальные задачи откладываются. Для разгрузки процессорного ядра от такой неэффективной работы микроконтроллеры снабжаются специальными схемами, получившими название таймеры-счетчики. Они могут быть использованы для подсчета тактовых импульсов фиксированной частоты либо для подсчета любых внешних импульсных сигналов. Считается, что в первом случае устройство выполняет функции таймера, во втором – счетчика.

В современных микроконтроллерах, кроме простейших функций подсчета импульсов, на таймеры-счетчики возлагают дополнительные функции:

функция захвата IC (Input Capture),

функция выхода сравнения OC (Output Compare),

широтно-импульсной модуляции PWM (Pulse-Width Modulation).

В режиме захвата содержимое таймера-счетчика в момент времени, задаваемый каким-либо внешним событием на входе захвата, запоминается в регистре данных и становится доступным для процессорного ядра. Одновременно формируется запрос на прерывание, сообщающий программе о готовности данных.

В режиме сравнения содержимое таймера-счетчика сравнивается с некоторым фиксированным числом, хранящимся в одном из регистров микроконтроллера. В момент равенства данных формируется сигнал на выходе захвата.

В режиме широтно-импульсной модуляции таймер-счетчик формирует последовательность импульсов определенной частоты, в которой длительность импульсов может быть изменена программно от 0 до периода последовательности.

Количество таймеров-счетчиков, интегрируемых на кристалл микроконтроллера, может быть различно. Для регулирования частоты входного сигнала таймеры снабжаются предделителями (Prescaler).