- •1.Закон Мура в електроніці.

- •2. Основні тенденції розвитку комп’ютерної електроніки.

- •3. Продуктивність комп’ютерних систем та методи їх підвищення.

- •4. Фізичні обмеження в елементах комп’ютерів.

- •5. Інформація, інформаційний процес, вимоги до інформації.

- •6. Носії інформації та їх класифікація.

- •7. Сигнали та їх класифікації

- •8. Математичне представлення сигналів. Типи сигналів

- •9. Закони для булевих операцій.

- •10. Аналітичне представлення булевих функцій.

- •11. Арифметичні операції над числами, представлених в додаткових кодах.

- •12. Основні булеві функції Функції:

- •13. Способи задання булевих функцій

- •14. Буливі функції однієї змінної

- •15. Типи логічних елементів

- •16Аналітичне представлення булевих операцій

- •17. Елементи, вузли, пристрої кс

- •18. Потенціальні та імпульсні сигнали

- •Позитивний.

- •Негативний.

- •19.Класифікація елементів в комп’ютері

- •20. Імс та їх класифікація

- •26. Основні параметри цімс

- •27.Характеристики мікросхем

- •28.Швидкодія логічних мікросхем

- •29.Зп пристрої та їх класифікація

- •30. Функціональна схема ram. Статичні озп

- •32. Динамічні озп. Класифікація динамічних озп

- •36Елемент пам’яті на мнон транзисторі

- •37. Елемент пам’яті на лізмон транзисторі

- •38.Тригери та їх різновиди

- •39.Синхронізація роботи тригерів

- •40. Схемотехнічні принципи побудови тригерів. Jk тригери

- •41.Д тригери і т тригери

- •42. Лічильники імпульсів.

- •43. Асинхронні і синхронні лічильники

- •44. Дешифратори. Класифікація, основні характеристики.

- •45. Мультиплексори

- •46. Демультиплексори

- •47. Архітектура комп’ютерів:. Прінстонська і Гарвардська

- •48. Основні принципи Нейманівської архітектури є 2 блоки формування цих принципів.

- •49. Класифікація архітектур обчислювальних систем

- •50. Класифікація архітектур за взаємодією цп, пп, оп.

- •51. Класифікація архітектур за взаємодією потоків команд і даних

- •52. Способи вдосконалення архітектур

- •53. Мікропроцесор та його функції

- •54. Основні параметри мп.

- •55. Характеристика мп 80386 та 80486.

- •56.Характеристика мп типу Pentium

- •57. Характеристика мп типу Pentium Pro

- •58. Характеристика мп ммх та Pentium II

- •59.Характеристика мп Pentium III

- •60.Технологія нт.

- •61. Характеристика мп типу Celeron.

- •62.Характеристика мп Pentium 4.

- •63. Технологія гіперконвеєрної обробки.

- •64.Характеристика мп типу risk.

- •65. Характеристика мп Over Drive.

- •66. Компоненти що входять до складу мп.

- •67. Операційна та інтерфейс на частини мп.

- •68. Функціональна схема пу мп.

- •69. Функціональна схема алп.

- •Мікропроцесорна пам'ять.

- •71. Типи регістрів мпп.

- •72. Універсальні регістри.

- •73. Сегментні регісти.

- •74. Регістри зміщень.

- •75. Регістри прапорців.

- •76. Управляючі прапорці.

- •77. Призначення інтерфейсної частини мп.

- •78. Інтерфейси евм.

- •79. Шини розширень.

- •80. Локальні шини.

- •81. Периферійні шини.

- •82.Універсальні послідовні шини.

- •83. Послідовна шина usb.

- •84. Станадарт ieee(Fire Wire).

- •85. Послідовний інтерфейс sata.

- •86. Послідовний інтерфейс sas.

- •87. Сімейство послідовних інтерфейсів pci Express.

- •88. Безпровідні інтерфейси.

- •89. Інтерфейс IrDa.

- •90. Інтерфейс Bluetooth.

- •91.Інтерфейс wusb.

- •92.Сімейство інтерфейсів wi fi.

- •93. Інтерфейс wi Max.

- •94. Синхронний та асинхронний sr-тригери.

- •95. Асинхронний сумуючий лічильник.

- •99. Часові характеристики цифрового сигналу. Синхроімпульси.

- •100. Архітектура, як інтерфейс між рівнями фізичної підсистеми.

- •101. Лічильники. Логічна стуктура лічильника. Режими роботи.

- •102. Шифратори:характеристика,класифікація.

- •103. Способи підвищення продуктивності кс.

- •104. Тегова пам'ять. Дискриптори.

- •105. Домен-як адресний простір.

- •106. Ключ на біп- транзисторі.

- •107. Вхідна характеристика логічного елемента.

- •108. Вихідна характеристика логічного елемента.

- •109. Передаточна характеристика логічного елемента.

- •110. Динамічні параметри логічних елементів.

- •111. Швидкодія логічних мікросхем.

- •112. Вимірювання часових параметрів сигналів.

40. Схемотехнічні принципи побудови тригерів. Jk тригери

Має

2 інформаційні входи: J і K. Подібно до

SR-тригера це входи, установки тритера

в стан 1 або 0.

Має

2 інформаційні входи: J і K. Подібно до

SR-тригера це входи, установки тритера

в стан 1 або 0.

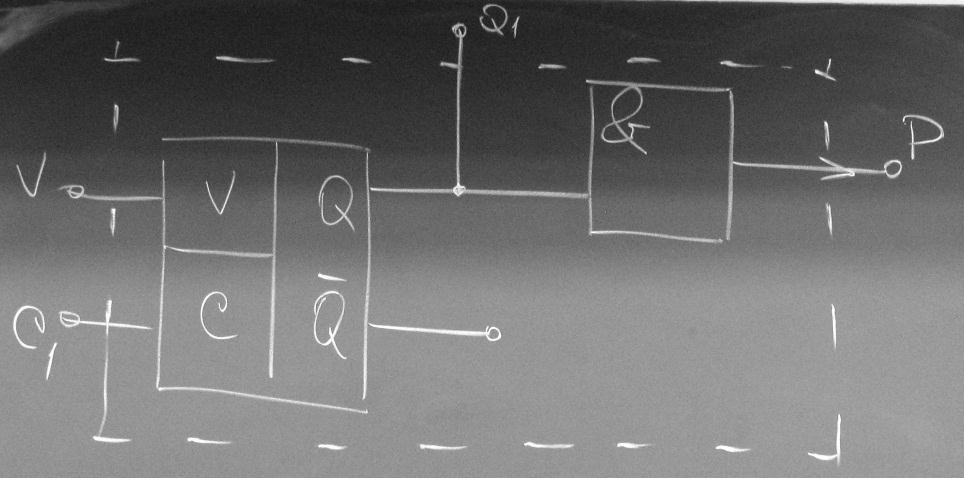

41.Д тригери і т тригери

Однак на відміну від SR-тригера в JK-тригера наявність j=k=1 приводить до переведення Q виходу

D-Тритер (тригер затримки)

При поступанні синхросигналу на вхід ЦЕ встановлюється стан, що відповідає потенціалу на вході ДЕ. Особливістю є те, що вихідний сигнал змінюється не зразу після зміни вхідного сигналу а лише з приходом синхросигналу, тобто із затримкою на один період імпульсів синхронізації. Синхронізація цього тригеру може здійснюватися імпульсом або фронтом імпульсу.

T-тритер.

Змінює свій стан по фронту імпульсу на вході ЦЕ. Однак такий тригер крім синхровходу ЦЕ такий тригер має підготовчий вхід ТЕ. Сигнал по цьому входу дозволяє, якщо Т-рівне одиниці, або забороняє(якщо ТЕ рівне нулю) спрацювання тритерів від фронту імпульсів, що поступають на вхід ЦЕ. Аналіз при Т рівне одиниці показує, що відповідний фронт сигналу на вході ЦЕ переводить тригер в протилежний стан.

Частота зміни потенціалу на виходу Т тригера в 2 рази менша частоти імпульсів на вході ЦЕ. Ця

властивість дозволяє будувати на цьому тригері двійкові лічильники.

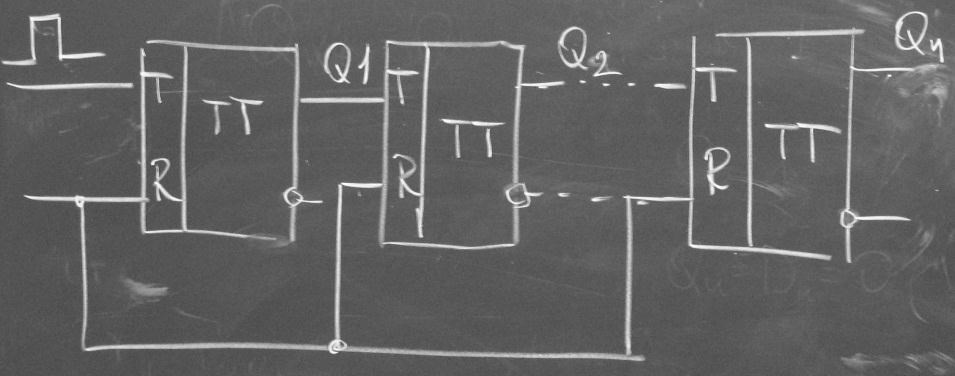

42. Лічильники імпульсів.

Лічильник у загальному випадку являє собою зв’язаний ланцюг T-тригерів, які утворюють пам’ять із заданим числом станів.

–

кубічна структура лічильника.

–

кубічна структура лічильника.

Розрядність лічильника рівна числу T-тригерів.

Кожний вхідний імпульс змінює стан лічильника, який зберігається до наступного сигналу. Значення виходу тригерів лічильники відображають результат лічби у прийнятій системі числення.

Основне застосування лічильників:

Утворення послідовності адрес команд програми.

Підрахунок числа циклів при виконанні операцій ділення, множення та зсуву.

Одержання сигналів мікрооперацій та синхронізацій.

Аналогом цифрового перетворення. Побудова електронних таймерів. Характеристика:

Модуль личби.

Ємність лічби.

Модуль лічби визначає число станів лічильника. Тоді модуль двійкового N-розрядного лічильника визначається цілим степенем двійки M 2n

Особливістю лічильника є те, що після лічби лічильник повертається у попередній стан.

Ємність лічби. Визначає максимальну кількість вхідних імпульсів, яку може зафіксувати лічильник

при одному циклі роботи.

При роботі лічильника використовується 3 режими роботи:

Керування.

Накопичення.

Ділення.

Лічильники класифікують за такими 4. Способом організації між розрядних ознаками: зв’язків.

Способом кодування. a. З послідовним.

Позиційні. b. З наскрізним.

Не позиційні. c. З паралельним.

Модулем лічби. d. Комбінованим переносами.

Напрямом лічби. 5. Елементним базисом.

Прості. a. Потенціальні.

Реверсивні. b. Імпульсні.

Потенціально-імпульсні.

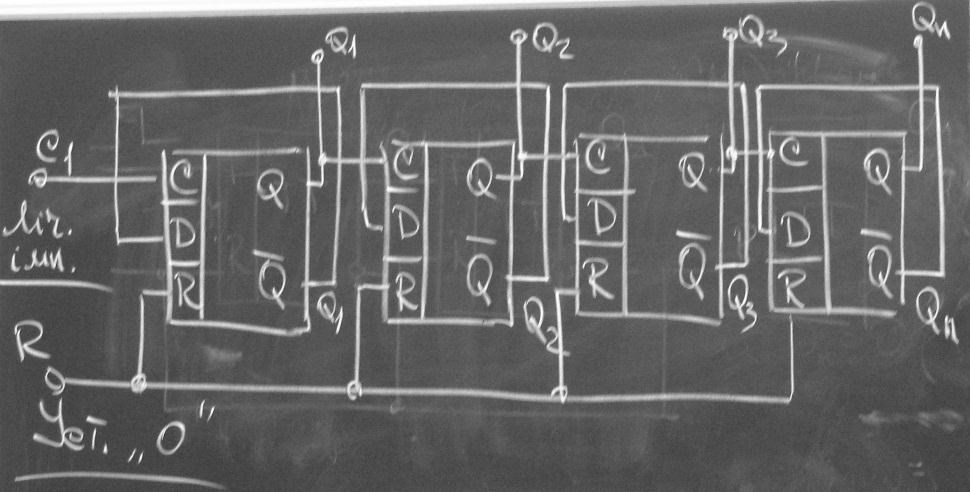

43. Асинхронні і синхронні лічильники

Асинхронний сумуючий лічильник виконують на тригерах довільного типу. Переважно використовують JK або D-тригери в лічильному режимі.

Найпростіший чотирьох розрядний лічильник на D-тригерах скадаєтсья із з’єднаних послідовно чотирьох лічильних тригерів таким чином щоб вихід кожного тригера з’єднаний з входом наступного. При надходженні лічильних імпульсів на вхід C тригери будуть змінювати свій стан. Для преведення лічильника у початковий стан використовуються сигнал скидання R, що поступає одночасно на всі входи R тригерів.

–

схема асинхронного сумуючого лічильника.

–

схема асинхронного сумуючого лічильника.

Для побудови асинхронного реверсивного лічильника, який може функціонувати в режимі віднімання достатньо замінити виходи _____. В цьому випадку при надходження імпульсу скидання R на всіх виходах лічильника встановляться одиничні рівні. А при надходженні лічильників на вхід ЦЕ1 тригери лічильника будуть змінювати свої стани.

Для побудови асинхронного реверсивного лічильника можна за допомогою логічної схеми забезпечити подачу сигналів з інверсного виходу Q при сумуванні або з прямого виходу Q при відніманні від попереднього тригера на лічильний вхід наступного тригера.

Синхронні лічильники. Він побудований на лічильних тригерах і логічних елементах.

Вхід ВІ – сигнал дозволу.

Схема реалізована підключенням входу __ до лічильного входу тригера. А для формування сигналу переносу ПЕ використано логічний добуток сигналу розділення лічби ВІ і вихидного сигналу К’Ю. Тобто P V Q

Переключення тригера відбувається по додатному перепаду сигналу на вході ЦЕ тригера та при наявності сигналу дозволу на вході ВІ. При цьому на виході тригера К’Ю і виході переносу встановлюється логічні одиниці. При від’ємному перепаді сигналу на вході ЦЕ1 стан тригера не змінюється. Чергове переключення тригера пройде лише при наступному додатному препаду імпульсу на вході ЦЕ і при наявності дозвольного імпульсу на вході ВІ.