- •1.Закон Мура в електроніці.

- •2. Основні тенденції розвитку комп’ютерної електроніки.

- •3. Продуктивність комп’ютерних систем та методи їх підвищення.

- •4. Фізичні обмеження в елементах комп’ютерів.

- •5. Інформація, інформаційний процес, вимоги до інформації.

- •6. Носії інформації та їх класифікація.

- •7. Сигнали та їх класифікації

- •8. Математичне представлення сигналів. Типи сигналів

- •9. Закони для булевих операцій.

- •10. Аналітичне представлення булевих функцій.

- •11. Арифметичні операції над числами, представлених в додаткових кодах.

- •12. Основні булеві функції Функції:

- •13. Способи задання булевих функцій

- •14. Буливі функції однієї змінної

- •15. Типи логічних елементів

- •16Аналітичне представлення булевих операцій

- •17. Елементи, вузли, пристрої кс

- •18. Потенціальні та імпульсні сигнали

- •Позитивний.

- •Негативний.

- •19.Класифікація елементів в комп’ютері

- •20. Імс та їх класифікація

- •26. Основні параметри цімс

- •27.Характеристики мікросхем

- •28.Швидкодія логічних мікросхем

- •29.Зп пристрої та їх класифікація

- •30. Функціональна схема ram. Статичні озп

- •32. Динамічні озп. Класифікація динамічних озп

- •36Елемент пам’яті на мнон транзисторі

- •37. Елемент пам’яті на лізмон транзисторі

- •38.Тригери та їх різновиди

- •39.Синхронізація роботи тригерів

- •40. Схемотехнічні принципи побудови тригерів. Jk тригери

- •41.Д тригери і т тригери

- •42. Лічильники імпульсів.

- •43. Асинхронні і синхронні лічильники

- •44. Дешифратори. Класифікація, основні характеристики.

- •45. Мультиплексори

- •46. Демультиплексори

- •47. Архітектура комп’ютерів:. Прінстонська і Гарвардська

- •48. Основні принципи Нейманівської архітектури є 2 блоки формування цих принципів.

- •49. Класифікація архітектур обчислювальних систем

- •50. Класифікація архітектур за взаємодією цп, пп, оп.

- •51. Класифікація архітектур за взаємодією потоків команд і даних

- •52. Способи вдосконалення архітектур

- •53. Мікропроцесор та його функції

- •54. Основні параметри мп.

- •55. Характеристика мп 80386 та 80486.

- •56.Характеристика мп типу Pentium

- •57. Характеристика мп типу Pentium Pro

- •58. Характеристика мп ммх та Pentium II

- •59.Характеристика мп Pentium III

- •60.Технологія нт.

- •61. Характеристика мп типу Celeron.

- •62.Характеристика мп Pentium 4.

- •63. Технологія гіперконвеєрної обробки.

- •64.Характеристика мп типу risk.

- •65. Характеристика мп Over Drive.

- •66. Компоненти що входять до складу мп.

- •67. Операційна та інтерфейс на частини мп.

- •68. Функціональна схема пу мп.

- •69. Функціональна схема алп.

- •Мікропроцесорна пам'ять.

- •71. Типи регістрів мпп.

- •72. Універсальні регістри.

- •73. Сегментні регісти.

- •74. Регістри зміщень.

- •75. Регістри прапорців.

- •76. Управляючі прапорці.

- •77. Призначення інтерфейсної частини мп.

- •78. Інтерфейси евм.

- •79. Шини розширень.

- •80. Локальні шини.

- •81. Периферійні шини.

- •82.Універсальні послідовні шини.

- •83. Послідовна шина usb.

- •84. Станадарт ieee(Fire Wire).

- •85. Послідовний інтерфейс sata.

- •86. Послідовний інтерфейс sas.

- •87. Сімейство послідовних інтерфейсів pci Express.

- •88. Безпровідні інтерфейси.

- •89. Інтерфейс IrDa.

- •90. Інтерфейс Bluetooth.

- •91.Інтерфейс wusb.

- •92.Сімейство інтерфейсів wi fi.

- •93. Інтерфейс wi Max.

- •94. Синхронний та асинхронний sr-тригери.

- •95. Асинхронний сумуючий лічильник.

- •99. Часові характеристики цифрового сигналу. Синхроімпульси.

- •100. Архітектура, як інтерфейс між рівнями фізичної підсистеми.

- •101. Лічильники. Логічна стуктура лічильника. Режими роботи.

- •102. Шифратори:характеристика,класифікація.

- •103. Способи підвищення продуктивності кс.

- •104. Тегова пам'ять. Дискриптори.

- •105. Домен-як адресний простір.

- •106. Ключ на біп- транзисторі.

- •107. Вхідна характеристика логічного елемента.

- •108. Вихідна характеристика логічного елемента.

- •109. Передаточна характеристика логічного елемента.

- •110. Динамічні параметри логічних елементів.

- •111. Швидкодія логічних мікросхем.

- •112. Вимірювання часових параметрів сигналів.

38.Тригери та їх різновиди

Три́гер (англ. trigger, flip-flop) — електронна логічна схема, яка має два стійкі стани, в яких може перебувати доки не зміняться відповідним чином сигнали керування. Напруги і струми на виході тригера можуть змінюватися стрибкоподібно.

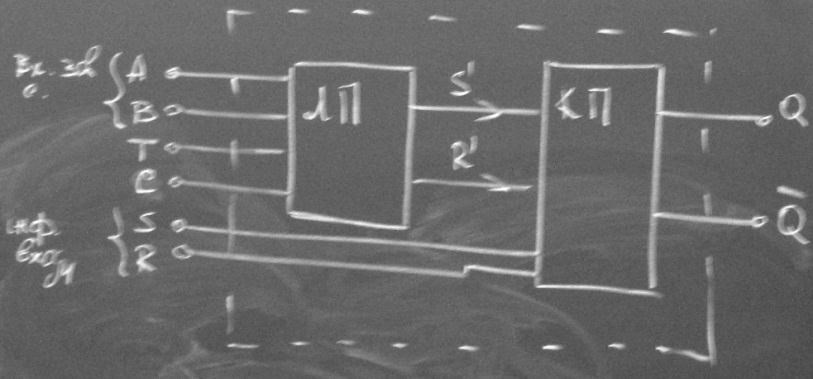

В арифметичних і логічних пристроях для збереження інформації найчастіше використовують тригери – пристрої з двома стійкими станами по виходу, які містять елементарну запам’ятовувальну комірку (бістабільна схема БС) і схему керування (СК). Схема керування перетворює інформацію, яка надходить, на комбінацію сигналів, що діють безпосередньо на входи елементарної запам’ятовувальної комірки. Для забезпечення надійного перемикання в точках А для деяких тригерів повинні бути кола затримки. З цією метою можуть використовуватися запам'ятовувальні елементи на основі БС того ж типу, що вже є у тригері. Схему такого тригера називають схемою типу M-S (master-slave), оскільки стан однієї БС, яку називають веденою, повторює стан додаткової БС, яку називають ведучою.

Тригери широко використовуються для формування імпульсів, у генераторах одиничних сигналів, для побудови подільників частоти, лічильників, перерахункових пристроїв, регістрів, суматорів, у пристроях керування тощо.

У більшості серій інтегральних елементів містяться тригери різних типів, у тому числі універсальні.

Класифікація тригерів

• за способом організації логічних зв’язків розрізняють тригери з запуском (RS-тригери); з лічильним входом (Т-тригери); тригери затримки (D-тригери); універсальні (JK-тригери); комбіновані (наприклад, RST-, JKRS-, DRS-тригери).

• за способом запису інформації тригери поділяють на несинхронізовані (асинхронні, нетактові) і синхронізовані (тактові).

• за кількістю інформаційних входів тригери можуть бути з одним, двома та багатьма входами.

• за видом вихідних сигналів тригери поділяються на статичні і динамічні. Статичні тригери – тригери, в яких вихідні сигнали в стійких станах залишаються незмінними в часі. Динамічні тригери – тригери, в яких вихідні сигнали в стійких станах змінюються в часі.

• за способом запам’ятовування інформації тригери можуть бути з логічною і фізичною організацією пам’яті. Перші виконують на логічних елементах І, АБО, НІ, І-НІ, АБО-НІ, І-АБО-НІ і т.д., а другі є елементами запам’ятовувальних пристроїв, у яких використовують нелінійні властивості матеріалів або нелінійні вольт-амперні характеристики компонентів.

39.Синхронізація роботи тригерів

Тригер – це такий пристрій, вихід якого може перебувати в двох стійких станах, стан яких може змінюватись під дією тільки зовнішніх сигналів.

В загальному випадку це пристрої, що складаються у комірки пам’яті і логічного пристрою управління, що перетворює вхідну інформацію в комбінацію вхідних сигналів під впливом яких комірка пам’яті приймає один-двох стійких станів. Тригер складається з:

Інформаційні сигнали поступають на входи А і В і перетворюються логічним пристроєм(ЛП) на внутрішні входи ЕСШТРИХ і ЕРШТРИХ. Але процес перетворення інформаційних сигналів здійснюється при дії сигналів, що подаються на вхід ТЕ та вхід синхронізації ЦЕ. При чому вхід ТЕ – дозвільний, а вхід ЦЕ забезпечує тактовий прийом інформації.

Тригери із входом ЦЕ називаються синхронними, а при відсутності його називаються асинхронними. Зміна стану асинхронного тригера відбувається зразу ж після відповідної зміни потенціалів на його інформаційних входах А і В. В синхронному тригері зміна стану може пройти лише момент наявності відповідного сигналу на вході ЦЕ. Синхронізація може відбуватися або фронтом(перепадом потенціалу) або повним імпульсом. У першому випадку сигнали на інформаційних входах здійснюють вплив на стан тригера лише при дозвільному потенціалі на вході ЦЕ. В другому випадку вплив інформаційних сигналів проявляється лише у момент зміни потенціалу на вході ЦЕ, тобто при переході його від одиниці до нуля або від нуля до одиниці. Для універсальних тригерів забезпечений режим роботи в синхронному і асинхронному режимі.

По способу організації логічних зв’язків розрізняють тригери з роздільною установкою:

В стані 0 і 1. Це так званий RC тригер.

З лічильним входом.

Універсальний. З роздільною установкою станів 0 і 1. 4. З сприйманням інформації із одного входу. D тригер.

Універсальні, з керованим прийманням інформації з одного входу(DV-тригери).

Комбіновані (RC-тригери, JKRS, DRS).