- •1.Закон Мура в електроніці.

- •2. Основні тенденції розвитку комп’ютерної електроніки.

- •3. Продуктивність комп’ютерних систем та методи їх підвищення.

- •4. Фізичні обмеження в елементах комп’ютерів.

- •5. Інформація, інформаційний процес, вимоги до інформації.

- •6. Носії інформації та їх класифікація.

- •7. Сигнали та їх класифікації

- •8. Математичне представлення сигналів. Типи сигналів

- •9. Закони для булевих операцій.

- •10. Аналітичне представлення булевих функцій.

- •11. Арифметичні операції над числами, представлених в додаткових кодах.

- •12. Основні булеві функції Функції:

- •13. Способи задання булевих функцій

- •14. Буливі функції однієї змінної

- •15. Типи логічних елементів

- •16Аналітичне представлення булевих операцій

- •17. Елементи, вузли, пристрої кс

- •18. Потенціальні та імпульсні сигнали

- •Позитивний.

- •Негативний.

- •19.Класифікація елементів в комп’ютері

- •20. Імс та їх класифікація

- •26. Основні параметри цімс

- •27.Характеристики мікросхем

- •28.Швидкодія логічних мікросхем

- •29.Зп пристрої та їх класифікація

- •30. Функціональна схема ram. Статичні озп

- •32. Динамічні озп. Класифікація динамічних озп

- •36Елемент пам’яті на мнон транзисторі

- •37. Елемент пам’яті на лізмон транзисторі

- •38.Тригери та їх різновиди

- •39.Синхронізація роботи тригерів

- •40. Схемотехнічні принципи побудови тригерів. Jk тригери

- •41.Д тригери і т тригери

- •42. Лічильники імпульсів.

- •43. Асинхронні і синхронні лічильники

- •44. Дешифратори. Класифікація, основні характеристики.

- •45. Мультиплексори

- •46. Демультиплексори

- •47. Архітектура комп’ютерів:. Прінстонська і Гарвардська

- •48. Основні принципи Нейманівської архітектури є 2 блоки формування цих принципів.

- •49. Класифікація архітектур обчислювальних систем

- •50. Класифікація архітектур за взаємодією цп, пп, оп.

- •51. Класифікація архітектур за взаємодією потоків команд і даних

- •52. Способи вдосконалення архітектур

- •53. Мікропроцесор та його функції

- •54. Основні параметри мп.

- •55. Характеристика мп 80386 та 80486.

- •56.Характеристика мп типу Pentium

- •57. Характеристика мп типу Pentium Pro

- •58. Характеристика мп ммх та Pentium II

- •59.Характеристика мп Pentium III

- •60.Технологія нт.

- •61. Характеристика мп типу Celeron.

- •62.Характеристика мп Pentium 4.

- •63. Технологія гіперконвеєрної обробки.

- •64.Характеристика мп типу risk.

- •65. Характеристика мп Over Drive.

- •66. Компоненти що входять до складу мп.

- •67. Операційна та інтерфейс на частини мп.

- •68. Функціональна схема пу мп.

- •69. Функціональна схема алп.

- •Мікропроцесорна пам'ять.

- •71. Типи регістрів мпп.

- •72. Універсальні регістри.

- •73. Сегментні регісти.

- •74. Регістри зміщень.

- •75. Регістри прапорців.

- •76. Управляючі прапорці.

- •77. Призначення інтерфейсної частини мп.

- •78. Інтерфейси евм.

- •79. Шини розширень.

- •80. Локальні шини.

- •81. Периферійні шини.

- •82.Універсальні послідовні шини.

- •83. Послідовна шина usb.

- •84. Станадарт ieee(Fire Wire).

- •85. Послідовний інтерфейс sata.

- •86. Послідовний інтерфейс sas.

- •87. Сімейство послідовних інтерфейсів pci Express.

- •88. Безпровідні інтерфейси.

- •89. Інтерфейс IrDa.

- •90. Інтерфейс Bluetooth.

- •91.Інтерфейс wusb.

- •92.Сімейство інтерфейсів wi fi.

- •93. Інтерфейс wi Max.

- •94. Синхронний та асинхронний sr-тригери.

- •95. Асинхронний сумуючий лічильник.

- •99. Часові характеристики цифрового сигналу. Синхроімпульси.

- •100. Архітектура, як інтерфейс між рівнями фізичної підсистеми.

- •101. Лічильники. Логічна стуктура лічильника. Режими роботи.

- •102. Шифратори:характеристика,класифікація.

- •103. Способи підвищення продуктивності кс.

- •104. Тегова пам'ять. Дискриптори.

- •105. Домен-як адресний простір.

- •106. Ключ на біп- транзисторі.

- •107. Вхідна характеристика логічного елемента.

- •108. Вихідна характеристика логічного елемента.

- •109. Передаточна характеристика логічного елемента.

- •110. Динамічні параметри логічних елементів.

- •111. Швидкодія логічних мікросхем.

- •112. Вимірювання часових параметрів сигналів.

32. Динамічні озп. Класифікація динамічних озп

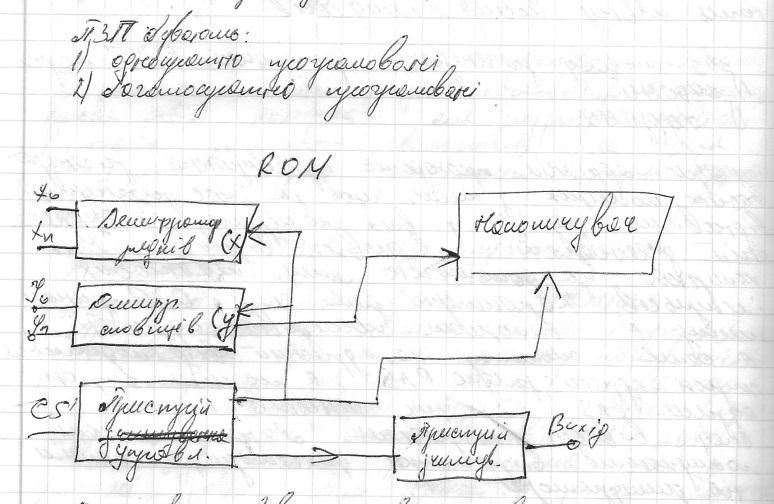

Функціональна схема ROM

Масочні та програмовані ПЗП

Репрограмовані ПЗП

36Елемент пам’яті на мнон транзисторі

Пам’ять на МНОН-транзисторах.(Метал Нітрид Окисил Напівпровідник)

струмопроходження вздовж каналу буде суттєво залежати від наявності чи відсутності локалізованого заряду на границі SiO2 SiN4.

Програмуванням МНОН-транзистора називається процес формування заряду в під затворному діелектрику. Для цього до затвору N-канального транзистора прикладають додатній імпульс напруги амплітудою близько 20 Вольт. Під дією електричного утворення(поля) електрони тунелюють з підкладки через тонкий шар SiO2 на межу SiN4 SiO2, де вони захоплюються локальними пастками.

Таким чином формується негативний заряд, який виконує функцію носія інформації. Наявність заряду означає 0 а його відсутність логічну 1. Таким чином стоково-затворна характеристика має вигляд при наявності заряду і при відсутності заряду:

_____ заряд екранує дію позитивної напруги на затворі і відповідно підвищує порогову напругу на стільки, що робочий сигнал відкрити транзистор не може. Кожному новому запису передує стирання інформації(заряду). Число перезаписів 104 106раз. Програмований стан транзистора зберігається роками. В режимі зчитування на затвор подають напругу, значення якої лежить між двома граничними рівнями: якщо записана логічна 1 то транзистор відкриється, якщо 0 то транзистор закритий. Таким чином залежно від транзистора при подачі на його затвор напруги зчитування(по шині xi в розрядній шині y j струм або протікає або ні.

Підсилювач зчитування трансформує стан розрядної шини у вихідну напругу високого або низького рівня(відповідно струм протікає або ні). Якщо транзистор має локалізований заряд(стан 0) то для переходу в 1 накопичений заряд витискують з під затвора негативним імпульсом амплітудою порядку 40 Вольт, який подається на затвор. Це процес стирання інформації

37. Елемент пам’яті на лізмон транзисторі

Елементи пам’яті на ЛІЗМОН-транзисторах(Лавинно-Інжектований Заряд).

Прикладом такого є пряме зміщення на PN-переході.

Структура ЛІЗМОН-транзистора з одним Структура ЛІЗМОН-транзистора з двома

Металевий затвор розміщений в товщині діелектрика і в нього відсутні зовнішні виведення, тому його називають плаваючим. При наявності заряду на плаваючому затворі(ПЗ) утворюється провідний канал і транзистор відкривається, що відповідає запису логічної одиниці. При відсутності заряду транзистор закривається, тобто є логічний 0. У випадку двозатворного транзистора в режимі програмування на витік – стік подається позитивний імпульс амплітудою 25 Вольт. В результаті PNпереходи виявляються зворотньо-міщеними і виникає процес лавинної інжекції. Частина електронів в результаті тунелювання попадає на плаваючий затвор і в результаті накладання на плаваючий затвор негативного заряду порогова напруга зміщується в область більш високого рівня, що відповідає запису логічного нуля. Відсутність зарядів електродів на плаваючому затворі відповідає запису логічної одиниці. Стирання інформації здійснюють шляхом витіснення заряду ПЗ. Цю операцію здійснюють двома методами:

Імпульсом напруги, що подається на затвор. Такі елементи мають позначення ЗПЗП-ЕС.

За допомогою ультрафіолетового випромінювання крізь вікно у мікросхемі.

У першому випадку накопичені в ПЗ електрони витісняються у підкладку електричним полем, що приводить до відновлення стану 1. У випадку 2 електрони розсмоктуються з ПЗ у підкладку за рахунок теплового руху від УФ джерела. Режим зчитування виконується аналогічно як і у МНОН-транзисторів.