- •1.Закон Мура в електроніці.

- •2. Основні тенденції розвитку комп’ютерної електроніки.

- •3. Продуктивність комп’ютерних систем та методи їх підвищення.

- •4. Фізичні обмеження в елементах комп’ютерів.

- •5. Інформація, інформаційний процес, вимоги до інформації.

- •6. Носії інформації та їх класифікація.

- •7. Сигнали та їх класифікації

- •8. Математичне представлення сигналів. Типи сигналів

- •9. Закони для булевих операцій.

- •10. Аналітичне представлення булевих функцій.

- •11. Арифметичні операції над числами, представлених в додаткових кодах.

- •12. Основні булеві функції Функції:

- •13. Способи задання булевих функцій

- •14. Буливі функції однієї змінної

- •15. Типи логічних елементів

- •16Аналітичне представлення булевих операцій

- •17. Елементи, вузли, пристрої кс

- •18. Потенціальні та імпульсні сигнали

- •Позитивний.

- •Негативний.

- •19.Класифікація елементів в комп’ютері

- •20. Імс та їх класифікація

- •26. Основні параметри цімс

- •27.Характеристики мікросхем

- •28.Швидкодія логічних мікросхем

- •29.Зп пристрої та їх класифікація

- •30. Функціональна схема ram. Статичні озп

- •32. Динамічні озп. Класифікація динамічних озп

- •36Елемент пам’яті на мнон транзисторі

- •37. Елемент пам’яті на лізмон транзисторі

- •38.Тригери та їх різновиди

- •39.Синхронізація роботи тригерів

- •40. Схемотехнічні принципи побудови тригерів. Jk тригери

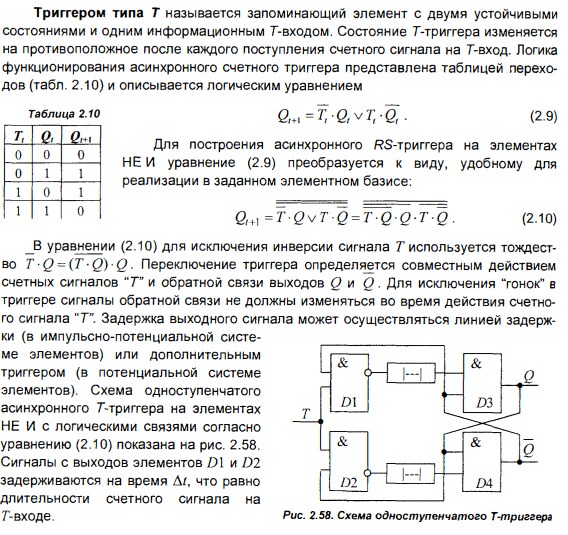

- •41.Д тригери і т тригери

- •42. Лічильники імпульсів.

- •43. Асинхронні і синхронні лічильники

- •44. Дешифратори. Класифікація, основні характеристики.

- •45. Мультиплексори

- •46. Демультиплексори

- •47. Архітектура комп’ютерів:. Прінстонська і Гарвардська

- •48. Основні принципи Нейманівської архітектури є 2 блоки формування цих принципів.

- •49. Класифікація архітектур обчислювальних систем

- •50. Класифікація архітектур за взаємодією цп, пп, оп.

- •51. Класифікація архітектур за взаємодією потоків команд і даних

- •52. Способи вдосконалення архітектур

- •53. Мікропроцесор та його функції

- •54. Основні параметри мп.

- •55. Характеристика мп 80386 та 80486.

- •56.Характеристика мп типу Pentium

- •57. Характеристика мп типу Pentium Pro

- •58. Характеристика мп ммх та Pentium II

- •59.Характеристика мп Pentium III

- •60.Технологія нт.

- •61. Характеристика мп типу Celeron.

- •62.Характеристика мп Pentium 4.

- •63. Технологія гіперконвеєрної обробки.

- •64.Характеристика мп типу risk.

- •65. Характеристика мп Over Drive.

- •66. Компоненти що входять до складу мп.

- •67. Операційна та інтерфейс на частини мп.

- •68. Функціональна схема пу мп.

- •69. Функціональна схема алп.

- •Мікропроцесорна пам'ять.

- •71. Типи регістрів мпп.

- •72. Універсальні регістри.

- •73. Сегментні регісти.

- •74. Регістри зміщень.

- •75. Регістри прапорців.

- •76. Управляючі прапорці.

- •77. Призначення інтерфейсної частини мп.

- •78. Інтерфейси евм.

- •79. Шини розширень.

- •80. Локальні шини.

- •81. Периферійні шини.

- •82.Універсальні послідовні шини.

- •83. Послідовна шина usb.

- •84. Станадарт ieee(Fire Wire).

- •85. Послідовний інтерфейс sata.

- •86. Послідовний інтерфейс sas.

- •87. Сімейство послідовних інтерфейсів pci Express.

- •88. Безпровідні інтерфейси.

- •89. Інтерфейс IrDa.

- •90. Інтерфейс Bluetooth.

- •91.Інтерфейс wusb.

- •92.Сімейство інтерфейсів wi fi.

- •93. Інтерфейс wi Max.

- •94. Синхронний та асинхронний sr-тригери.

- •95. Асинхронний сумуючий лічильник.

- •99. Часові характеристики цифрового сигналу. Синхроімпульси.

- •100. Архітектура, як інтерфейс між рівнями фізичної підсистеми.

- •101. Лічильники. Логічна стуктура лічильника. Режими роботи.

- •102. Шифратори:характеристика,класифікація.

- •103. Способи підвищення продуктивності кс.

- •104. Тегова пам'ять. Дискриптори.

- •105. Домен-як адресний простір.

- •106. Ключ на біп- транзисторі.

- •107. Вхідна характеристика логічного елемента.

- •108. Вихідна характеристика логічного елемента.

- •109. Передаточна характеристика логічного елемента.

- •110. Динамічні параметри логічних елементів.

- •111. Швидкодія логічних мікросхем.

- •112. Вимірювання часових параметрів сигналів.

93. Інтерфейс wi Max.

Технологія безпровідного зв’язку Wi Max – це комерційна назва стандарту IEEE 802.16a, заявленого в січні 2003р.

Третя версія стандарту IEEE 802.16a використовує «нищий» діапазон частот від 2 до 11 Г Гц, збільшена дальність зв’язку до 50 км. Зв’язок здійснюється і не в межах прямої видимості але знижена швидкість передачі до 75 Мбіт/с.

Інтерфейс Wi Max розроблявся для організації роботи безпровідних мереж, що охоплюють великі міста, регіони (стандарт MAN).

По етр-рі ці інтерфейси дуже подібні на стандарт мережі стільникового зв’язку. Для Wi Max також необхідні базові станції.

Т. ч. інтерфейси Wi Max і Wi Fi взаємно доповнюють один одного: Wi Fi – в локальних мережах всередині приміщень або на невеликих відкритих площадках, а Wi Max – для організацій більш глобального зв’язку в регіоні, місті.

По нових проектах споживач в приміщені працює по Wi Fi, а вийшовши – автоматично переходить на протокол Wi Max.

Сьогоднішня ера знаменує кардинальним оновленням інтерфейсів. Фірма Intel майже всі порти (COM, LPT, PS/2) і паралельні інтерфейси (ISA, PC, IDE – ATA) замінює на швидкісні послідовні. Вже є системні плати лише з інтерфейсами USB, а скоро – лише Serial ATA або PCI Express. А зв’язок із зовнішніми пристроями, а тим більше локальними і портативними мережами, буде виключно безпровідним.

94. Синхронний та асинхронний sr-тригери.

Асинхронний SR-тригер складається з двох комірок типу «І-НЕ»(«АБО-НЕ») замкнутих у кільце і є по суті елементарною коміркою без додаткового логічного пристрою.

Переключення SR-тритера відбувається сигналом 0, що подаються на входи S і R.

Синхронний SR-тригер містить ще й логічний пристрій з двох комірок «І-НЕ».

Переключення цього сигналу в ____, що подається на входи ____, але лише при наявності синхросигналу на вхід ЦЕ.

JK-тригер. Виконується по двохступінчастій структурі, що складається з двох синхронних SRтригерів і двох логічних схем «І-НЕ». Для цієї схеми S1=JQ і R1=KQ. Якщо J рівне одиниці і K рівне нулю, то при J рівне нулю S1 рівне одиниці. І після закінчення першого тактового імпульсу на вході C тригер встановлюється в стан Q=1.

Якщо J=1 і K=0,то при Q=1 обидва вхідних сигнали тригера першої ступені S1 і R1 будуть рівні нулю. І відповідно весь двохступеневий тригер не буде змінювати свого стану при приході синхроімпульса на вхід ЦЕ. Таким чином при J=1 і K=0 вихід тригера QN=1. Якщо QMN1 0 або 1 подібним чином по відношенню до стану Q0діє сигнал K 0 при J 0. Якщо ж J K 1то отримаємо S1 1 і R1 1. При Q0або S1 0 ____ при Q1. В наслідок цього при J K 1 тригер переключиться в протилежний стан при відповідному фронту сигналу на вході C .

95. Асинхронний сумуючий лічильник.

Асинхронний сумуючий лічильник виконують на тригерах довільного типу. Переважно використовують JK або D-тригери в лічильному режимі.

Найпростіший чотирьох розрядний лічильник на D-тригерах скадаєтсья із з’єднаних послідовно чотирьох лічильних тригерів таким чином щоб вихід кожного тригера з’єднаний з входом наступного. При надходженні лічильних імпульсів на вхід C тригери будуть змінювати свій стан. Для преведення лічильника у початковий стан використовуються сигнал скидання R, що поступає одночасно на всі входи R тригерів.

– схема асинхронного сумуючого лічильника.

Для побудови асинхронного реверсивного лічильника, який може функціонувати в режимі віднімання достатньо замінити виходи _____. В цьому випадку при надходження імпульсу скидання R на всіх виходах лічильника встановляться одиничні рівні. А при надходженні лічильників на вхід ЦЕ1 тригери лічильника будуть змінювати свої стани.

Для побудови асинхронного реверсивного лічильника можна за допомогою логічної схеми забезпечити подачу сигналів з інверсного виходу Q при сумуванні або з прямого виходу Q при відніманні від попереднього тригера на лічильний вхід наступного тригера.

96. JK-тригери.

Має 2 інформаційні входи: J і K. Подібно

до SR-тригера це входи, установки тритера

в стан 1 або 0.

97. D-тригер.

98.T-тригер.