- •1.Закон Мура в електроніці.

- •2. Основні тенденції розвитку комп’ютерної електроніки.

- •3. Продуктивність комп’ютерних систем та методи їх підвищення.

- •4. Фізичні обмеження в елементах комп’ютерів.

- •5. Інформація, інформаційний процес, вимоги до інформації.

- •6. Носії інформації та їх класифікація.

- •7. Сигнали та їх класифікації

- •8. Математичне представлення сигналів. Типи сигналів

- •9. Закони для булевих операцій.

- •10. Аналітичне представлення булевих функцій.

- •11. Арифметичні операції над числами, представлених в додаткових кодах.

- •12. Основні булеві функції Функції:

- •13. Способи задання булевих функцій

- •14. Буливі функції однієї змінної

- •15. Типи логічних елементів

- •16Аналітичне представлення булевих операцій

- •17. Елементи, вузли, пристрої кс

- •18. Потенціальні та імпульсні сигнали

- •Позитивний.

- •Негативний.

- •19.Класифікація елементів в комп’ютері

- •20. Імс та їх класифікація

- •26. Основні параметри цімс

- •27.Характеристики мікросхем

- •28.Швидкодія логічних мікросхем

- •29.Зп пристрої та їх класифікація

- •30. Функціональна схема ram. Статичні озп

- •32. Динамічні озп. Класифікація динамічних озп

- •36Елемент пам’яті на мнон транзисторі

- •37. Елемент пам’яті на лізмон транзисторі

- •38.Тригери та їх різновиди

- •39.Синхронізація роботи тригерів

- •40. Схемотехнічні принципи побудови тригерів. Jk тригери

- •41.Д тригери і т тригери

- •42. Лічильники імпульсів.

- •43. Асинхронні і синхронні лічильники

- •44. Дешифратори. Класифікація, основні характеристики.

- •45. Мультиплексори

- •46. Демультиплексори

- •47. Архітектура комп’ютерів:. Прінстонська і Гарвардська

- •48. Основні принципи Нейманівської архітектури є 2 блоки формування цих принципів.

- •49. Класифікація архітектур обчислювальних систем

- •50. Класифікація архітектур за взаємодією цп, пп, оп.

- •51. Класифікація архітектур за взаємодією потоків команд і даних

- •52. Способи вдосконалення архітектур

- •53. Мікропроцесор та його функції

- •54. Основні параметри мп.

- •55. Характеристика мп 80386 та 80486.

- •56.Характеристика мп типу Pentium

- •57. Характеристика мп типу Pentium Pro

- •58. Характеристика мп ммх та Pentium II

- •59.Характеристика мп Pentium III

- •60.Технологія нт.

- •61. Характеристика мп типу Celeron.

- •62.Характеристика мп Pentium 4.

- •63. Технологія гіперконвеєрної обробки.

- •64.Характеристика мп типу risk.

- •65. Характеристика мп Over Drive.

- •66. Компоненти що входять до складу мп.

- •67. Операційна та інтерфейс на частини мп.

- •68. Функціональна схема пу мп.

- •69. Функціональна схема алп.

- •Мікропроцесорна пам'ять.

- •71. Типи регістрів мпп.

- •72. Універсальні регістри.

- •73. Сегментні регісти.

- •74. Регістри зміщень.

- •75. Регістри прапорців.

- •76. Управляючі прапорці.

- •77. Призначення інтерфейсної частини мп.

- •78. Інтерфейси евм.

- •79. Шини розширень.

- •80. Локальні шини.

- •81. Периферійні шини.

- •82.Універсальні послідовні шини.

- •83. Послідовна шина usb.

- •84. Станадарт ieee(Fire Wire).

- •85. Послідовний інтерфейс sata.

- •86. Послідовний інтерфейс sas.

- •87. Сімейство послідовних інтерфейсів pci Express.

- •88. Безпровідні інтерфейси.

- •89. Інтерфейс IrDa.

- •90. Інтерфейс Bluetooth.

- •91.Інтерфейс wusb.

- •92.Сімейство інтерфейсів wi fi.

- •93. Інтерфейс wi Max.

- •94. Синхронний та асинхронний sr-тригери.

- •95. Асинхронний сумуючий лічильник.

- •99. Часові характеристики цифрового сигналу. Синхроімпульси.

- •100. Архітектура, як інтерфейс між рівнями фізичної підсистеми.

- •101. Лічильники. Логічна стуктура лічильника. Режими роботи.

- •102. Шифратори:характеристика,класифікація.

- •103. Способи підвищення продуктивності кс.

- •104. Тегова пам'ять. Дискриптори.

- •105. Домен-як адресний простір.

- •106. Ключ на біп- транзисторі.

- •107. Вхідна характеристика логічного елемента.

- •108. Вихідна характеристика логічного елемента.

- •109. Передаточна характеристика логічного елемента.

- •110. Динамічні параметри логічних елементів.

- •111. Швидкодія логічних мікросхем.

- •112. Вимірювання часових параметрів сигналів.

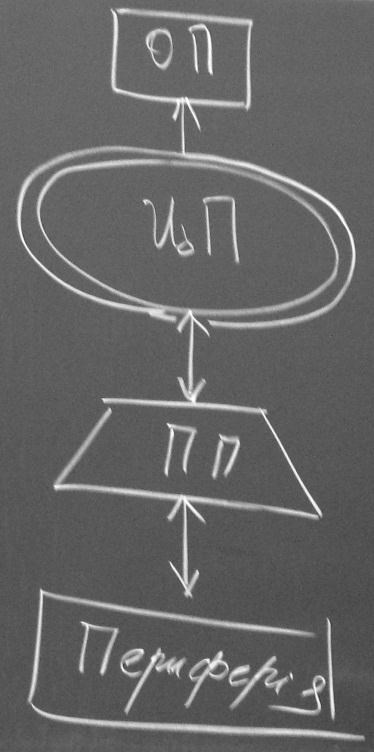

50. Класифікація архітектур за взаємодією цп, пп, оп.

По структурним зв’язкам архітектури ОС поділяються на:

Одно процесорна зі зв’язком через центральний процесор(ЦП).

З одним потужнім процесором(ЦП) і кількома процесорами(ПП), які його обслуговують.

Багатопроцесорна.

З магістральною шиною.

Мережна.

Функціонально переналагоджувальна.

Мас процесорна, яка містить велику кількість процесорів.

В такій архітектурі центральний процесор

контролює роботу всієї системи. Зв’язок

із периферійними пристроями здійснюється

або через прямі канали, або через

ПП(периферійні пристрої). Така архітектура

характерна для машин третього покоління.

Однак також така архітектура

використовується для виконання

спеціальний функцій у комп’ютерних

мережах. Однак для випадку продуктивних

операцій у випадку кожного звертання

необхідно переривати роботу ЦП, тому

реалізується ідея про поєднання потужного

ЦП з декількома менш потужнішими функція

яких полягає у обслуговуванні переривань

від зовнішніх пристроїв а також ОЗП.

такій архітектурі центральний процесор

контролює роботу всієї системи. Зв’язок

із периферійними пристроями здійснюється

або через прямі канали, або через

ПП(периферійні пристрої). Така архітектура

характерна для машин третього покоління.

Однак також така архітектура

використовується для виконання

спеціальний функцій у комп’ютерних

мережах. Однак для випадку продуктивних

операцій у випадку кожного звертання

необхідно переривати роботу ЦП, тому

реалізується ідея про поєднання потужного

ЦП з декількома менш потужнішими функція

яких полягає у обслуговуванні переривань

від зовнішніх пристроїв а також ОЗП.

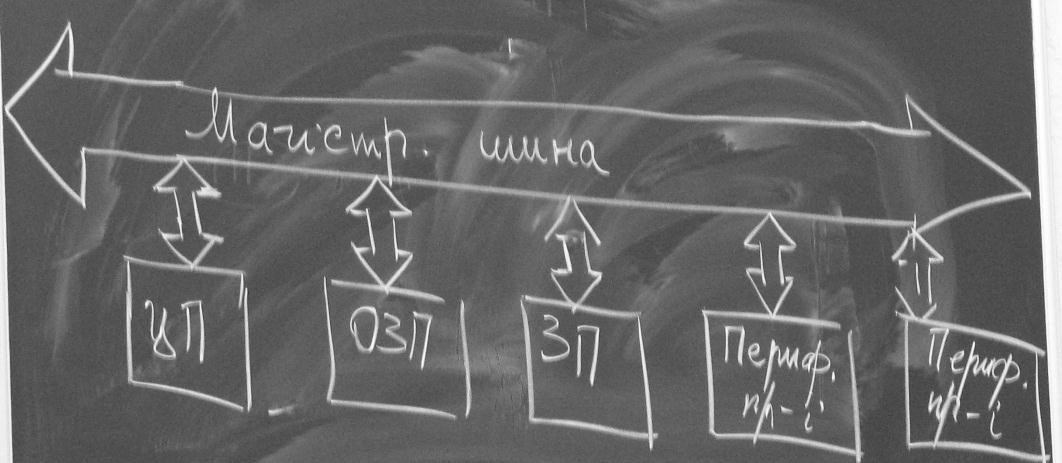

Обчислювальні системи з магістральною шиною.

Специфіка такої архітектури полягає в тому, що всі частини ОС(обчислювальної системи) можуть бути приєднаними до магістральної шини, захоплюючи її на короткий період машинного такту для обміну інформації. Для запобіганню конфліктів використовується арбітр шини.

51. Класифікація архітектур за взаємодією потоків команд і даних

опрацьовування множини даних, при чому

кількість елементів, що опрацьовуються

може бути дуже

52. Способи вдосконалення архітектур

Архітектура комп’ютерів в основному вдосконалюється зараз за рахунок введення додаткових засобів:

1. Збереження даних у вигляді само визначених даних.

Як правило інформація про тип збережених у пам’яті даних міститься у командах програми. Однак у комірці пам’яті можна вказати і тип даних доповнивши їх деяким набором, який називається «тегом». Цей принцип організації пам’яті має назву тегової пам’яті. При чому теги можуть зберігати також інші характеристики, на приклад, довжину операнда. Існує 2 типи тегів:

Статичні. Вміст яких визначається перед виконанням програми і в ході обчислень не змінюється.

Динамічні. З наповненням його змісту під час обчислень і періодичним оновленням. Переваги тегової пам’яті дозволяють:

Виявляти помилки.

Підвищити швидкість обробки команд.

Спростити алгоритми деяких операцій.

Дозволяють робити від лагодження програми більш досконало.

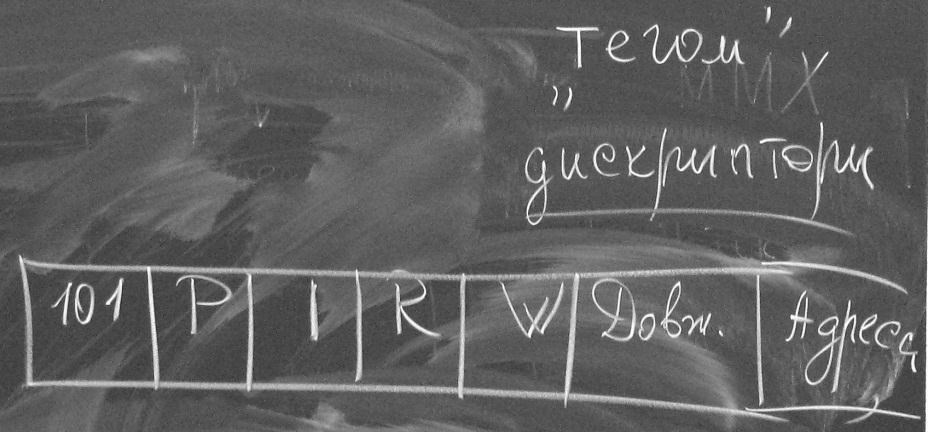

Економія пам’яті через відсутність генерування кодів для функцій контролю і перетворення даних. Поряд з тегами використовуються так звані дескриптори.

Дескриптор – це додаткова інформація, що відіграє роль опосередкованої адреси комірки пам’яті з даними.

В таких комп’ютерах команди містять посилання на дескриптори, які у свою чергу посилаються на області пам’яті, що зберігають значення операндів команд. Основна відмінність тегів і дескрипторів:

Дескриптори створюють додатковий рівень адресацій, тобто дескриптори це частина команди або програми а теги це частина даних. Приклад дескриптора:

Пояснення індексів:

Індекс ПЕ означає, чи знаходяться па

АЙ – означає, чи описує даний дескриптор лише ___ чи весь масив.

ЕР – ідентифікує неперервну чи ___ область пам’яті.

ДУБЛЬ ВЕ – дозвіл лише для читання даних,