- •Теми для самостійного опрацювання з предмету “Комп’ютерна схемотехніка” Розділ 1. Основи двійкової арифметики

- •Тема 1.1. Подання чисел з фіксованою комою в розрядній сітці

- •Домашнє завдання

- •Ділення чисел з фіксованою комою

- •Алгоритм ділення модулів чисел без відновлення остач

- •Ділення з відновленням залишку

- •Тема 1.2. Виконання арифметичних операцій над числами з плаваючою комою (пк)

- •Розділ 2. Основи алгебри логіки (ало)

- •Тема 2.1 Основні функції та теореми алгебри логіки.

- •Домашнє завдання

- •Тема 2.2. Мінімізація логічних функцій

- •Розділ 3. Схемотехніка комбінаційних схем

- •Тема 3.1. Дешифратори та шифратори. Селектори та мультиплексори.

- •11, 12, 13, 14, 15, 16, 17, 18, 19 – Інформаційні входи;

- •09, 07, 06, 14 – Інформаційні виходи. Побудова універсальних логічних модулів (улм) за допомогою ms

- •Тема 3.2. Перетворювачі кодів

- •Перетворювач двійково–десяткових чисел в код семисегментного індикатора.

- •Тема 3.3. Суматори (sm)

- •Розділ 4. Схемотехніка накопичувальних схем

- •Тема 4.1. Тригери

- •Інтегральна мікросхема кр1533тв6

- •Контрольне завдання

- •Тема 4.3. Лічильники.

Розділ 4. Схемотехніка накопичувальних схем

Тема 4.1. Тригери

Лекція №15с. Тригери на ІМС

Інтегральна мікросхема кр1533тв6

Основу послідовних цифрових структур складають тригери різних типів, які можуть використовуватися самостійно або у складі лічильників, регістрів і т. д.

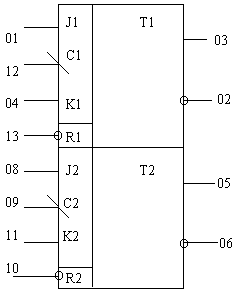

Конструктивно мікросхема КР1533ТВ6, рис.1, являє собою два JK-тригера, що спрацьовують по негативному фронту тактового сигналу, з входами скидання. Низький рівень напруги на вході скидання R встановлює прямий вихід Q відповідного тригера в стан низького рівня напруги незалежно від логічного стану на інших входах. За наявності на вході скидання напруги високого рівня для правильної роботи тригера потрібна попередня установка інформації з входів J і К щодо негативного фронту тактового сигналу, а також відповідний витяг інформації після подачі негативного фронту синхросигналу С. При подачі на входи J і К напруги високого рівня тригер буде працювати в якості лічильного.

Рис.1. УГП мікросхеми тригера КР1533ТВ6

Мікросхеми виготовляються за вдосконаленою епітоксіально - планарною технології з діодами Шотткі і окисної ізоляцією, одно-і дворівневої металізованої розводкою на основі PtSi-TiW0AlSi. Конструктивно мікросхеми серії КР1533 виконані в 14 -, 16 -, 20 -, і 24 - вивідних стандартних пластмасових корпусах типу 201, 14-1, 238.16-1, 2140.20-8, 2142.42-2Малопотужні швидкодіючі цифрові ІМС серії КР1533 призначені для організації високошвидкісного обміну та обробки цифрової інформації, тимчасового та електричного узгодження сигналів в обчислювальних системах.

Таблиця призначення виводів

Номер виводу |

Призначення |

|

Номер виводу |

Призначення |

0 1 |

Вхід управління J тригера Т1 |

|

0 8 |

Вхід управління J тригера Т2 |

0 2 |

Вихід інверсний тригера Т1 |

|

0 9 |

Синхровхід С тригера Т2 |

0 3 |

Вихід прямий тригера Т1 |

|

1 0 |

Вхід скидання R тригера Т2 |

0 4 |

Вхід керуючий К тригера Т1 |

|

1 1 |

Вхід керуючий К тригера Т2 |

0 5 |

Вихід прямий тригера Т2 |

|

1 2 |

Синхровхід С тригера Т1 |

0 6 |

Вихід інверсний тригера Т2 |

|

1 3 |

Вхід скидання R тригера Т1 |

0 7 |

Загальний вивід |

|

1 4 |

Вивід живлення Ucc |

Таблиця істинності

Входи |

Виходи |

|||||

R |

C |

J |

K |

Q |

|

|

0 |

X |

X |

X |

0 |

1 |

|

1 |

1/0 |

0 |

1 |

0 |

1 |

|

1 |

1/0 |

1 |

1 |

Лічильний режим |

||

1 |

1/0 |

0 |

0 |

Q 0 |

|

|

1 |

1/0 |

1 |

0 |

1 |

0 |

|

1 |

1 |

X |

X |

Q 0 |

|

|