- •Ю.В.Шаповалов Схемотехника эвм Конспект лекций

- •Глава 1.

- •Глава 2. Основы алгебры логики.

- •§1. Функции алгебры логики и их основные свойства.

- •Диаграммы Венна.

- •Здесь 0 представлен как класс, совсем не имеющий точек, а 1 – как класс всех точек квадрата.

- •§2. Формы записи булевых функций. Табличная запись.

- •Аналитическая запись.

- •§3. Основная теорема.

- •§4. Выражение функции в сднф и скнф с помощью аналитических преобразований.

- •§5. Способы выявления равносильности булевых функций.

- •§6. Свойства функций сложения по модулю 2.

- •Алгоритм построения.

- •§7. Основные классы функций алгебры логики.

- •Класс линейных функций от n аргументов (Ln).

- •Класс функций, сохраняющих единицу (к1).

- •Класс монотонных булевых функций (м).

- •Класс самодвойственных функций (u).

- •Подставляя функции φi вместо аргументов XI, получаем

- •Найдем значение функции f2 на противоположных наборах аргументов

- •§8. Полные системы булевых функций.

- •Раздел 2. Минимизация булевых функций.

- •§1. Сокращенные, тупиковые и минимальные формы булевых функций.

- •§2. Метод Квайна.

- •Алгоритм метода Квайна.

- •§3. Гарвардский метод.

- •§4. Метод импликантных матриц.

- •§5. Минимизация булевых функций с помощью карт Вейча.

- •Правила склеивания с помощью карт Вейча.

- •Метод Блека-Порецкого.

- •§6. Минимальные конъюнктивные нормальные формы булевых функций.

- •Из них обязательными является ас и . Функция имеет две минимальные формы:

- •§8. Абсолютные минимальные представления булевых функций.

- •Раздел 3.

- •§1. Синтез логических схем на интегральных элементах.

- •Синтез схем на элементах типа «не-или».

- •Берем двойное отрицание от каждой суммы

- •Импликанты и объединяются по правилу 1, а не объединяется с ними:

- •§2. Синтез логических схем на мультиплексорах.

- •Глава 3. Структурный и абстрактный синтез устройств вм.

- •Глава 4.Сверхбольшие интегральные схемы

- •4.1. Классификация сбис программируемой логики

- •1. Степень интеграции

- •Соединений.

- •4. Технология изготовления программируемого элемента

- •4.2 Семейство max Общая характеристика.

- •Программируемая матрица соединений.

- •Макроячейка.

- •Разделяемый расширитель.

- •Блок ввода/вывода

- •Глава 5. Методы и средства функционального синтеза

- •2.4. Детерминированные методы расчета элементов и узлов

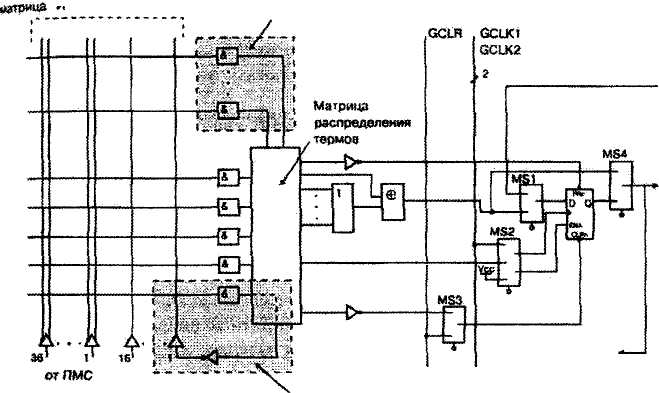

Макроячейка.

Макроячейка, внутренняя структура которой приведена на рис. 4.15, содержит:

участок локальной программируемой матрицы "И";

программируемую матрицу распределения термов;

матрицу "ИЛИ";

программируемый элемент сложения по mod2;

синхронный триггер;

параллельный логический расширитель;

разделяемый логический расширитель;

цепь быстрого ввода;

набор программируемых мультиплексоров (MS[3...1]).

от

вывода Цепь

быстрого ввода СБИС

кБВВ

вПМС Лкальная

Лкальная

Программируемая

"

Параллельные логические расширители

Разделяемый логический расширитель

Рис. 4.15 Структура макроячейки

Комбинационную часть макроячейки образуют: участок локальной программируемой матрицы "И", обеспечивающий формирование пяти термов; программируемая матрица распределения термов, позволяющая размещать формируемые термы и использовать параллельный и разделяемый логические расширители; матрица "ИЛИ"; элемент сложения по mod2; параллельный расширитель; разделяемый расширитель.

Параллельный расширитель.

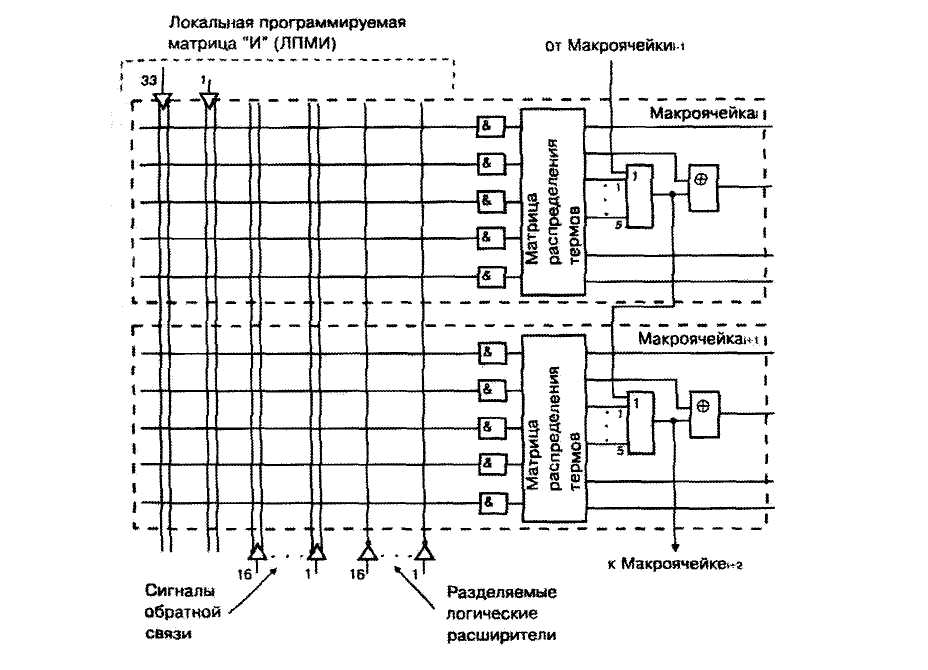

Для реализации сложных логических функций, в ДНФ которых входит более пяти термов, целесообразно применение параллельных логических расширителей, позволяющих совместно использовать термы (либо все, либо оставшиеся нераспределенными) смежных макроячеек. Одна цепочка параллельных расширителей может включать до четырех макроячеек, обеспечивая, таким образом, возможность реализации логической функции, имеющей до двадцати термов.

Организация цепочки параллельных расширителей иллюстрируется на рис. 4.16.

В пределах каждого Л Б, содержащего 16 макроячеек, может быть организовано две цепочки параллельных расширителей: одна на макроячейках с номерами от 1 до 8, другая на макроячейках с номерами от 9 до 16. При этом каждая из них начинается с макроячейки, имеющей меньший номер.

Рис. 4.16 Организация цепочки параллельных расширителей

Задержка в формировании выходного значения логической функции, в ДНФ которой входит 20 термов, реализованной с использованием параллельных

расширителей на СБИС МАХ 7032-5, составит: г = iMD +3 * тРЕХР + Тс.омв =1.5+3*0.8+0.8=4.7нс, где: fLAD -задержка формирования выходного сигнала матрицами "И", "ИЛИ";

ТРЕХР - задержка распространения сигнала в цепи параллельного логического расширителя (от выхода матрицы "ИЛИ" i-ой макроячейки до выхода матрицы "ИЛИ" 0+1)-ой макроячейки); Тсомв " задержка передачи сигнала с выхода матрицы "ИЛИ" на выход макроячейки.

Разделяемый расширитель.

Для реализации сложных логических функций с большим количеством переменных, целесообразно использование разделяемых логических расширителей. Разделяемый логический расширитель формирует терм, инверсное значение которого передается матрицей размещения термов в локальную программируемую матрицу "И" и может быть использовано в любой макроячейке данного ЛБ.

Отметим, что каждая макроячейка содержит только один разделяемый расширитель.