- •Ю.В.Шаповалов Схемотехника эвм Конспект лекций

- •Глава 1.

- •Глава 2. Основы алгебры логики.

- •§1. Функции алгебры логики и их основные свойства.

- •Диаграммы Венна.

- •Здесь 0 представлен как класс, совсем не имеющий точек, а 1 – как класс всех точек квадрата.

- •§2. Формы записи булевых функций. Табличная запись.

- •Аналитическая запись.

- •§3. Основная теорема.

- •§4. Выражение функции в сднф и скнф с помощью аналитических преобразований.

- •§5. Способы выявления равносильности булевых функций.

- •§6. Свойства функций сложения по модулю 2.

- •Алгоритм построения.

- •§7. Основные классы функций алгебры логики.

- •Класс линейных функций от n аргументов (Ln).

- •Класс функций, сохраняющих единицу (к1).

- •Класс монотонных булевых функций (м).

- •Класс самодвойственных функций (u).

- •Подставляя функции φi вместо аргументов XI, получаем

- •Найдем значение функции f2 на противоположных наборах аргументов

- •§8. Полные системы булевых функций.

- •Раздел 2. Минимизация булевых функций.

- •§1. Сокращенные, тупиковые и минимальные формы булевых функций.

- •§2. Метод Квайна.

- •Алгоритм метода Квайна.

- •§3. Гарвардский метод.

- •§4. Метод импликантных матриц.

- •§5. Минимизация булевых функций с помощью карт Вейча.

- •Правила склеивания с помощью карт Вейча.

- •Метод Блека-Порецкого.

- •§6. Минимальные конъюнктивные нормальные формы булевых функций.

- •Из них обязательными является ас и . Функция имеет две минимальные формы:

- •§8. Абсолютные минимальные представления булевых функций.

- •Раздел 3.

- •§1. Синтез логических схем на интегральных элементах.

- •Синтез схем на элементах типа «не-или».

- •Берем двойное отрицание от каждой суммы

- •Импликанты и объединяются по правилу 1, а не объединяется с ними:

- •§2. Синтез логических схем на мультиплексорах.

- •Глава 3. Структурный и абстрактный синтез устройств вм.

- •Глава 4.Сверхбольшие интегральные схемы

- •4.1. Классификация сбис программируемой логики

- •1. Степень интеграции

- •Соединений.

- •4. Технология изготовления программируемого элемента

- •4.2 Семейство max Общая характеристика.

- •Программируемая матрица соединений.

- •Макроячейка.

- •Разделяемый расширитель.

- •Блок ввода/вывода

- •Глава 5. Методы и средства функционального синтеза

- •2.4. Детерминированные методы расчета элементов и узлов

Глава 4.Сверхбольшие интегральные схемы

4.1. Классификация сбис программируемой логики

Разнообразие существующих в настоящее время типов СБИС ПЛ различных фирм не позволяет выбрать единый критерий для их всеобъемлющей классификации. Поэтому целесообразно выделить набор классификационных критериев, обеспечивающих возможность систематизации информации о характеристиках и особенностях существующих СБИС ПЛ и выбора ПЛИС, необходимых при проектировании устройства :

степень интеграции;

архитектура простейшего функционального преобразователя;

организация внутренней структуры СБИС и структуры матрицы соединений функциональных преобразователей;

технология изготовления программируемого элемента.

1. Степень интеграции

Степень интеграции БМК и СБИС ПЛ характеризуется логической емкостью. Логическая емкость, измеряемая числом (Nт) логических вентилей

(элементов типа 2И-НЕ), определяет возможность оцениваемой СБИС обеспечить реализацию цифрового устройства (либо цифровых устройств), для построения которого (которых) требуется Nm логических вентилей.

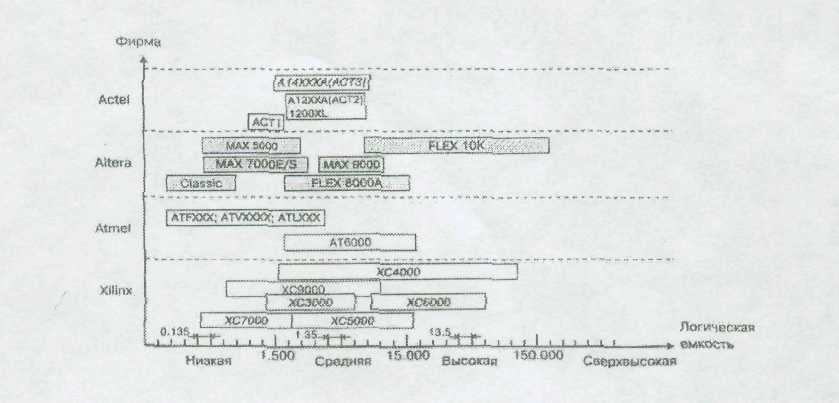

В соответствии с выбранным критерием СБИС ПЛ делят на СБИС, имеющие:

низкую степень интеграции (лог. емк. до 1500 ЛВ);

среднюю степень интеграции (лог.емк. от 1500 до 15000 ЛВ);

высокую степень интеграции (лог.емк. от 15000 до 150000 ЛВ);

сверхвысокую степень интеграции (лог.емк. более 150000 ЛВ).

Соотношение логической емкости наиболее широко известных семейств СБИС ПЛ иллюстрируется на рис. 4.1, где отражены также и названия фирм, выпускающих указанные семейства.

Рис. 4.7 Логическая емкость СБИС ПЛ 2. Архитектура простейшего функционального преобразователя.

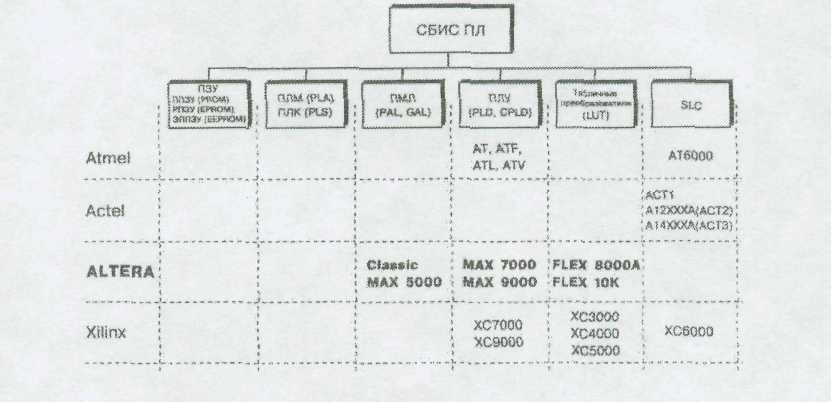

Классификация СБИС ПЛ в соответствии с данным критерием приведена на рис. 4.2.

Puc. 4.2 Архитектуры простейших функциональных преобразователей СБИС ПЛ

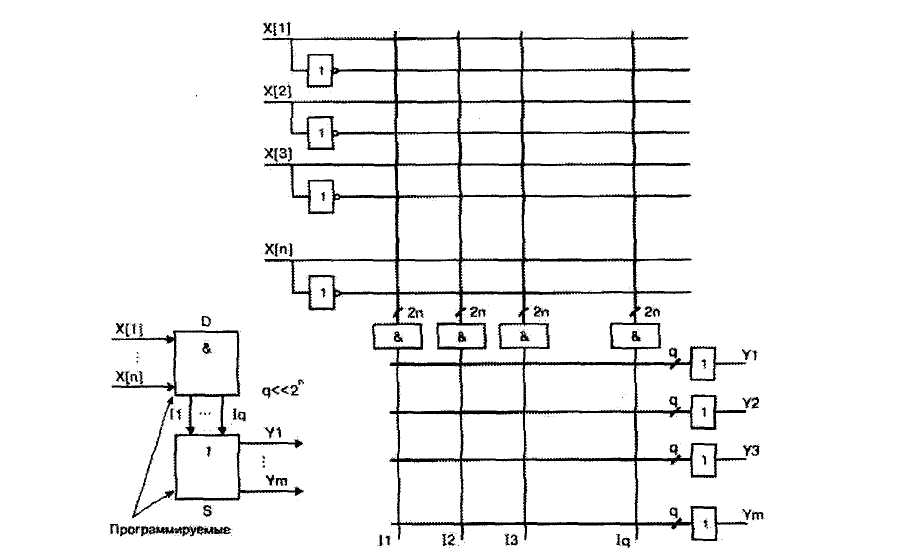

Первыми в логическом проектировании цифровых устройств получили применение БИС постоянных запоминающих устройств: программируемых (ППЗУ, PROM), репрограммируемых (РПЗУ, EPROM) и электрически перепрограммируемых (ЭЛПЗУ, EEPROM). ПЗУ имеет структуру универсального логического преобразователя, т.е. функционально является композицией двух блоков (см. рис. 4.3): дешифратора (D) и шифратора (S). Дешифратор, имеющий фиксированную структуру, порождает полный набор термов от п входных переменных. Шифратор, реализованный на базе массива хранения данных ПЗУ, является программируемым и обеспечивает формирование m независимых логических функций (m - разрядность выходных данных ПЗУ) от п переменных, представленных в совершенной дизъюнктивной нормальной форме. Недостаток такой организации - избыточность представления функции в СДНФ и связанная с ней степенная зависимость объема накопителя ПЗУ от числа аргументов. Так, для реализации функции от 32 переменных потребуется массив объемом 232=4Гбит.

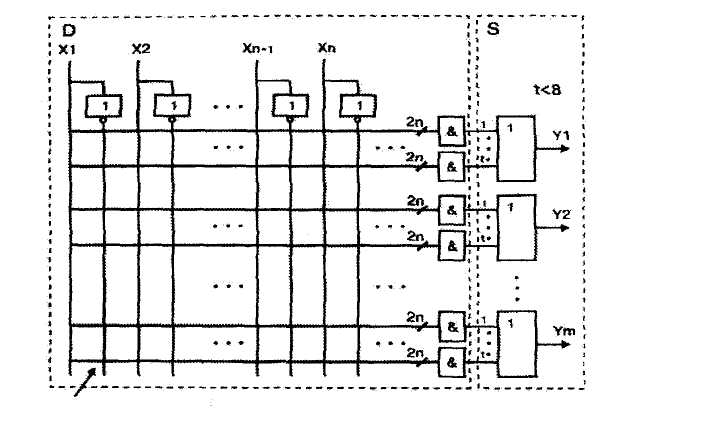

4.3. ПЗУ- универсальный логический преобразователь СБИС ПЛ следующего поколения - программируемые логические матрицы ПЛМ (Programmable Logic Array - PLA), позволяющие реализовать логические функции, представленные в произвольной (сокращенной, тупиковой, минимальной) дизъюнктивной нормальной форме (ДНФ). ПЛМ также, как и ПЗУ, имеет структуру универсального логического преобразователя (см. рис. 4.4); дешифратор (D) - шифратор (S). Причем, и дешифратор (матрица "И") и шифратор (матрица "ИЛИ") являются программируемыми. Для обеспечения возможности реализации не только комбинационных, но и последовательных схем, на выходы шифратора были добавлены триггеры. Такие БИС получили название программируемые

логические контроллеры (ПЛК), а за рубежом -Programmable Logic Sequencers (PLS).

Поскольку у логических функций, представленных в дизъюнктивной нормальной форме, редко бывают общие термы, то матрица "ИЛИ" оказывается

разреженной, а занятая ей часть кристалла используется не полностью. Таким образом, недостаток ПЛМ и ПЛК - неэффективное использование матрицы "ИЛИ".

имеет фиксированную структуру. Простейшие БИС ПМЛ за рубежом получили название Programmable Array Logic (PAL), а ПМЛ с регистрами на выходе - Generic Array Logic (GAL).

( На рис.4.5. Структура БИС программируемой матричной логики)

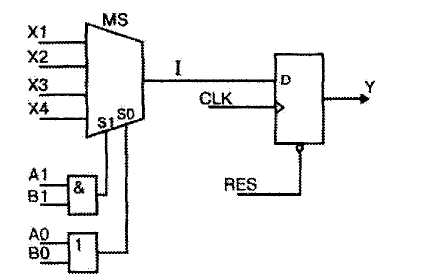

В его состав входят: п - входовая таблица перекодировки (ШТ); синхронный триггер; логическая схема управления асинхронными установкой/сбросом триггера (R_S); программируемый мультиплексор выбора источника выходного сигнала (MS). Таблица перекодировок с п входами представляет собой одноразрядное запоминающее устройство объемом 2" бит, позволяющее реализовать любую логическую функцию от п переменных. Таким образом, в рамках простейшего функционального преобразователя, как и в исторически первых СБИС ПЛ — ПЗУ, для формирования логической функции используется фиксированная матрица «И» и программируемая матрица «ИЛИ». Однако, в отличие от ПЗУ, число входов (п) в таблицу перекодировок невелико, а число простейших функциональных преобразователей, размещенных в СБИС, наоборот - весьма значительно и может достигать нескольких тысяч. Это позволяет осуществлять иерархическую реализацию сложных логических функций, и тем, самым нивелировать известный недостаток табличной реализации, связанный со степенной зависимостью объема ЗУ от числа аргументов функции. Так, для реализации функции от 32 аргументов потребуется всего 11 четырехвходовых таблиц перекодировок, а не ЗУ объемом 4Гбит.

Другой тип архитектуры (Simple Logic Cell) простейшего функционального преобразователя (см. рис. 4.8), объединяющий разнообразные СБИС ПЛ различных производителей, основан на использовании комбинационных схем, обеспечивающих реализацию того или иного, минимального или неминимального базиса. В зависимости от используемых комбинационных схем, структуры подобных простейших функциональных преобразователей существенно

‗‗

‗‗ ‗‗ ‗‗

i

= S1& S0& X1 + S1& S0& X2 + S1&S0& X3 + S1&

S0& X4

4.8

Структура простейшего

функционального

преобразователя

СБИС ПЛ

3. Организация внутренней структуры и структуры матрицы