- •Лекція №7 з дисципліни «Основи електроніки та мікроелектроніки»

- •1. Логічний елемент — це електронний пристрій, що реалізує одну з логічних операцій, наприклад, суматор, тригер.

- •Принцип роботи

- •Пристрій і принцип роботи

- •Історія

- •2. Найпростіші логічні прилади.

- •Суматор(виконаний за американським стандартом)

Лекція №7 з дисципліни «Основи електроніки та мікроелектроніки»

Логічні елементи

План лекції

1) |

Види електронних логік. |

2) |

Найпростіші логічні прилади. |

Матеріал:

1. Логічний елемент — це електронний пристрій, що реалізує одну з логічних операцій, наприклад, суматор, тригер.

Логічні елементи являють собою електронні пристрої, у яких оброблювана інформація закодована у вигляді двійкових чисел, відображуваних напругою (сигналом) високого і низького рівня.

Термін «логічні» прийшов в електроніку з алгебри логіки, що оперує зі змінними величинами і їхніми функціями, що можуть приймати тільки два значення: «істинно» чи «хибно». Для позначення істинності чи хибності висловлювань використовують відповідно символи 1 чи 0. Кожна логічна змінна може приймати тільки одне значення: 1 чи 0. Ці двійкові змінні і функції від них називаються логічними змінними і логічними функціями. Пристрої, що реалізують логічні функції, називаються логічними або цифровими пристроями.

Діодно-транзисторна логіка (ДТЛ), англ. Diode-transistor logic (DTL) — технологія побудови цифрових схем на основі біполярних транзисторів, діодів і резисторів. Свою назву технологія отримала завдяки реалізації логічних функцій (наприклад, 2І) за допомогою діодних ланцюгів, а посилення і інверсії сигналу — за допомогою транзистора.

Принцип роботи

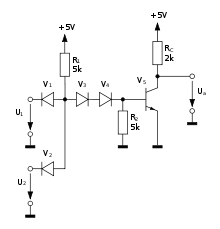

Показана на рисунку схема є прикладом схемотехнічної реалізації типового логічного вентиля 2І-НІ в ДТЛ.

Якщо хоча б на одному з входів встановлений рівень логічного нуля (U1 або U2), то в точці з'єднання V1, V2, V3, R1 потенціал визначається як сума напруги логічного нуля та падіння напруги на вхідному діоді V1 або V2. Цього потенціалу виявляється недостатньо для відкриття транзистора V5. При цьому на виході схеми формується рівень логічної одиниці.

Якщо на всіх входах встановлено рівень логічної одиниці, то вхідні діоди виявляються закритими, а в точці з'єднання V1, V2, V3, R1 встановлюється високий потенціал, при цьому транзистор V5 відкривається і переходить в режим насичення, а на виході встановлюється низький потенціал логічного нуля.

Діоди V3, V4 забезпечують необхідний для надійного перемикання вихідного транзистора діапазон напруг логічного нуля (від 0 до приблизно 1.2 Вольт) та логічної одиниці (більше 1.2 Вольт)

Параметри

споживана потужність:

логічний нуль на виході - близько 15 міліВатт;

логічна одиниця на виході - до 1 міліВатта;

час перемикання - близько 30 нС.

Переваги та недоліки

Основна перевага ДТЛ перед більш ранньою технологією РТЛ — можливість організації значного числа входів логічного елемента.

Основний недолік — значна затримка перемикання елемента, яка є наслідком роботи транзистора в режимі насичення, через повільність перезарядження ємності переходу база-емітер. Для зменшення часу розряду включено резистор R2, для зменшення часу заряду - встановлено резистор R1 з відносно малим опором.

Виробництво

У СРСР випускались серії мікросхем з ДТЛ: 104, 109, 121, 128, 146, 156, 205, 215, 217, 218, 221, 240, 511

Емітерно-зв'язана логіка, ЕЗЛ (англ. Emitter Coupled Logic, ECL) — технологія побудови цифрових схем на основі біполярних транзисторів включених за схемою диференціального підсилювача. ЕЗЛ є найшвидкодіючою з усіх типів логіки, побудованої на біполярних транзисторах. Це пояснюється тим, що транзистори в ЕЗЛ працюють у лінійному режимі, не переходячи у режим насичення, вихід з якого уповільнений.

Принцип роботи

Низькі значення логічних перепадів в ЕЗЛ-логіці сприяють зниженню впливу на швидкодію паразитних ємностей, а диференціальний підсилювач на вході дозволяє значно зменшити вплив синфазних збурень у вхідному сигналі.

Основна деталь ЕЗЛ-логіки — схема потенційного порівняння, зібрана не на діодах (як у ДТЛ), а на транзисторах за схемою диференціального підсилювача. Як правило, один транзистор у схемі порівняння підключений до опорного рівня, рівному напрузі логічного порогу, а інші транзистори є входами. Вихід схеми порівняння подається на підсилювальні транзистори, а з них — на вихідні емітерні повторювачі. Використання емітерних повторювачів на виході значно зменшує вихідний опір схеми, забезпечує можливість підключення значної кількості входів інших елементів та забезпечує шунтування збурень в ланцюгу навантаження.

Параметри

Типові параметри для серії К500:

споживана потужність: близько 50 міліВатт;

час перемикання: 4-6 нс.

напруга живлення:

вхідний каскад: −5,2 Вольта

вихідний каскад: −2 Вольта

опір резисторів навантаження: 51 Ом

логічні рівні (для серії К500):

логічна одиниця: −1,6 — −2 Вольта

логічний нуль: −0,8 Вольта

Переваги та недоліки

Основною перевага ЕЗЛ є підвищена швидкість (150 МГц вже в перших зразках 1960-х років і 0,5 … 2 ГГц у 1970-1980-х). Також, виходи кількох елементів ЕЗЛ можуть бути об'єднані на спільному резисторі навантаження.

Основний недолік — відносно високе енергоспоживання, необхідність використання двох джерел живлення (для вхідного та вихідного каскадів окремо), необхідність встановлення додаткових резисторів навантаження.

Резисторно-транзисторна логіка (РТЛ) - технологія побудови цифрових схем на базі простих транзисторних ключів. Свою назву технологія отримала завдяки реалізації логічних функцій (наприклад, 2АБО) складанням токів на резисторі, а посилення і інверсії сигналу — за допомогою транзистора.