- •Функциональные устройства микропроцессорных систем

- •Функциональные устройства микропроцессорных систем

- •Часть I

- •Введение

- •Элементы алгебры логики

- •Логические функции одной переменной

- •Логические функции двух переменных

- •Свойства элементарных функций алгебры логики

- •Функционально полные системы булевых функций

- •Комбинационные схемы

- •Базовые элементы 2и-не и 2или-не

- •Логический элемент 2и-не

- •Логический элемент 2или-не

- •Электронная реализация базового логического элемента 2и-не

- •Простейшие логические элементы Логический элемент 2и

- •Логический элемент 2или

- •Логический элемент 3и

- •Логический элемент Исключающее или

- •Комбинирование логических элементов

- •Простейшие интегральные микросхемы средней степени интеграции

- •Типовые комбинационные схемы Полусумматоры

- •Одноразрядные полные сумматоры

- •Дешифраторы

- •Шифраторы

- •Компараторы

- •Сравнение на равенство

- •Сравнение на “больше”

- •Мультиплексоры

- •Синтез комбинационных схем

- •Схемы с элементами памяти Цифровые автоматы

- •Триггеры

- •Асинхронный (несинхронизируемый) rs-триггер

- •Синхронизируемый (тактируемый) rs-триггер

- •D-триггер

- •Т-триггер

- •Универсальный jk-триггер

- •Классификация триггеров

- •Одноступенчатые и двухступенчатые триггеры

- •Счетчики

- •Суммирующий счетчик с последовательным переносом

- •Другие типы счетчиков

- •Регистры

- •Параллельные регистры

- •Последовательные регистры

- •Система маркировки интегральных микросхем

- •Пример маркировки имс

- •Рекомендуемая литература

- •Часть I

Другие типы счетчиков

Рассмотренный счетчик является простейшим по схемной реализации. Он относится к счетчикам последовательного типа, т.к. в них каждый очередной триггер переключается выходным сигналом предыдущего триггера, и поэтому отличается низким быстродействием.

Более быстродействующими являются параллельные счетчики, в которых все разряды переключаются одновременно.

В вычитающих счетчикахпри подаче на счетный вход очередного импульса значение выходного кода счетчика уменьшается на единицу.

Реверсивные счетчикипозволяют выполнять операции суммирования и вычитания импульсов в зависимости от сигналов управления на входах счетчика.

Рассмотренный двоичный счетчик позволяет получить коэффициент счета, т.е. число устойчивых состояний, 2n, где n - разрядность счетчика. Однако иногда нужны счетчики с модулем счета, отличным от 2n, например, счетчики с модулем 10. Принцип построения таких счетчиков заключается в исключении “лишних” устойчивых состояний в счетчике 2n. Это может быть достигнуто:

путем применения логических схем, запрещающих некоторые состояния;

использованием обратных связей;

начальной установкой счетчика в некоторой состояние.

Наиболее широко применяемые счетчики такого типа - это двоично-десятичные счетчикиСТ2/10, имеющие 10 устойчивых состояний (декадные счетчики).

Регистры

Регистром называется устройство, предназначенное для запоминания двоичных слов, а также для выполнения над словами некоторых логических операций.

Регистр представляет собой совокупность триггеров, число которых равно числу разрядов в запоминаемом слове, и вспомогательных схем, обеспечивающих некоторые из следующих операций:

сброс триггеров в логической 0;

прием слова из другого устройства (регистра, сумматора и т.д.);

передача слова в другое устройство;

сдвиг слова вправо или влево на требуемое число разрядов;

преобразование последовательного кода слова в параллельный и наоборот;

поразрядные логические операции.

Регистры делятся на параллельные и последовательные (сдвигающие).

Параллельные регистры

В параллельных регистрах прием и выдача слов производятся по всем разрядам одновременно. В них могут осуществляться также поразрядные операции над словами.

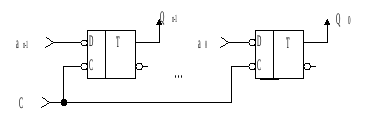

В последовательных регистрах слова принимаются и выдаются разряд за разрядом. Их также называют сдвигающими, так как тактирующие сигналы сдвигают хранимое в регистре слово влево или вправо.

Последовательно-параллельные регистры одновременно имеют входы как для последовательного, так и параллельного приема/выдачи слов. Они могут выполнять взаимное преобразование последовательных кодов в параллельные и наоборот.

Параллельный регистр на рис.19 принимает слово за два такта: в первом такте все триггеры устанавливаются в нулевое состояние, во втором такте переключаются в логическую 1 те триггеры, на входы которых поступают единичные сигналы ai.

Рис.19. Параллельный регистр на основе RS-триггеров с однофазным входом и выходом.

В схеме на D-триггерах (рис.20) параллельный код подается на входы an-1...a0. Поданный код записывается в регистр импульсом записи С.

Рис.20. Параллельный регистр на D-триггерах с однофазным входом и выходом.

На

рис.21 приведены временные диаграммы

работы регистра на D-триггерах. При С=1

записываемые данные должны быть

статическими, С=0 - хранение информации.

На

рис.21 приведены временные диаграммы

работы регистра на D-триггерах. При С=1

записываемые данные должны быть

статическими, С=0 - хранение информации.

Рис.21. Временные диаграммы работы регистра на D- триггерах

Рис.22. Параллельный регистр на RS - триггерах с парафазными входами и выходами.

Видим, что параллельные регистры состоят из разрядных схем, не связанных между собой.