- •Часть 2

- •Глава 4. Логические элементы и устройства систем автоматики 7

- •Глава 5. Вычислительные средства обработки информации в системах автоматики 63

- •Глава 6. Исполнительные устройства и регулирующие органы систем автоматики 158

- •Глава 4. Логические элементы и устройства систем автоматики

- •4.1. Логические элементы

- •4.2. Функциональные узлы комбинационного типа

- •4.2.1. Шифраторы и дешифраторы

- •4.2.2. Мультиплексоры

- •4.2.3. Сумматоры

- •4.2.4. Цифровые компараторы

- •4.3. Функциональные узлы последовательностного типа

- •4.3.1. Асинхронные триггеры

- •4.3.2. Синхронные триггеры

- •4.3.3. Регистры параллельного действия

- •4.3.4. Регистры последовательного действия.

- •4.3.5. Счетчики

- •4.4. Схемотехника запоминающих устройств

- •4.4.1. Запоминающие устройства эвм

- •4.4.2. Запоминающие элементы статических озу

- •4.4.3. Оперативные запоминающие устройства динамического типа

- •4.4.4. Постоянные запоминающие устройства

- •4.4.5. Перепрограммируемые пзу, Flash-память

- •4.4.6. Построение модуля озу заданной емкости

- •4.5. Цифро-аналоговые и аналого-цифровые преобразователи

- •4.5.1. Цифро-аналоговые преобразователи

- •4.5.2. Аналого-цифровые преобразователи параллельного кодирования

- •4.5.3. Аналого-цифровые преобразователи последовательного кодирования

- •4.6. Программируемые логические матрицы и интегральные схемы

- •Глава 5. Вычислительные средства обработки информации в системах автоматики

- •5.1. Микропроцессоры в системах автоматизации текстильного производства

- •5.1.1. Архитектура микропроцессорных устройств

- •5.1.2. Классификация микропроцессоров

- •5.1.3. Взаимодействие микропроцессора с внешними устройствами

- •5.1.4. Структура типового микропроцессорного комплекта

- •5.1.5. Однокристальные микроконтроллеры

- •5.1.6. Программируемые логические контроллеры

- •5.2. Вычислительные машины и вычислительные системы асу тп текстильных производств

- •5.2.1. Эвм общего назначения

- •5.2.2. Специализированные эвм и вычислительные комплексы

- •5.2.3. Рабочие станции

- •5.3. Сетевые компоненты систем автоматики

- •5.3.1. Локальные управляющие вычислительные сети

- •5.3.2. Топологии локальных сетей

- •5.3.3. Сетевые среды

- •5.4. Промышленные интерфейсы и протоколы

- •5.4.1. Интерфейс стандарта rs-232

- •5.4.2. Интерфейсы стандартов eia rs‑422a/rs-485

- •5.4.3. Интерфейс и протокол can

- •5.4.4. Шина usb

- •5.4.5. Протокол profibus

- •5.4.6. Протокол modbus

- •5.5. Программные средства автоматизации

- •5.5.1. Структура программного обеспечения

- •5.5.2. Системное программное обеспечение

- •5.5.3. Прикладное программное обеспечение

- •5.5.4. Инструментальные средства разработки, отладки и сопровождения программного обеспечения

- •5.5.5. Системы scаda

- •Глава 6. Исполнительные устройства и регулирующие органы систем автоматики

- •6.1. Электрические исполнительные механизмы

- •6.1.1. Электромагнитные исполнительные элементы

- •6.1.2. Электродвигательные исполнительные устройства

- •6.1.3. Двигатель постоянного тока как элемент исполнительных механизмов

- •6.1.4. Двухфазный асинхронный двигатель как элемент исполнительных механизмов

- •6.1.5. Трехфазный асинхронный двигатель как элемент исполнительных механизмов

- •6.1.6. Синхронный двигатель как элемент исполнительных механизмов

- •6.2. Автоматизированный электропривод

- •6.2.1. Асинхронные электроприводы со скалярным управлением

- •6.2.2. Асинхронные электроприводы с векторным управлением

- •6.2.3. Вентильные и бесконтактные машины постоянного тока

- •6.3. Силовые полупроводниковые преобразователи в системе автоматизированного электропривода

- •6.3.1. Управляемые выпрямители

- •6.3.2. Широтно-импульсные преобразователи

- •6.3.3. Автономные инверторы

- •6.3.4. Непосредственные преобразователи частоты

- •6.4. Пневматические исполнительные механизмы

- •6.5. Регулирующие органы. Классификация и области применения

- •Список литературы

4.5.3. Аналого-цифровые преобразователи последовательного кодирования

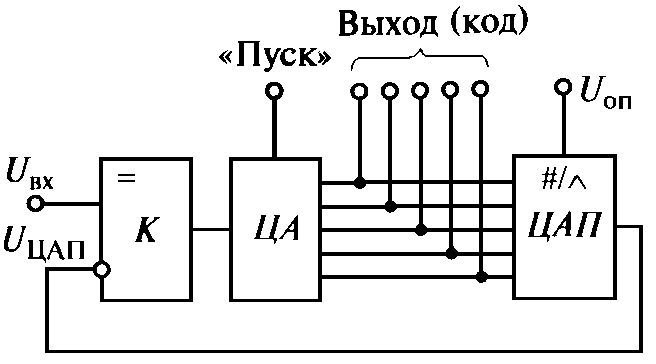

На рис. 4.41 показана схема АЦП последовательного типа.

Рис. 4.41. Схема аналого-цифрового преобразователя последовательного типа

По команде «Пуск» цифровой автомат ЦА вырабатывает последовательность двоичных чисел, которые поступают на вход цифро-аналогового преобразователя ЦАП, вырабатывающего напряжение Uцап, соответствующее каждому входному двоичному сигналу. Это напряжение (непрерывно растущее, пока работает ЦА) подается на один из входов компаратора K, на другой вход которого поступает входное напряжение Uвх. Компаратор сравнивает эти два напряжения и выдает сигнал при их равенстве. По этому сигналу ЦА останавливается, а на его выходе фиксируется двоичный код, соответствующий Uвх. Таким образом, преобразование в последовательном АЦП происходит в ступенчатом режиме. Выходное значение отдельными шагами (тактами), т.е. последовательно, приближается к измеряемому значению. Поэтому последовательные АЦП на каждое преобразование аналогового сигнала затрачивают много времени. Для повышения их быстродействия используется метод поразрядного уравновешивания. Иллюстрирующая этот метод схема показана на рис. 4.42.

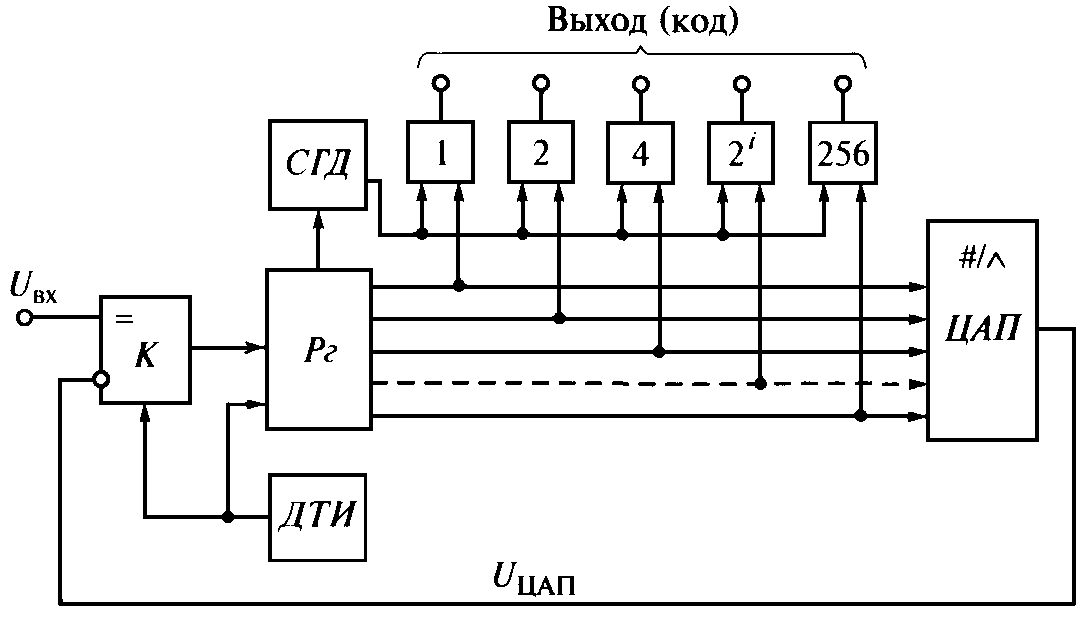

Рис. 4.42. Схема аналого-цифрового преобразователя с поразрядным уравновешиванием

Роль цифрового автомата выполняет регистр Рг с датчиком тактовых импульсов ДТИ. Считывание выходного кода происходит по сигналу схемы готовности данных СГД, который подается при поступлении сигнала от компаратора K о равенстве входного напряжения Uвх и напряжения Uцап. Работа компаратора синхронизирована импульсами ДТИ. Эти же импульсы последовательно переводят разряды регистра Рг в состояние 1. Перевод начинается со старшего разряда, а младшие остаются в состоянии 0. При этом ЦАП вырабатывает соответствующее напряжение, которое сравнивается в компараторе K с входным. Если Uцап > Uвх, то по команде компаратора старший разряд сбрасывается в состояние 0; если Uцап < Um, то в старшем разряде остается 1. Затем в состояние 1 переводится следующий по старшинству разряд Рг и снова производится сравнение напряжений Uцап и Uвх. Цикл повторяется до тех пор, пока не будет зафиксировано равенство указанных напряжений при переводе в состояние 1 какого-то из младших разрядов. После этого СГД подает сигнал о выдаче выходного кода. Число циклов сравнения в таком АЦП будет равно числу разрядов выходного кода.

4.6. Программируемые логические матрицы и интегральные схемы

В организации ПЗУ и программируемых логических матриц (ПЛМ) много общего. Выявим общий подход в построении этих схем на примере.

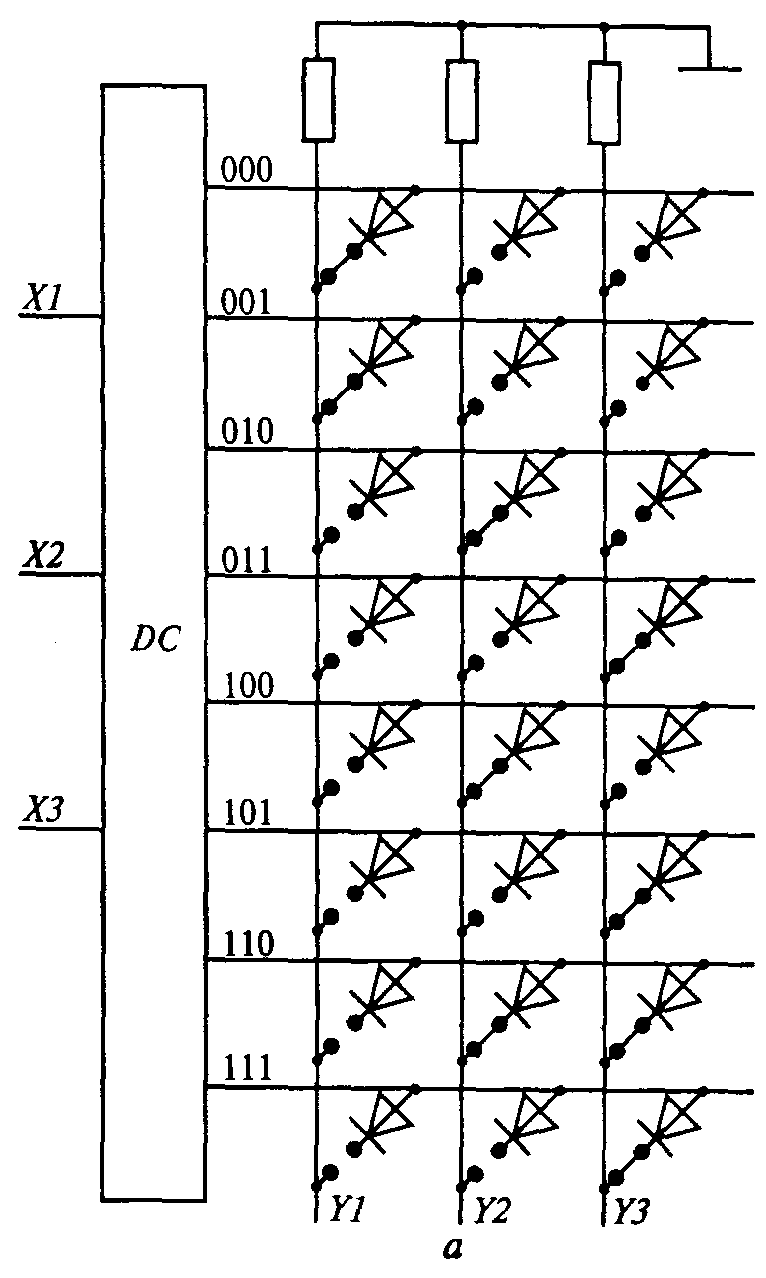

Предположим, что необходимо построить устройство, которое обеспечивает выдачу сигнала на выходе Y1 при поступлении на вход кодов 000, 001; на выходе Y2 при кодах 010, 100, 110; на выходе Y3 при кодах 011, 101, 110, 111. Подаваемые на вход устройства коды можно рассматривать как коды адреса одноразрядных ячеек ПЗУ, из которых считываемые единицы через элемент ИЛИ поступают на один из выходов Yi. Рассмотрим взаимосвязь между адресами и данными – функциями (табл. 4.13).

На рис. 4.43, а представлена схема ПЗУ, состоящая из дешифратора адреса на логических элементах и запоминающих элементов в виде диодно-резистивных схем, в цепи которых включены перемычки. Переменные Х3, Х2, X1 рассматриваются как коды адресов различных ячеек памяти. Из табл. 4.13 видно, что в дешифраторе при определенных адресах возбуждаются соответствующие выходные шины, которые должны быть объединены на одном из выходов схемы: Y1, Y2, Y3. Элементы ИЛИ, с помощью которых формируются сигналы Yi, представляют собой неполный шифратор.

Таблица 4.13

Таблица истинности дешифратора

Адрес |

Входы |

Выходы |

||||

|

Х3 |

Х2 |

XI |

Y1 |

Y2 |

Y3 |

А0 A1 А2 A3 А4 А5 А6 А7 |

0 0 0 0 1 1 1 1 |

0 0 1 1 0 0 1 1 |

0 1 0 1 0 1 0 1 |

1 1 0 0 0 0 0 0 |

0 0 1 0 1 0 1 0 |

0 0 0 1 0 1 1 1 |

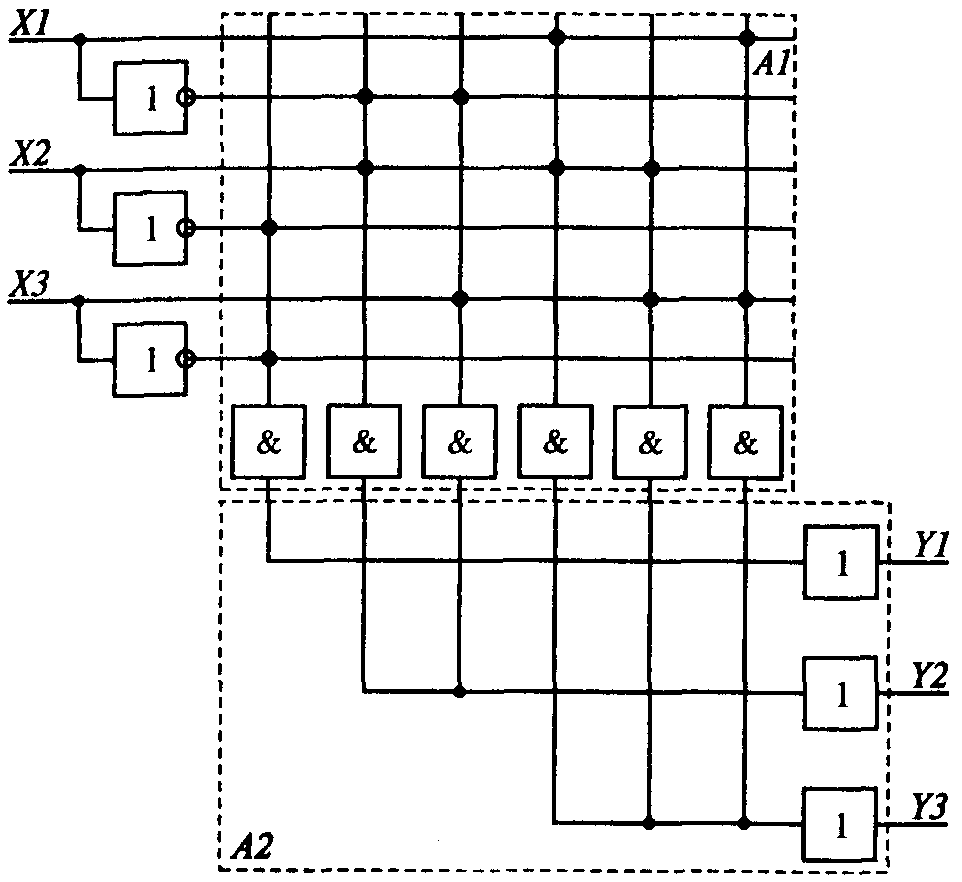

На рис. 4.43, б представлена та же схема ПЗУ в виде двух матриц. Матрица А1 представляет собой полный линейный дешифратор на восемь выходов. Каждая вертикальная линия в А1 соответствует элементу И с тремя входами, на каждом из которых реализовано одно из сочетаний входных переменных Х3, Х2, X1. Матрица А2 представляет собой неполный шифратор.

а

б

Рис. 4.43. Матрица ПЗУ, как основа ПЛМ

Каждая горизонтальная линия в А2 соответствует восьмивходовому элементу ИЛИ. О формировании необходимых сигналов на каждом из его входов говорит точка в месте пересечения вертикальной линии матрицы А1 и горизонтальной линии матрицы А2.

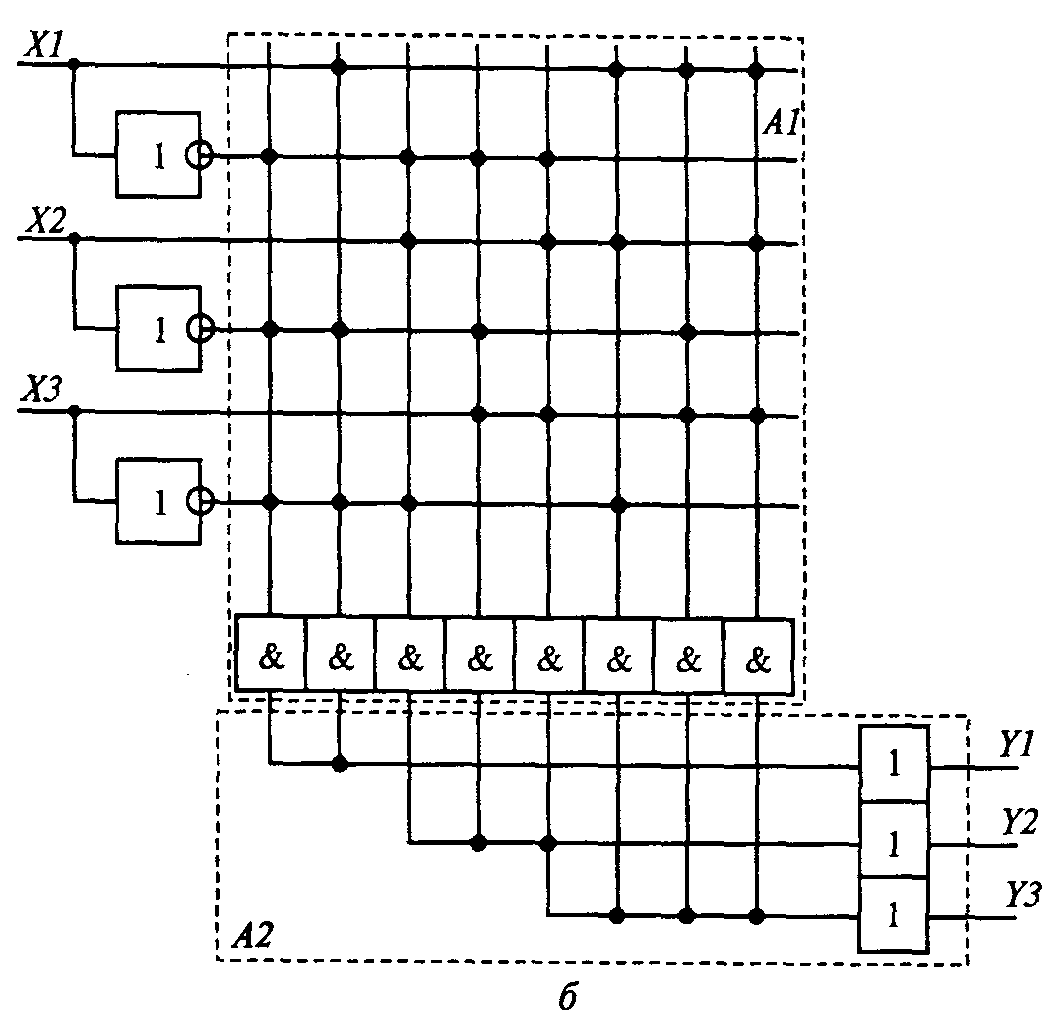

Схемы, приведенные на рис. 4.43 могут быть реализованы в виде комбинационной схемы на ПЛМ (рис. 4.44).

Рис. 4.44. Комбинационная схема на ПЛМ

Сравнивая две схемы, выполняющие одни и те же функции (см. рис. 4.43, б и 4.44), видим, что схема, реализованная в виде ПЛМ, проще. Матрица А1 в ПЗУ – это полный, жестко программируемый дешифратор, в матрице ПЛМ – это программируемые под функции минтермы. Затраты на оборудование принято определять площадью полупроводникового кристалла, занимаемого схемой. Таким образом, схемы, выполненные на ПЛМ, обеспечивают большую степень интеграции и тем самым расширяют функциональные возможности микросхемы.