- •Часть 2

- •Глава 4. Логические элементы и устройства систем автоматики 7

- •Глава 5. Вычислительные средства обработки информации в системах автоматики 63

- •Глава 6. Исполнительные устройства и регулирующие органы систем автоматики 158

- •Глава 4. Логические элементы и устройства систем автоматики

- •4.1. Логические элементы

- •4.2. Функциональные узлы комбинационного типа

- •4.2.1. Шифраторы и дешифраторы

- •4.2.2. Мультиплексоры

- •4.2.3. Сумматоры

- •4.2.4. Цифровые компараторы

- •4.3. Функциональные узлы последовательностного типа

- •4.3.1. Асинхронные триггеры

- •4.3.2. Синхронные триггеры

- •4.3.3. Регистры параллельного действия

- •4.3.4. Регистры последовательного действия.

- •4.3.5. Счетчики

- •4.4. Схемотехника запоминающих устройств

- •4.4.1. Запоминающие устройства эвм

- •4.4.2. Запоминающие элементы статических озу

- •4.4.3. Оперативные запоминающие устройства динамического типа

- •4.4.4. Постоянные запоминающие устройства

- •4.4.5. Перепрограммируемые пзу, Flash-память

- •4.4.6. Построение модуля озу заданной емкости

- •4.5. Цифро-аналоговые и аналого-цифровые преобразователи

- •4.5.1. Цифро-аналоговые преобразователи

- •4.5.2. Аналого-цифровые преобразователи параллельного кодирования

- •4.5.3. Аналого-цифровые преобразователи последовательного кодирования

- •4.6. Программируемые логические матрицы и интегральные схемы

- •Глава 5. Вычислительные средства обработки информации в системах автоматики

- •5.1. Микропроцессоры в системах автоматизации текстильного производства

- •5.1.1. Архитектура микропроцессорных устройств

- •5.1.2. Классификация микропроцессоров

- •5.1.3. Взаимодействие микропроцессора с внешними устройствами

- •5.1.4. Структура типового микропроцессорного комплекта

- •5.1.5. Однокристальные микроконтроллеры

- •5.1.6. Программируемые логические контроллеры

- •5.2. Вычислительные машины и вычислительные системы асу тп текстильных производств

- •5.2.1. Эвм общего назначения

- •5.2.2. Специализированные эвм и вычислительные комплексы

- •5.2.3. Рабочие станции

- •5.3. Сетевые компоненты систем автоматики

- •5.3.1. Локальные управляющие вычислительные сети

- •5.3.2. Топологии локальных сетей

- •5.3.3. Сетевые среды

- •5.4. Промышленные интерфейсы и протоколы

- •5.4.1. Интерфейс стандарта rs-232

- •5.4.2. Интерфейсы стандартов eia rs‑422a/rs-485

- •5.4.3. Интерфейс и протокол can

- •5.4.4. Шина usb

- •5.4.5. Протокол profibus

- •5.4.6. Протокол modbus

- •5.5. Программные средства автоматизации

- •5.5.1. Структура программного обеспечения

- •5.5.2. Системное программное обеспечение

- •5.5.3. Прикладное программное обеспечение

- •5.5.4. Инструментальные средства разработки, отладки и сопровождения программного обеспечения

- •5.5.5. Системы scаda

- •Глава 6. Исполнительные устройства и регулирующие органы систем автоматики

- •6.1. Электрические исполнительные механизмы

- •6.1.1. Электромагнитные исполнительные элементы

- •6.1.2. Электродвигательные исполнительные устройства

- •6.1.3. Двигатель постоянного тока как элемент исполнительных механизмов

- •6.1.4. Двухфазный асинхронный двигатель как элемент исполнительных механизмов

- •6.1.5. Трехфазный асинхронный двигатель как элемент исполнительных механизмов

- •6.1.6. Синхронный двигатель как элемент исполнительных механизмов

- •6.2. Автоматизированный электропривод

- •6.2.1. Асинхронные электроприводы со скалярным управлением

- •6.2.2. Асинхронные электроприводы с векторным управлением

- •6.2.3. Вентильные и бесконтактные машины постоянного тока

- •6.3. Силовые полупроводниковые преобразователи в системе автоматизированного электропривода

- •6.3.1. Управляемые выпрямители

- •6.3.2. Широтно-импульсные преобразователи

- •6.3.3. Автономные инверторы

- •6.3.4. Непосредственные преобразователи частоты

- •6.4. Пневматические исполнительные механизмы

- •6.5. Регулирующие органы. Классификация и области применения

- •Список литературы

4.4.3. Оперативные запоминающие устройства динамического типа

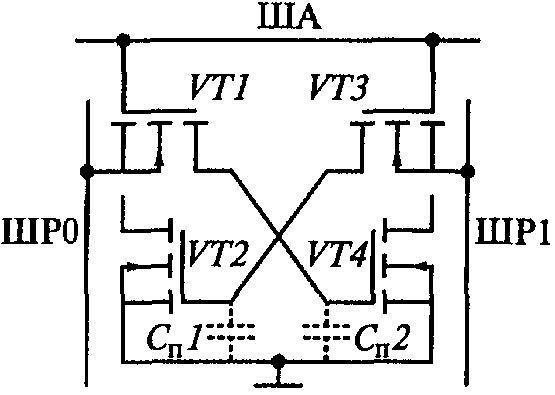

Запоминающие элементы динамических ОЗУ построены на базе МОП-транзисторов. Здесь используется тот факт, что у МОП-транзистора высокое входное сопротивление. Это позволило построить схемы ЗЭ, у которых входной ток близок к нулю. В основу положен принцип накопления и восстановления – регенерации – заряда на затворе МОП транзистора. Основой ЗЭ является паразитная емкость Сп, накапливающая заряд. Из-за постепенного разряда Сп за счет токов утечки необходимы схемы восстановления, регенерации заряда. Периодическое, а не постоянное поступление энергии в ЗЭ позволяет сократить потребляемую мощность и упростить схему, что снижает размер площади и увеличивает плотность компоновки на кристалле. На рис. 4.30 приведена схема ЗЭ динамического типа. В режиме записи VT1 и VT3 совмещают функции возбуждения разрядных шин и нагрузки для транзисторов триггера VT2, VT4.

В режиме записи подаются положительный импульс в адресную шину ША и отрицательный – в разрядную шину ШР0 либо ШР1 в зависимости от того, записывается логический «0» или логическая «1». При этом VT1 или VT3 открывается, информация заносится в триггер. Информация хранится в виде зарядов паразитных емкостей Сп1 и Сп2, причем «0» хранится неограниченное время, а «1» из-за токов утечки должна периодически восстанавливаться. Для регенерации информации периодически возбуждается шина ША и одновременно на разрядные шины подается одинаковое по знаку напряжение низкого уровня в случае p-канальных транзисторов. В этом состоит одна из отличительных особенностей динамических ОЗУ.

Рис. 4.30. Динамические ЗЭ на МОП-транзисторе

В режиме считывания возбуждают ША, как бы подключая источник питания к триггеру, и ток считывания через VT1 или VT3 поступает в соответствующую ШР – в ШР0, если хранился «0», или в ШР1, если хранилась «1».

4.4.4. Постоянные запоминающие устройства

Хранящаяся в ПЗУ информация не изменяется в процессе решения задачи. Она записывается заблаговременно при изготовлении устройств и может быть произвольной. ПЗУ часто обозначают ROM (read only memory). В ПЗУ универсальных ЭВМ хранятся константы, стандартные подпрограммы, контрольные программы – тесты и т.п. В виде ПЗУ выполняется микропрограммное устройство управления, в котором хранятся микропрограммы.

В специализированных ЭВМ, работающих в ряде случаев без вмешательства оператора, в ПЗУ хранятся основные программы работы ЭВМ. ПЗУ могут выполнять роль кодирующих и декодирующих устройств, могут использоваться для выполнения арифметических операций табличным способом.

ПЗУ проще, дешевле и надежнее ОЗУ, поскольку в них отсутствуют схемы записи информации, и для хранения информации могут применяться более простые и дешевые элементы. Простота элементов матрицы ПЗУ, а также отсутствие цепей регенерации позволяют получить период обращения к ПЗУ в несколько раз меньший, чем период обращения к ОЗУ. В ПЗУ, предназначенных для хранения констант и команд, период обращения обычно делается равным периоду обращения к ОЗУ.

Программируемые постоянные запоминающие устройства (ППЗУ) отличаются от ППЗУ тем, что пользователь может самостоятельно запрограммировать ПЗУ – ввести в него программу с помощью специального устройства программатора, но только один раз: после введения программы содержимое памяти изменить нельзя.

Репрограммируемое постоянное запоминающее устройство (РПЗУ), называемое также стираемым ПЗУ, допускает неоднократное стирание информации и запись новой с помощью программатора. Это облегчает исправление обнаруженных ошибок и позволяет изменять содержимое памяти.

Структурная схема ПЗУ аналогична структурной схеме ОЗУ. Различие состоит в том, что в ПЗУ отсутствуют схемы, предназначенные для записи информации. Матрица накопителя информации обычно организуется по системе 2D. В узлах матриц располагаются запоминающие элементы, иногда называемые для ПЗУ элементами связи (ЭС). ЭС связывают между собой электрически (или не связывают) адресные и разрядные шины. Наличие ЭС соответствует коду «1», отсутствие ЭС – коду «0».

Полупроводниковые ЭС могут быть диодными и транзисторными. На рис. 4.31 приведены схемы ЭС полупроводниковых ППЗУ и РПЗУ ( – программируемая маскированием перемычка; ~ – плавная перемычка). Наибольшую емкость при наименьшей потребляемой мощности имеют ПЗУ, построенные на n-канальных МОП-транзисторах (см. рис. 4.31, б). В масочных ПЗУ (см. рис. 4.31, а...в) информация записывается при изготовлении ПЗУ на заводе с помощью соответствующих фотошаблонов.

При программировании изготовителем или заказчиком ППЗУ часть плавких перемычек ЭС типа приведенных (см. рис. 4.31, г, д) расплавляется импульсами тока, которые пропускают через определенные эмиттеры согласно карте заказа. В результате нарушаются некоторые связи источника питания с разрядными шинами, что обеспечивает при считывании появление логических «0» в определенных разрядах числа (слова). Занести новую информацию в ППЗУ невозможно, так как нарушенные связи восстановлению не поддаются.

Рис. 4.31. Запоминающие элементы полупроводниковых ППЗУ и РПЗУ: а, б, в – ППЗУ, программируемые маскированием; г, д – ППЗУ, программируемые выжиганием плавких перемычек; е, ж, з – РПЗУ