- •Часть 2

- •Глава 4. Логические элементы и устройства систем автоматики 7

- •Глава 5. Вычислительные средства обработки информации в системах автоматики 63

- •Глава 6. Исполнительные устройства и регулирующие органы систем автоматики 158

- •Глава 4. Логические элементы и устройства систем автоматики

- •4.1. Логические элементы

- •4.2. Функциональные узлы комбинационного типа

- •4.2.1. Шифраторы и дешифраторы

- •4.2.2. Мультиплексоры

- •4.2.3. Сумматоры

- •4.2.4. Цифровые компараторы

- •4.3. Функциональные узлы последовательностного типа

- •4.3.1. Асинхронные триггеры

- •4.3.2. Синхронные триггеры

- •4.3.3. Регистры параллельного действия

- •4.3.4. Регистры последовательного действия.

- •4.3.5. Счетчики

- •4.4. Схемотехника запоминающих устройств

- •4.4.1. Запоминающие устройства эвм

- •4.4.2. Запоминающие элементы статических озу

- •4.4.3. Оперативные запоминающие устройства динамического типа

- •4.4.4. Постоянные запоминающие устройства

- •4.4.5. Перепрограммируемые пзу, Flash-память

- •4.4.6. Построение модуля озу заданной емкости

- •4.5. Цифро-аналоговые и аналого-цифровые преобразователи

- •4.5.1. Цифро-аналоговые преобразователи

- •4.5.2. Аналого-цифровые преобразователи параллельного кодирования

- •4.5.3. Аналого-цифровые преобразователи последовательного кодирования

- •4.6. Программируемые логические матрицы и интегральные схемы

- •Глава 5. Вычислительные средства обработки информации в системах автоматики

- •5.1. Микропроцессоры в системах автоматизации текстильного производства

- •5.1.1. Архитектура микропроцессорных устройств

- •5.1.2. Классификация микропроцессоров

- •5.1.3. Взаимодействие микропроцессора с внешними устройствами

- •5.1.4. Структура типового микропроцессорного комплекта

- •5.1.5. Однокристальные микроконтроллеры

- •5.1.6. Программируемые логические контроллеры

- •5.2. Вычислительные машины и вычислительные системы асу тп текстильных производств

- •5.2.1. Эвм общего назначения

- •5.2.2. Специализированные эвм и вычислительные комплексы

- •5.2.3. Рабочие станции

- •5.3. Сетевые компоненты систем автоматики

- •5.3.1. Локальные управляющие вычислительные сети

- •5.3.2. Топологии локальных сетей

- •5.3.3. Сетевые среды

- •5.4. Промышленные интерфейсы и протоколы

- •5.4.1. Интерфейс стандарта rs-232

- •5.4.2. Интерфейсы стандартов eia rs‑422a/rs-485

- •5.4.3. Интерфейс и протокол can

- •5.4.4. Шина usb

- •5.4.5. Протокол profibus

- •5.4.6. Протокол modbus

- •5.5. Программные средства автоматизации

- •5.5.1. Структура программного обеспечения

- •5.5.2. Системное программное обеспечение

- •5.5.3. Прикладное программное обеспечение

- •5.5.4. Инструментальные средства разработки, отладки и сопровождения программного обеспечения

- •5.5.5. Системы scаda

- •Глава 6. Исполнительные устройства и регулирующие органы систем автоматики

- •6.1. Электрические исполнительные механизмы

- •6.1.1. Электромагнитные исполнительные элементы

- •6.1.2. Электродвигательные исполнительные устройства

- •6.1.3. Двигатель постоянного тока как элемент исполнительных механизмов

- •6.1.4. Двухфазный асинхронный двигатель как элемент исполнительных механизмов

- •6.1.5. Трехфазный асинхронный двигатель как элемент исполнительных механизмов

- •6.1.6. Синхронный двигатель как элемент исполнительных механизмов

- •6.2. Автоматизированный электропривод

- •6.2.1. Асинхронные электроприводы со скалярным управлением

- •6.2.2. Асинхронные электроприводы с векторным управлением

- •6.2.3. Вентильные и бесконтактные машины постоянного тока

- •6.3. Силовые полупроводниковые преобразователи в системе автоматизированного электропривода

- •6.3.1. Управляемые выпрямители

- •6.3.2. Широтно-импульсные преобразователи

- •6.3.3. Автономные инверторы

- •6.3.4. Непосредственные преобразователи частоты

- •6.4. Пневматические исполнительные механизмы

- •6.5. Регулирующие органы. Классификация и области применения

- •Список литературы

4.4.2. Запоминающие элементы статических озу

Микросхемы памяти изготовляются методами полупроводниковой технологии при использовании в качестве исходных материалов кремния, арсенида галлия, аморфных полупроводников или структур «кремний на сапфире». В настоящее время кремний остается основным материалом для изготовления микросхем памяти.

Особенности различных типов микросхем памяти определяются типом использованных в них запоминающих элементов, дешифраторов, формирователей сигналов записи-считывания и буферных каскадов. В большинстве статических микросхем памяти эти схемы реализованы на базе биполярных элементов ТТЛ, ТТЛШ, ЭСЛ или на базе элементов КМОП структур.

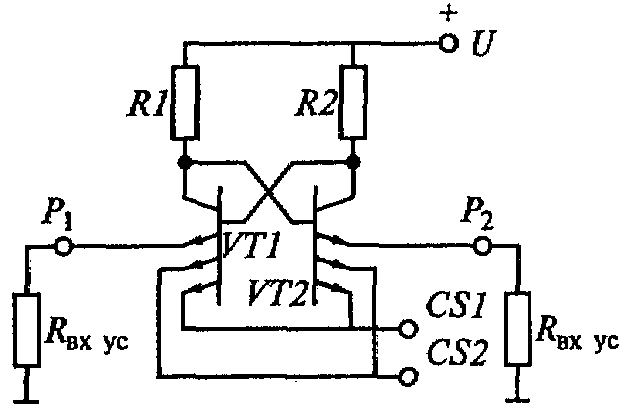

На рис. 4.29 приведена принципиальная электрическая схема ЗЭ на биполярных транзисторах. Данный элемент использует технологию ТТЛ и предназначен для применения в ЗУ с двухмерной адресацией. Его основу составляют два инвертора, выполненных на трехэмиттерных транзисторах VT1 и VT2. Инверторы включены последовательно и охвачены глубокой положительной обратной связью (ПОС). Две пары попарно объединенных эмиттеров транзисторов образуют выводы выборки элемента CS1 и CS2. Третья пара эмиттеров транзисторов образует прямой Р1 и инверсный Р2 выходы элемента, которые через входные сопротивления усилителя считывания (см. рис. 4.29) подключены к общей шине.

Рис. 4.29. Принципиальная электрическая схема ЗЭ на основе биполярных транзисторов

В режиме хранения на один или оба выхода выборки (CS1, CS2) ЗЭ подается напряжение низкого уровня. При этом триггер, образованный инверторами, находится в одном из устойчивых состояний. Предположим, что транзистор VT1 насыщен, a VT2 заперт. Весь ток насыщенного транзистора VT1 замыкается через один из выводов выборки элемента на общую шину. Поэтому в цепи вывода Р1 ток отсутствует и информация из ЗЭ не попадает на вход усилителя считывания (URвх.ус = 0).

Для считывания информации на оба входа выборки элемента необходимо подать напряжение высокого уровня. При этом единственным путем протекания тока насыщенного транзистора остается выходной вывод Р1 ЗЭ. Этот ток создает на входном сопротивлении усилителя считывания напряжение URвх.ус, полярность которого соответствует записанной в элемент информации. Следует отметить, что при считывании из элемента информации она не теряется. При подаче на один или оба входа выборки напряжения низкого уровня триггер продолжает оставаться в том же состоянии.

При необходимости записать в элемент новую информацию на него также первоначально подаются сигналы выборки. После чего на внешних шинах устанавливается полярность напряжения, соответствующая новой информации. Для рассматриваемого случая на вывод Р1 подается напряжение высокого уровня, а на Р2 – низкого уровня. При этом, так как все цепи протекания эмиттерного тока транзистора VT1 оказываются разорванными, на его коллекторе формируется напряжение высокого уровня. Это напряжение насыщает транзистор VT2, который, формируя на своем коллекторе напряжение низкого уровня, подтверждает запертое состояние транзистора VT1. В ЗЭ записывается новая информация. После снятия с элемента сигналов выборки новая информация будет храниться в триггере до момента очередной перезаписи.