- •Часть 2

- •Глава 4. Логические элементы и устройства систем автоматики 7

- •Глава 5. Вычислительные средства обработки информации в системах автоматики 63

- •Глава 6. Исполнительные устройства и регулирующие органы систем автоматики 158

- •Глава 4. Логические элементы и устройства систем автоматики

- •4.1. Логические элементы

- •4.2. Функциональные узлы комбинационного типа

- •4.2.1. Шифраторы и дешифраторы

- •4.2.2. Мультиплексоры

- •4.2.3. Сумматоры

- •4.2.4. Цифровые компараторы

- •4.3. Функциональные узлы последовательностного типа

- •4.3.1. Асинхронные триггеры

- •4.3.2. Синхронные триггеры

- •4.3.3. Регистры параллельного действия

- •4.3.4. Регистры последовательного действия.

- •4.3.5. Счетчики

- •4.4. Схемотехника запоминающих устройств

- •4.4.1. Запоминающие устройства эвм

- •4.4.2. Запоминающие элементы статических озу

- •4.4.3. Оперативные запоминающие устройства динамического типа

- •4.4.4. Постоянные запоминающие устройства

- •4.4.5. Перепрограммируемые пзу, Flash-память

- •4.4.6. Построение модуля озу заданной емкости

- •4.5. Цифро-аналоговые и аналого-цифровые преобразователи

- •4.5.1. Цифро-аналоговые преобразователи

- •4.5.2. Аналого-цифровые преобразователи параллельного кодирования

- •4.5.3. Аналого-цифровые преобразователи последовательного кодирования

- •4.6. Программируемые логические матрицы и интегральные схемы

- •Глава 5. Вычислительные средства обработки информации в системах автоматики

- •5.1. Микропроцессоры в системах автоматизации текстильного производства

- •5.1.1. Архитектура микропроцессорных устройств

- •5.1.2. Классификация микропроцессоров

- •5.1.3. Взаимодействие микропроцессора с внешними устройствами

- •5.1.4. Структура типового микропроцессорного комплекта

- •5.1.5. Однокристальные микроконтроллеры

- •5.1.6. Программируемые логические контроллеры

- •5.2. Вычислительные машины и вычислительные системы асу тп текстильных производств

- •5.2.1. Эвм общего назначения

- •5.2.2. Специализированные эвм и вычислительные комплексы

- •5.2.3. Рабочие станции

- •5.3. Сетевые компоненты систем автоматики

- •5.3.1. Локальные управляющие вычислительные сети

- •5.3.2. Топологии локальных сетей

- •5.3.3. Сетевые среды

- •5.4. Промышленные интерфейсы и протоколы

- •5.4.1. Интерфейс стандарта rs-232

- •5.4.2. Интерфейсы стандартов eia rs‑422a/rs-485

- •5.4.3. Интерфейс и протокол can

- •5.4.4. Шина usb

- •5.4.5. Протокол profibus

- •5.4.6. Протокол modbus

- •5.5. Программные средства автоматизации

- •5.5.1. Структура программного обеспечения

- •5.5.2. Системное программное обеспечение

- •5.5.3. Прикладное программное обеспечение

- •5.5.4. Инструментальные средства разработки, отладки и сопровождения программного обеспечения

- •5.5.5. Системы scаda

- •Глава 6. Исполнительные устройства и регулирующие органы систем автоматики

- •6.1. Электрические исполнительные механизмы

- •6.1.1. Электромагнитные исполнительные элементы

- •6.1.2. Электродвигательные исполнительные устройства

- •6.1.3. Двигатель постоянного тока как элемент исполнительных механизмов

- •6.1.4. Двухфазный асинхронный двигатель как элемент исполнительных механизмов

- •6.1.5. Трехфазный асинхронный двигатель как элемент исполнительных механизмов

- •6.1.6. Синхронный двигатель как элемент исполнительных механизмов

- •6.2. Автоматизированный электропривод

- •6.2.1. Асинхронные электроприводы со скалярным управлением

- •6.2.2. Асинхронные электроприводы с векторным управлением

- •6.2.3. Вентильные и бесконтактные машины постоянного тока

- •6.3. Силовые полупроводниковые преобразователи в системе автоматизированного электропривода

- •6.3.1. Управляемые выпрямители

- •6.3.2. Широтно-импульсные преобразователи

- •6.3.3. Автономные инверторы

- •6.3.4. Непосредственные преобразователи частоты

- •6.4. Пневматические исполнительные механизмы

- •6.5. Регулирующие органы. Классификация и области применения

- •Список литературы

4.3.5. Счетчики

Для хранения информации о многоразрядном кодовом слове используются несколько триггеров, по одному на каждый разряд. В этом случае такую группу триггеров называют регистром.

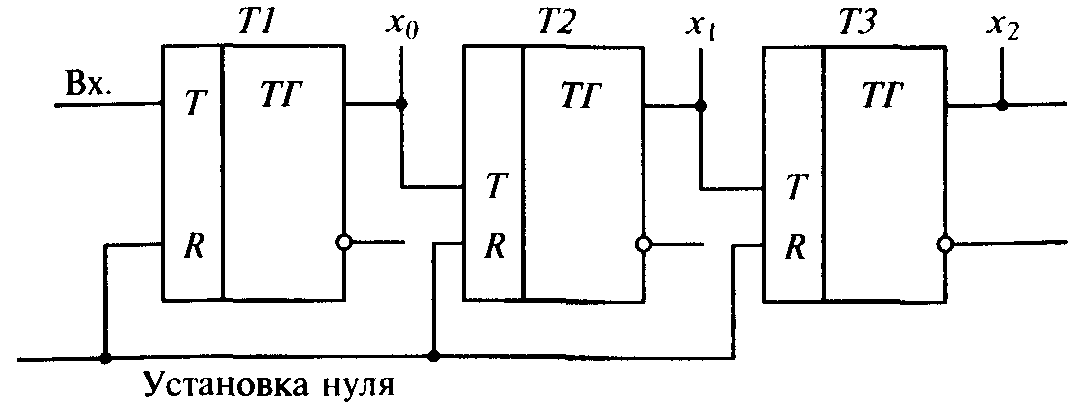

Для подсчета импульсов применяют регистры, состоящие из T-триггеров. На рис. 4.26 показан простой трехразрядный двоичный счетчик импульсов, состоящий из трех T-триггеров, которые имеют входы R для установки нуля. Временные диаграммы сигналов в таком счетчике приведены на рис. 4.27, а табл. 4.11 иллюстрирует состояние триггеров. В исходном положении все триггеры находятся в состоянии 0. После первого входного импульса триггер T1 переходит в состояние 1, после второго входного импульса в состояние 1 переходит триггер T2, а T1 возвращается в состояние 0 и т.д. Из табл. 4.11 видно, что по состоянию триггеров можно определить, сколько импульсов поступило на вход к данному моменту времени. После восьмого входного импульса все три триггера переходят в состояние 0 и счет повторяется. В общем случае емкость счетчика (т.е. коэффициент пересчета) равна 2n, где п – число триггеров в счетчике. С помощью обратных связей можно получить коэффициент пересчета меньше указанного значения.

Рис. 4.26. Трехразрядный двоичный счетчик импульсов

Рис. 4.27. Диаграммы сигналов в счетчике импульсов

Таблица 4.11

Состояния триггеров счетчика импульсов

Число входных импульсов |

Состояние триггера |

||

Т3 |

Т2 |

Т1 |

|

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

2 |

0 |

1 |

0 |

3 |

0 |

1 |

1 |

4 |

1 |

0 |

0 |

5 |

1 |

0 |

1 |

6 |

1 |

1 |

0 |

7 |

1 |

1 |

1 |

8 |

0 |

0 |

0 |

4.4. Схемотехника запоминающих устройств

4.4.1. Запоминающие устройства эвм

Память ЭВМ – функциональная часть ЭВМ, предназначенная для записи, хранения и выдачи данных. В соответствии с этим различают три режима работы памяти: записи, хранения и считывания. Запись в запоминающее устройство (ЗУ) или считывание из него информации иначе называются обращением к ЗУ. Быстродействие памяти определяется продолжительностью операции обращения к ЗУ.

Запоминающие устройства разделяют: по использованию – на внешние и внутренние (или оперативные); по назначению – на сверхоперативные, оперативные, постоянные, буферные и внешние; по физическим принципам действия – на полупроводниковые, магнитные и оптические; по способу хранения информации – на статические и динамические; по способу доступа к заданной ячейке (для адресных ЗУ) – с последовательным, циклическим и произвольным доступом; по характеру обращения – с адресным обращением (или адресной выборкой) и с ассоциативным обращением (ассоциативной выборкой) [2].

Для достижения в ЭВМ одновременно и большой информационной емкости и высокого быстродействия используется принцип иерархического построения памяти. Техническая реализация иерархических структур обеспечивает большую емкость памяти и малое время обращения, что позволяет решать на ЭВМ сложные задачи, требующие хранения большого количества данных. При иерархическом принципе построения структуры ЗУ логическая организация потоков информации должна быть такой, чтобы все информационное поле ЭВМ или ВС представлялось в виде внутреннего абстрактного ЗУ с единым адресным пространством. Это абстрактное ЗУ называют виртуальным (кажущимся) ЗУ. Адресацию его ячеек осуществляют посредством абстрактных математических адресов с использованием страничных таблиц.

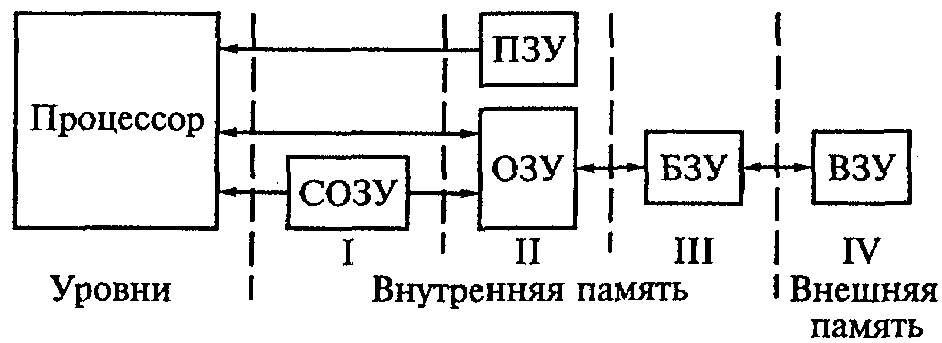

В иерархической структуре можно выделить следующие уровни памяти (рис. 4.28).

Рис. 4.28. Схема иерархии ЗУ ЭВМ

Сверхоперативные ЗУ (СОЗУ) или местная память. Они имеют быстродействие, соизмеримое с быстродействием процессора. Емкость СОЗУ обычно составляет от нескольких десятков до нескольких тысяч слов, а период обращения – десятые или сотые доли микросекунды. Они предназначаются для хранения ряда чисел, используемых некоторой текущей последовательностью команд программы. Сверхоперативные ЗУ применяют в том случае, если быстродействие процессора ограничивается быстродействием ОЗУ.

Оперативные ЗУ (ОЗУ) или основная память предназначены для хранения данных и программ текущих вычислений, а также программ, к которым следует быстро перейти, если в ходе вычислительного процесса возникло прерывание. ОЗУ современных ЭВМ имеют емкость от нескольких тысяч до сотен тысяч слов и период обращения от долей до нескольких микросекунд. ОЗУ может быть связано с процессором как непосредственными связями, так и через СОЗУ. В качестве элементов памяти ОЗУ и СОЗУ используются полупроводниковые элементы, тонкие магнитные пленки, ферритовые сердечники и др.

Постоянные ЗУ (ПЗУ) или односторонние ЗУ предназначены только для хранения и считывания информации, которая не изменяется в процессе вычислений, например постоянно используемые программы, различные константы, таблицы функций, микропрограммы и т.п. В ПЗУ информация записывается один раз при изготовлении, а при работе только считывается. Такие ПЗУ имеют меньшую аппаратную сложность, чем ОЗУ.

Буферные ЗУ (БЗУ) используются для промежуточного хранения данных при обмене между устройствами с разным быстродействием, например между ОЗУ и внешним ЗУ. По емкости и быстродействию БЗУ занимают промежуточное место между ОЗУ и внешним ЗУ. Они могут быть построены на полупроводниковых элементах, ферритовых сердечниках и на магнитных дисках.

Внешние ЗУ (ВЗУ) предназначены для хранения больших массивов информации. Объем данных, которые могут одновременно храниться в таких ЗУ, обычно превышает сотни миллионов слов, однако период обращения к ним составляет от нескольких миллисекунд до нескольких десятков секунд. Данные, хранящиеся во ВЗУ, непосредственно не используются в вычислительном процессе, а передаются из ВЗУ в ОЗУ. В качестве ВЗУ чаще всего используют накопители информации на магнитных лентах (НМЛ), на гибких и жестких магнитных дисках (НГМД, НЖМД), на микросхемах на основе материалов, содержащих цилиндрические магнитные домены (ЦМД), а также на оптических дисках.

Основой полупроводникового запоминающего элемента (ЗЭ) служит бистабильная схема триггера, состоящая из инверторов с перекрестными связями, с цепями управления для записи и считывания информации. Достоинством таких ЗЭ является единство технологического процесса изготовления как самих ЗЭ, так и элементов электронного обрамления – регистров, дешифраторов и др.

Разнообразие типов ЗЭ объясняет большое количество способов объединения ЗЭ в большие интегральные схемы (БИС), а также способов объединения БИС в накопитель.

Классификацию ЗЭ можно провести по трем типам признаков: физико-технологическим, схемотехническим и системотехническим.

По физико-технологическим признакам ЗЭ подразделяются на выполненные на биполярных транзисторах и на выполненные на МДП-транзисторах. В основе биполярных транзисторов лежат явления, происходящие в полупроводниковом блоке, содержащем в области с чередующимися типами проводимости n и р, и, следовательно, с двумя р–n-переходами, отстоящими друг от друга на расстояние, меньшее диффузионной длины неосновных носителей – электронов и «дырок». С использованием биполярной технологии разработана большая группа ЗЭ: на одноэмиттерных и многоэмиттерных транзисторах, тиристорах, инжекционных схемах.

В основе МДП-транзисторов (униполярных) лежит принцип управления проводимостью полупроводникового материала между двумя электродами при помощи электрического поля (полевые транзисторы). МДП-транзистор – активный прибор, в котором ток создается основными носителями под действием продольного электрического поля, а управление величиной тока осуществляется поперечным электрическим полем, приложенным к управляющему электроду. Существуют две разновидности МДП-транзисторов: с каналами п- и p-типов. Плотность упаковки достигает 106 бит на кристалл.

Схемотехнические признаки классификации:

число транзисторов в ЗЭ;

количество и функции адресных и разрядных шин выборки (совмещенные или раздельные функции записи, считывания, подачи питающих напряжений);

характер нагрузочных сопротивлений в триггере (линейная, нелинейная, переключаемая нагрузка);

тип связи ЗЭ с разрядными шинами (непосредственная, через ключевые элементы).

Системотехнических признаков три: принцип хранения; принцип считывания; форма и вид считанного из ЗЭ сигнала. Принципы хранения – статический, динамический и квазистатический. Принципы считывания – с разрушением (ЗЭ на ферритовых сердечниках с прямоугольной петлей гистерезиса и ЗЭ на конденсаторах) и без разрушения информации. Формы считанного из ЗЭ сигнала – однополярный сигнал, двухполярный и парафазный. И, наконец, виды считанного сигнала – импульсный ток или импульсное напряжение.