- •1. Физика работы диода. Вах диода

- •2. Характеристики и параметры диода

- •3. Разновидности диодов. Точечные диоды

- •4. Разновидности диодов. Стабилитроны

- •5. Разновидности диодов. Туннельные диоды

- •6. Разновидности диодов. Диоды Шоттки

- •7. Однополупериодный выпрямитель

- •8. Двухполупериодный выпрямитель

- •9 . Односторонний ограничитель

- •10. Двусторонний ограничитель

- •11. Биполярные транзисторы

- •12. Формулы Молла-Эберса. Вах идеального биполярного транзистора

- •13. Эквивалентная схема замещения транзистора

- •14. Параметры эквивалентной схемы замещения транзистора

- •1 5. Схемы включения транзисторов. Схема с общей базой

- •16. Схемы включения транзисторов. Схема с общим эмиттером

- •1 7. Схемы включения транзисторов. Схема с общим коллектором

- •1 8. Параметры транзистора как четырехполюсника

- •19. Работа транзистора с нагрузкой

- •20. Полевые транзисторы

- •22. Схемы включения полевых транзисторов

- •23. Обратная связь в усилителях

- •24. Коэффициент передачи усилителя, охваченного ос

- •25. Последовательная ос по напряжению

- •26. Последовательная ос по току

- •2 7. Параллельная обратная связь по напряжению

- •28. Параллельная обратная связь по току

- •29. Трехкаскадная структура операционного усилителя

- •30. Двухкаскадная структура операционного усилителя

- •3 1. Режимы работы операционных усилителей в блоках эвм

- •32. Компараторы напряжения

- •33. Функции компаратора напряжения

- •3 4. Усилители. Назначение и классификация усилителей

- •35. Основные параметры и характеристики усилителей

- •36. Выбор режима работы транзистора

- •37. Выбор рабочей точки транзисторного каскада

- •3 8. Стабильность рабочей точки транзистора и 39. Анализ температурной нестабильности транзисторного каскада

- •40. Стабильность коэффициента усиления усилителя с обратной связью

- •41. Ослабление искажений в усилителях с обратной отрицательной связью

- •4 2. Расширение полосы пропускания в усилителях с оос

- •43. Устойчивость усилителя с обратной связью

- •44. Критерий Найквиста

- •4 5. Частотная характеристика двухкаскадного усилителя оэ-оэ (двойка)

- •46. Триггеры. Основные понятия. Классификация

- •47. Одноступенчатые триггеры

- •48. Двухступенчатые триггеры

- •49. Универсальные триггеры

- •50. Регистр хранения

- •51. Регистр хранения и сдвига

- •52. Счетчики. Основные понятия. Классификация

- •53. Двоичный счетчик с последовательным переносом

- •5 4. Двоичный счетчик с параллельным переносом

- •55. Двоично-десятичный счетчик

- •56. Дешифраторы

- •57. Шифраторы

- •58. Мультиплексоры

- •59. Демультиплексоры

49. Универсальные триггеры

J K-триггер

отличается от двухступенчатого

RS-триггера тем, что в нем

отсутствует запрещенная комбинация

входных сигналов. Приведены его схема

и условное обозначение.

K-триггер

отличается от двухступенчатого

RS-триггера тем, что в нем

отсутствует запрещенная комбинация

входных сигналов. Приведены его схема

и условное обозначение.

О н

работает также как RS-триггер

с одним лишь исключением: при подаче

логической единицы на оба входа J

и K состояние выхода

триггера изменяется на противоположное.

Вход J(от Jump)

аналогичен входу S у

RS-триггера. Входа K

(Kill) аналогичен входу R.

При подаче единицы на вход J

и нуля на входа K выходное

состояние триггера становится равным

логической единицы. А при подаче единицы

на вход K и нуля на вход J

выходное состояние триггера становится

равным логическому нулю. На практике

применяются только синхронные JK-триггеры,

т.е. состояния основных входов J

и K учитываются только в

момент тактирования, например, по

положительному фронту импульса на входе

синхронизации. JK триггер

является универсальным, т.к. на его базе

можно построить D-триггер

или T-триггер. Как видно

из таблицы истинности JK-триггера,

он переходит в инверсное состояние

каждый раз при одновременной подаче на

входы J и K

логической единицы. Это свойство

позволяет создать на базе JK

триггера T-триггер,

объединив входы J и K.

Алгоритм функционирования JK-триггера

можно представить формулой:

Q(t+1)=не(Q(t))J+Q(t)*не(K).

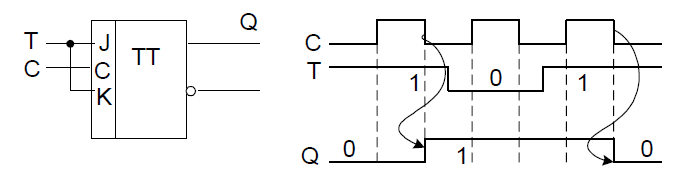

На рисунке способ построения синхронного

Т-триггера на основе JK-триггера

и временные диаграммы его работы.

н

работает также как RS-триггер

с одним лишь исключением: при подаче

логической единицы на оба входа J

и K состояние выхода

триггера изменяется на противоположное.

Вход J(от Jump)

аналогичен входу S у

RS-триггера. Входа K

(Kill) аналогичен входу R.

При подаче единицы на вход J

и нуля на входа K выходное

состояние триггера становится равным

логической единицы. А при подаче единицы

на вход K и нуля на вход J

выходное состояние триггера становится

равным логическому нулю. На практике

применяются только синхронные JK-триггеры,

т.е. состояния основных входов J

и K учитываются только в

момент тактирования, например, по

положительному фронту импульса на входе

синхронизации. JK триггер

является универсальным, т.к. на его базе

можно построить D-триггер

или T-триггер. Как видно

из таблицы истинности JK-триггера,

он переходит в инверсное состояние

каждый раз при одновременной подаче на

входы J и K

логической единицы. Это свойство

позволяет создать на базе JK

триггера T-триггер,

объединив входы J и K.

Алгоритм функционирования JK-триггера

можно представить формулой:

Q(t+1)=не(Q(t))J+Q(t)*не(K).

На рисунке способ построения синхронного

Т-триггера на основе JK-триггера

и временные диаграммы его работы.

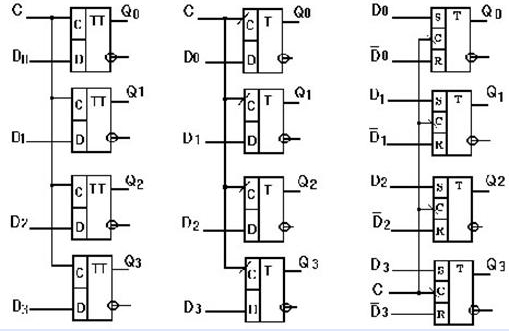

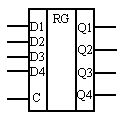

50. Регистр хранения

Регистр – внутреннее запоминающее устройство процессора или внешнего устройства, предназначенное для временного хранения обрабатываемой или управляющей информации. Регистры хранения (памяти) – регистры с параллельным приемом и выдачей информации. Они служат для хранения информации. Изменение хранящейся информации в регистре памяти (записи новой информации) осуществляется после установки на входах D0..Dm новой цифровой комбинации (информации) при поступлении определенного уровня или фронта синхросигнала (синхроимпульса) на вход «С» регистра. Количество разрядов записываемой цифровой информации определяется разрядностью регистра, которая, в свою очередь, определяется количеством триггеров, образующих этот регистр. В качестве разрядных триггеров регистра памяти используются синхронизируемые уровнем или фронтом триггеры. Регистры памяти могут быть реализованы на D-триггерах, если информация поступает на входы регистра в виде однофазных сигналов и на RS-триггерах, если информация поступает в виде парафазных сигналов. В некоторых случаях регистры могут иметь вход для установки выходов в состояние «0». Этот асинхронный вход называют входом R «сброса» триггеров регистра. На рисунке: 1-на D-триггерах, синхронизируемых уровнем синхроимпульса, 2- на D синхронизируемых фронтом; 3 – на RS синхронизируемых фронтом.

Такие регистры используются в системах оперативной памяти.