- •8.Алгебра логики. Основные понятия и тождества

- •4) Сложение (сумма) по модулю 2 (Исключающее (логическое)_или)

- •9. Минимизация логических функций. Общие сведения. Диаграммы вейча

- •10. Комбинационные схемы (мультиплексоры, сумматоры, дешифраторы, шифраторы).

- •13.Регистры. Общие сведения. Микросхемы регистров хранения, сдвига.

- •15.Запоминающие устройства. Общие сведения. Классификация микросхем памяти.

- •14. Аналого-цифровые преобразователи.

- •12. Счётчики.Классиф.Параметры.Бинарные счетчики.

- •11.Последов. Схемы. Триггеры.

11.Последов. Схемы. Триггеры.

Последовательностные схемы должны содерж-ть ячейки памяти. Простейшей такой ячейкой явл-ся триггер (состояние 1 и 0).

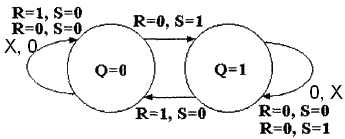

RS-триггер (R–Reset, S–Set). — триггер, который сохраняет своё предыдущее состояние при нулевых входах и меняет своё выходное состояние при подаче на один из его входов единицы.

Бывают синхронные и асинхронные триггеры.

RS – триггер может быть построен на различных логических элементах.

Асинхронный RS-триггер изм-ет свое состояние непоср-но в момент изм-ия сигнала на его инф-х входах.

![]()

![]()

![]() - логическое

выражение работы RS-триггера

- логическое

выражение работы RS-триггера

Синхронные триггеры изм-ют свое состояние лишь в строго опр-ые тактовые моменты времени, кот. сот-ют дей-ю активного сигнала на синхрониз-ом входе С.

По виду логич сигнала, действ-го на входах триг – статич(управл уровнем) димамич( управл перепадом вх сигн). Вх м.б. прямые( с 0 на 1-по фронту) инверсные.(по срезу)

Синхронный RS-триггер можно получить на базе асинхронного путем добавления входа С синхронизации. Тогда логич-ое выр-ие

![]()

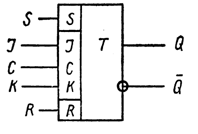

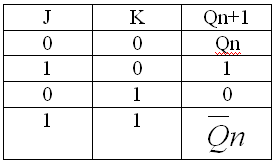

JK-триггер работает так же как RS-триггер, с одним лишь исключением: при подаче логической единицы на оба входа J и K состояние выхода триггера изменяется на противоположное. Вход J аналогичен входу S у RS-триггера. Вход K аналогичен входу R у RS-триггера. RS-триггер можно получить из JK-триггер, если приравнять J=K и S=R при запрете комбинации J=K=1. JK-триггер имеет более сложную стр-ру, его можно получить на основе двухступенчатого RS-триггера. На основе JK-триггера можно построить Д-триггер (триггер задержки) и Т-триггер (счетный триггер или делитель частоты на 2).

![]()

любой триггер хар-ся выражением:

![]()

![]() -

с учетом кода синхронизации

-

с учетом кода синхронизации

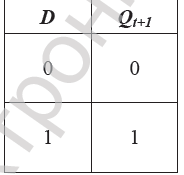

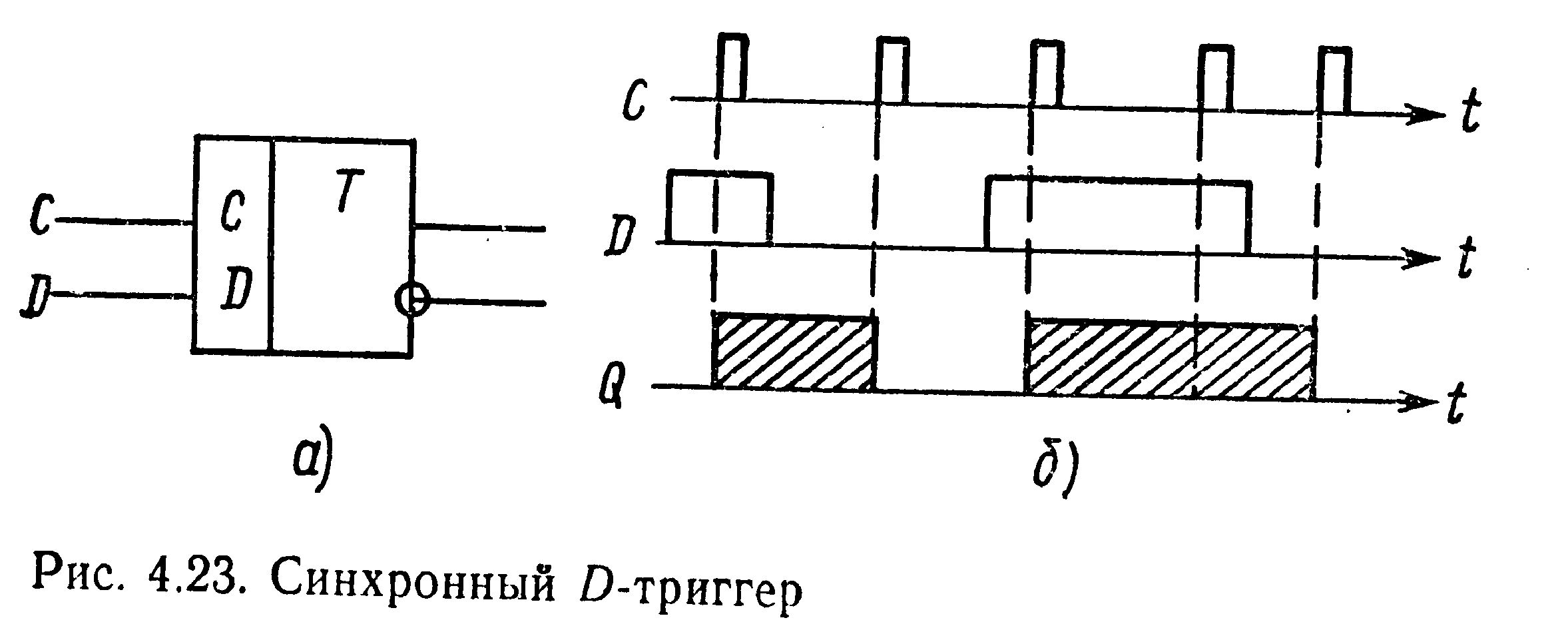

D-триггер

запоминает состояние входа и выдаёт

его на выход. D-триггеры имеют, как

минимум, два входа: информационный D

и синхронизации С.

информация на выходе остаётся неизменной

до прихода очередного импульса

синхронизации. D-триггер можно образовать

из любых RS- или JK-триггеров. В нем

![]() .

.

![]()

![]() -асинх.

-асинх.

![]() синх

синх

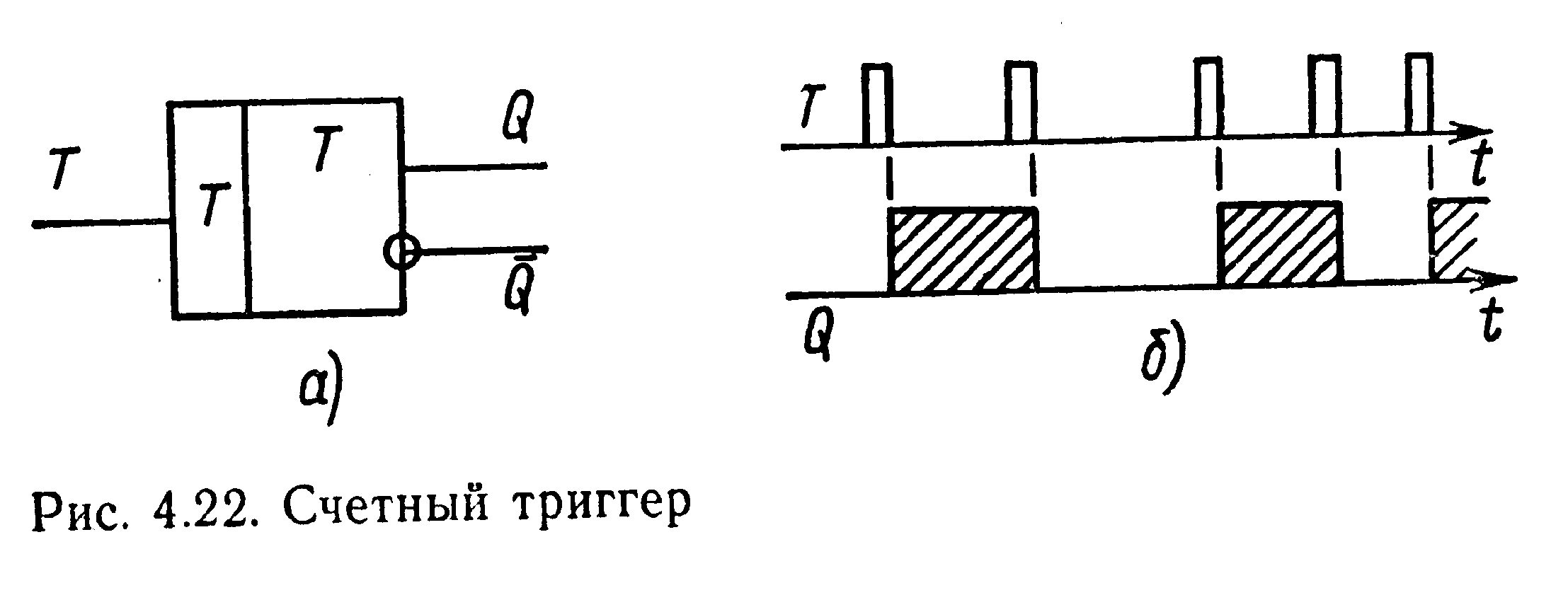

Т-триггерпо каждому такту изменяет своё логическое состояние на противоположное при единице на входе Т, и не изменяет выходное состояние при нуле на входе T. Т-триггер часто называют счётным триггером. Т-триггер может строиться как на JK, так и на D-триггерах. Можно создать на базе JK-триггера Т-триггер, объединяя входы J =К=1.

![]()