- •8.Алгебра логики. Основные понятия и тождества

- •4) Сложение (сумма) по модулю 2 (Исключающее (логическое)_или)

- •9. Минимизация логических функций. Общие сведения. Диаграммы вейча

- •10. Комбинационные схемы (мультиплексоры, сумматоры, дешифраторы, шифраторы).

- •13.Регистры. Общие сведения. Микросхемы регистров хранения, сдвига.

- •15.Запоминающие устройства. Общие сведения. Классификация микросхем памяти.

- •14. Аналого-цифровые преобразователи.

- •12. Счётчики.Классиф.Параметры.Бинарные счетчики.

- •11.Последов. Схемы. Триггеры.

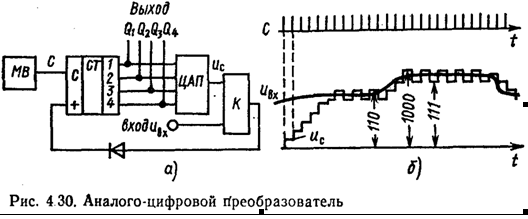

14. Аналого-цифровые преобразователи.

Схема АЦП состоит из мультивибратора генерирующего синхронизирующие (тактовые) импульсы «С» счетчика СТ подсчитывающего тактовые импульсы компаратора. Реверсивный счетчик работает на сложение, если на вход со знаком «+» подается «1», а если «0», то на вычитание. На первый вход компаратора подается вх напряжение (UВХ). Начальное состояние счетчика Q1=Q2=Q3=Q4=0. Напряжение UC является аналогом кода записанного в счетчике. (начальное состояние UС=0). Если UВХ–UС>0, сигнал компаратора будет положительным, то на вход счетчика подается «1» и счетчик работает на сложение. С каждым импульсом «С» код счетчика будет увеличиваться, пока не достигнет обратного неравенства (UВХ–UС<0). Следовательно UC на выходе ЦАП однозначно связано с кодом и код счетчика должен соответствовать вх значению. Вых сигнал АЦП снимается с разрядов реверсивного счетчика.

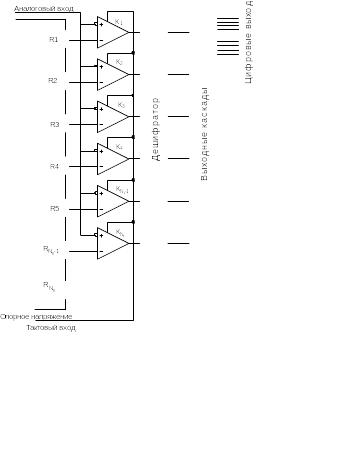

Схема параллельного ацп

Параллельные АЦП построены на принципе одновременного преобразования сигнала путем его квантования с помощью набора компараторов. Такие АЦП являются самыми быстродействующими. Построение всех параллельных АЦП однотипна: делитель опорных напряжений, набор компараторов напряжения, шифратор, выходные каскады. Такой АЦП работает следующим образом. Входной сигнал подается одновременно на одни входы компараторов, в которых он сравнивается с опорными напряжениями, подаваемыми на другие входы компараторов от делителя опорных напряжений. на выходах компараторов фиксируется значение кода: Uвх<Uоп , то 0. Затем результат кодирования с выходов компараторов подается на шифратор, в котором происходит преобразование в выбранный тип выходного кода АЦП. С выхода шифратора сформированный код подается на выходные каскады преобразователей внутрисхемных уровней в стандартные уровни ЭСЛ, ТТЛ, КМОП. Делитель опорных напряжений в параллельных АЦП служит для формирования опорных напряжений

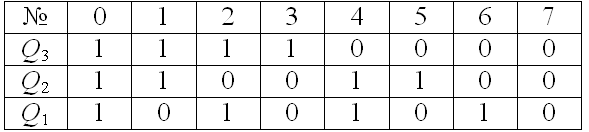

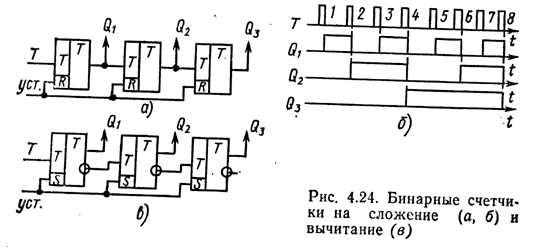

12. Счётчики.Классиф.Параметры.Бинарные счетчики.

Это устр-во, сигналы кот-го на выходе отображают число импульсв, поступивши на счетный вход. Рез-ты счета записываются в двоичном коде.Счётчики могут строиться на T-триггерах. Основной параметр счётчика — модуль счёта — максимальное число единичных сигналов, которое может быть сосчитано счётчиком.

![]() n

- число последовательно включенных

Т-триггеров.

N-число

разрядов счетчика

n

- число последовательно включенных

Т-триггеров.

N-число

разрядов счетчика

Счётчики обозначают через СТ.

Счётчики классифицируют:

1)по модулю счёта: (двоично-десятичные (декадные);двоичные (бинарные);2)с произвольным постоянным модулем счёта; с переменным модулем счёта;3)по направлению счёта: суммирующие;вычитающие;реверсивные;4)по способу формирования внутренних связей: с последовательным переносом; с параллельным переносом; кольцевые

Сч. с послед.переносом – цепочка триг.в кот.импульсы, подлежащие счету поступают на вход 1 тригера(мл.разр) а сигнал переноса последоват.от одного к др.(низкое быстрод., но простая схема).

Сч. с паралл.переносом – исп-ся синхр триггеры. Триггеры срабатывают одновременно по сигн.синх-ции (быстродействие)

Рассмотрим 3х-разрядный счетчик (3–триггера) на сложение построенный на основе Т-триггеров.

В этом счетчике каждый старший разряд перекл если пред разряд перекл. из 1 в 0. млад разр перекл всегда. Разряд исходного числа перекл если в разряде будет записана др цифра. Исх.число в сч.-число записанной в сч. Прибавляя 1 соответствует поступлению на вход импульса. 1 переносимый в след.разряд соответств. переносу перекл.перепада из одного триггера в послед. Перепадом по срезу первого вх имп. Триггер Т1 устанавлив в 1.появится перепад 0/1, значит Т2 не перекл. Поступупающий входной импульс возвращ Т1 в нулев сост.=> 1/0=> Т2 перключ в сост 1.

Вычитающий сч. – импульсы так же подаются на вход триггера млад.разр. м/у собой триггеры соед так чтобы обеспечить перекл послед когда пред. – по прямому выходу переходит из 0 в 1. Для этого счетный вхож послед.триг.следует соед. с инверсн выходом предыдущ., на кот будет перепад 1/0, являющийся переключающим.

Реверсивн.-работает как на сложение так и на вычитание, имеют спец.вход, кот управляет направлением счета.

Если N=2n-1, то счетчик называется бинарным (двоичным), а в случае, если N2n-1, то счетчики называются счетчиками с произвольным коэффициентом счета (счетчики на 10, 12 импульсов).