- •1.1. Микропроцессор и его архитектура

- •1.2. Типы мп бис

- •1.3. Универсальные микропроцессоры и их основные характеристики

- •1.4. Однокристальные микроконтроллеры: особенности архитектуры, основные характеристики, область применения.

- •2.1. Структура мк-51. Основные функциональные блоки и их назначение

- •2.2. Организация памяти программ и памяти данных

- •1. Память данных:

- •2. Память программ:

- •2.3. Аппаратные и программные средства микроконтроллера для обработки битовой информации

- •1. Аппаратные.

- •2. Программные.

- •2.4. Система прерывания

- •2.5. Блок таймеров/счетчиков: назначение, структура, режимы работы, применение

- •2.6. Организация последовательного ввода/вывода в микроконтроллере

- •3.1. Структура универсального мп. Основные функциональные блоки и их назначение.

- •3.2. Регистровая структура 32-разрядного мп

- •1 ) Основные функциональные регистры

- •1.1) Регистры общего назначения

- •3.1) Регистры управления.

- •3 .2) Регистры системных адресов и системных сегментов

- •3.3. Организация памяти. Физическое адресное пространство. Логическое адресное пространство (лап): линейное, сегментированное, страничное, сегментно-страничное

- •3.5. Структура расширенного кода команды x86. Вычисление процессором смещения

- •3.8. Механизмы защиты в 32-разрядном микропроцессоре. Защита при управлении памятью. Защита по привилегиям. Механизмы передачи управления между программами на разных уровнях привилегий. Шлюз вызова

- •3.9. Многозадачный режим работы мп, аппаратные средства поддержки многозадачности: регистр задачи, дескриптор сегмента состояния задачи, сегмент состояния задачи. Механизм переключения задач

- •3.10. Назначение, принципы работы и организация кэш-памяти. Типы кэш-памяти. Способы организации кэширования (сквозная и обратная запись). Организация внутренней кэш-памяти

- •3.13. Обмен информацией в режиме прямого доступа в память. Структура и функционирование контроллера прямого доступа в память. Каскадное включение контроллеров прямого доступа в память.

- •3.14. Функции чипсета. Структура микропроцессорной системы при использовании чипсета.

- •4.1. Организация конвейерной обработки информации в мп: структура классического конвейера, оценка производительности мп при конвейерной обработке

- •4.2. Конфликты в конвейере. Влияние конфликтов на производительность процессора. Типы конфликтов и способы минимизации их влияния на производительность мп

- •1. Структурные конфликты

- •4.3. Предсказание переходов: назначение, способы, техническая реализация

- •4.4. Неупорядоченное выполнение команд: суть подхода, проблемы, связанные с реализацией метода и пути их преодоления

- •4.5. Особенности архитектуры мп с технологией mmx и sse

- •4.6. Микропроцессор Pentium 4: особенности микроархитектуры, структура и назначение основных блоков, порядок функционирования

- •4.7. Пути повышения производительности микропроцессоров

- •4.8. Основные черты архитектуры epic

- •4.9. Микропроцессор Itanium: структура, архитектурные особенности

- •4.10. Отличительные черты микропроцессоров с risc-архитектурой

- •5.1. Основные конфигурации мультимикропроцессорных систем: smp-системы, numa-системы, кластеры, mpp-системы

- •5.2. Транспьютеры: структура, назначение, организация и порядок функционирования транспьютерных систем

- •6.1. Основные особенности мпс как объектов контроля

- •6.2. Особенности отладки мпс на различных этапах жизненного цикла

- •7.1. Назначение и особенности цифровой обработки сигналов

- •7.2. Основные особенности архитектуры процессоров цифровой обработки сигналов.

- •7.3. Особенности системы команд и программирования процессоров цифровой обработки сигналов.

- •8.1. Классические методы оценки производительности микропроцессоров: по тактовой частоте, mips, mflops. Достоинства, недостатки, область применимости

- •8.2. Оценка производительности микропроцессоров на основе бенчмарков. Тестовая программа Linpack. Тестовые пакеты specCpu, bdti

- •Допвопрос. Структура микропроцессорной системы

- •Для групп в7-12, к7-12в, к7-12с

- •2010-2011 Учебный год

- •I. Общие положения

- •Микропроцессор и его архитектура.

- •2. Однокристальные микроконтроллеры

- •3. Универсальные микропроцессоры

- •4. Структура и особенности функционирования современных микропроцессоров

4.5. Особенности архитектуры мп с технологией mmx и sse

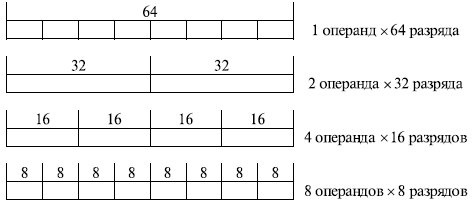

Главная особенность MMX — обработка по схеме SIMD (single instruction — multiple data). С помощью одной команды выполняется одна и та же операция сразу над несколькими операндами. Такой подход требует поддержки как со стороны системы команд и форматов данных, так и на аппаратном уровне.

В МП Pentium MMX появились 4 новых типа данных

(рис. 1). Для хранения этих данных в МП

были использованы 80-разрядные регистры

процессора обработки чисел с плавающей

точкой.

МП Pentium MMX появились 4 новых типа данных

(рис. 1). Для хранения этих данных в МП

были использованы 80-разрядные регистры

процессора обработки чисел с плавающей

точкой.

В систему команд МП Pentium MMX были включены 57 новых инструкций. Их использование было призвано, во-первых, уменьшить время выполнения мультимедийных приложений, а во-вторых, минимизировать конфликты в конвейере, который становился все более многоступенчатым.

Пример. Команда PADDSB «сложение со знаком с насыщением» выполняет сложение одновременно 8 пар однобайтовых операндов. Кроме того, если при выполнении сложения произошло переполнение, то результатом операции будет максимально возможное в этом формате число. Это избавляет программиста от необходимости использования после выполнения каждого сложения команд условных переходов, анализирующих признак переполнения результата, что хорошо сказывается на работе конвейера.

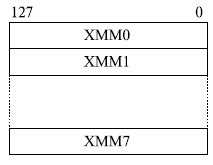

Т ехнология

MMX получила свое развитие в микропроцессоре

Pentium III с появлением специального блока

SSE (streaming SIMD Extension — потоковое SIMD-расширение)

обработки информации по схеме SIMD. Этот

блок содержит отдельный регистровый

файл из восьми 128-разрядных регистров

(рис. 2), что позволяет обрабатывать по

схеме SIMD числа с плавающей запятой

(четыре 32-разрядных числа): знак — 1

разряд; порядок (смещенный) — 8 разрядов;

мантисса — 23 разряда.

ехнология

MMX получила свое развитие в микропроцессоре

Pentium III с появлением специального блока

SSE (streaming SIMD Extension — потоковое SIMD-расширение)

обработки информации по схеме SIMD. Этот

блок содержит отдельный регистровый

файл из восьми 128-разрядных регистров

(рис. 2), что позволяет обрабатывать по

схеме SIMD числа с плавающей запятой

(четыре 32-разрядных числа): знак — 1

разряд; порядок (смещенный) — 8 разрядов;

мантисса — 23 разряда.

Расширено и количество форматов чисел с фиксированной точкой, обрабатываемых по схеме SIMD: 16 операндов × 8 разрядов; 8 операндов × 16 разрядов; 4 операнда × 32 разряда; 2 операнда × 64 разряда.

Для обработки чисел новых форматов в систему команд дополнительно введены 70 новых команд.

Блок SSE2, включенный в микропроцессор Pentium 4, реализует 144 новые команды. Из этих 144 инструкций 68 расширяют возможности старых SIMD-инструкций по работе с целыми числами, а 76 являются совершенно новыми. Среди последних — инструкции, позволяющие оперировать 128-разрядными числами (как целыми, так и вещественными с двойной точностью).

Новые возможности в этом направлении обработки информации были обеспечены в технологии SSE3, внедренной в ядре Prescott процессора Pentium 4 добавлением набора из 13 инструкций, и в технологии SSE4 в микропроцессорах семейства Intel Core 2 Duo.

4.6. Микропроцессор Pentium 4: особенности микроархитектуры, структура и назначение основных блоков, порядок функционирования

МП Pentium 4 является завершающей моделью 32-разрядных МП фирмы Intel с архитектурой IA-32. Основные особенности этого МП: 1) новая микроархитектура процессора NetBurst (пакетно-сетевая); 2) новая системная шина FSB.

Микроархитектура NetBurst отличается от своих предшественниц по целому ряду позиций:

Гарвардская структура с разделением потоков команд и данных.

Гиперконвейерная технология (Hyper-Pipelined Technology), число ступеней конвейера достигает 31 (в Pentium III — 11 ступеней).

Динамическое выполнение команд (dynamic execution), построенное на трех базовых концепциях: предсказание переходов (branch prediction), динамический анализ потока данных (dynamic data flow analysis) и спекулятивное выполнение (out-of-order execution). Аналогичный механизм используется в Pentium III, но в Pentium 4 он улучшен.

Выполнение арифметических и логических операций происходит с удвоенной тактовой частотой процессора, что позволяет за один такт получить результаты для двух команд.

Кэш-память 2-го уровня емкостью 256 Кбайт размещается непосредственно на кристалле процессора, что позволяет сократить время выборки по сравнению с ранними Pentuim III, где эта кэш-память располагается на отдельном кристалле.

Значительно расширены возможности обработки чисел по принципу SIMD в новом блоке SSE-2.

К оманды

и данные поступают в МП через блок

системного интерфейса.

оманды

и данные поступают в МП через блок

системного интерфейса.

Любой процессор архитектуры x86 обязательно оснащен процессорной шиной. Эта шина служит каналом связи между МП и всеми остальными устройствами в компьютере. Для ускорения обмена с памятью в Pentium 4 используется новая реализация системной шины: 4 канала передачи данных (по 100 МГц = 400 МГц). Шина включает 64-разрядную двунаправленную шину данных, дающую пропускную способность в 3,2 Гбайт/с, и 36-разрядную шину адреса.

Полученная по системной шине информация сохраняется в кэш 2-го уровня L2 (256 Кбайт), общий для команд и данных. Кэш данных 1-го уровня L1 имеет размер 8 Кбайт.

Вместо кэша команд 1-го уровня в Pentium 4 используется кэш для декодированных команд (микрокоманд): Execution Trace Cache — «кэш трассировки выполняемых микрокоманд». Там хранятся микрокоманды, которые были получены в результате декодирования входного потока инструкций исполняемого кода и готовы для передачи на выполнение конвейеру. Емкость — 12 Кбайт. Если в потоке команд оказывается команда условного перехода, то включается механизм предсказания ветвления. После формирования потоков микрокоманд производится выделение регистров, необходимых для выполнения декодированных команд. Эта процедура реализуется блоком распределения регистров. Он выделяет для каждого указанного в команде логического регистра один из 128 физических регистров, входящих в состав блоков регистров замещения (БРЗ).

Выбранные микрокоманды размещаются в очереди микрокоманд. Блок распределения микрокоманд выбирает микрокоманды из очереди не в порядке их поступления, а по мере готовности соответствующих операндов и исполнительных устройств. БФА — блок формирования адреса.

При формировании адресов обеспечивается обращение к заданному сегменту памяти. Каждый сегмент может делиться на страницы. Буфер ассоциативной трансляции страничного адреса TLB хранит базовые адреса наиболее часто используемых страниц.

Каждый ALU-модуль способен выполнить до двух целочисленных операций за один рабочий такт процессора.

Используется улучшенный блок предсказания ветвлений. Его основной частью является ассоциативная память, называемая буфером адресов ветвлений BTB, в которой хранятся 4092 адреса ранее выполненных переходов.

В Pentium 4 также интегрирован набор из 144 новых SIMD-инструкций, обеспечивающих одновременное выполнение одной операции над несколькими операндами.