- •Архитектура Фон-Неймана.

- •Init_timer0: anl tmod, #0f0h ;clear Timer 0

- •Init_special_interrupts: mov ie, #082h

- •Вопрос 21 платы развития

- •Вопрос 22мониторы отладки

- •Линейные,

- •Разветвляющиеся,

- •Циклические.

- •Igbt (Insulated Gate Bipolar Transistor) были запатентованы компанией International Rectifier в 1983 году и с тех пор постоянно совершенствуются.

- •Vd1,vd2,c1,c2 – двухполупериодный выпрямитель;

- •1) Метод прямого (параллельного) преобразования;

- •2) Метод последовательного приближения (поразрядного уравновешивания);

- •3) Метод интегрирования.

- •Ieee-1394 (FireWire или I.Link)

- •Ieee-1394 (FireWire или I.Link)

Вопрос №1.Кратая история ЭВМ.

Первая ЭВМ была построена в октябре 1945 года в школе инженеров-электриков Мура Пенсильванского университета (США) и получила название ENIAC (Electronic Numerical Integrator And Calculator — электронный числовой интегратор и вычислитель). ENIAC занимал площадь в 3000 квадратных футов и весил 30 тонн.

В создании следующей машины – ЭДВАК (электронный автоматический вычислитель с дискретными переменными) активное участие принял Джон фон Нейман. Он подсказал разработчикам как можно модифицировать ЭНИАК, чтобы упростить его программирование. Нейман разработал подробную логическую схему машины, в который структурными единицами были не физические элементы цепей, а идеализированные вычислительные элементы.

Фон Нейман предложил использовать в качестве элементов памяти не линии задержки, а электронно-лучевой трубки (электростатическая запоминающая система), что должно было сильно повысить быстродействие. При этом можно было обрабатывать все разряды машинного слова параллельно. Эта машина была названа ДЖОНИАК - в честь фон Неймана. На ней были сделаны предварительные расчеты для первой термоядерной бомбы «Майк», испытанной американцами 1 ноября 1952 г. в Тихом океане.

В нашей стране в начале 50-х годов под руководством Лебедева была разработана "МЭСМ. В 1952-1953 годах на ее основе была построена "БЭСМ-1" (Большая электронная счетная машина). А на ее основе был произведен серийный выпуск машины "БЭСМ-2".

Ламповая ЭВМ “Урал”, собранная в г. Пенза, одна из тех машин, которые решали задачу расчета траекторий полета ракет на космодроме Байконур.

В нашей стране в начале 50-х годов под руководством Лебедева была разработана "МЭСМ. В 1952-1953 годах на ее основе была построена "БЭСМ-1" (Большая электронная счетная машина). А на ее основе был произведен серийный выпуск машины "БЭСМ-2".

Ламповая ЭВМ “Урал”, собранная в г. Пенза, одна из тех машин, которые решали задачу расчета траекторий полета ракет на космодроме Байконур.

Многим учёным не давали покоя огромные размеры первых ЭВМ и большая потребляемая мощность. Кроме того эти машины принадлежали правительству и доступ к ним был ограничен. Поэтому некоторые заинтересованные фирмы стали проводить работы направленные на решение этих проблем.

С изобретением полупроводников почти сразу возникли идеи по сокращению соединительных проводов между ними. Первые опыты проводились в фирме Shockley Semiconductor Laboratory, затем в Fairchild Semiconductor Робертом Нойсом и Гордоном Муром.

В 1959 году Нойс сделал первое детальное сообщение об интегральных диффузионных или напылённых резисторах, по поводу изоляции приборов друг от друга с помощью смещённых в обратном направлении p-n-переходов и по поводу соединения друг с другом элементов через отверстия в окисле путем напыления металла на поверхность. С этого момента стало возможным создание первых интегральных схем.

На вершине успеха Fairchild Semiconductor Нойс и Мур уходят из фирмы, чтобы создать свою – Intel (integrated electronics – интегрированная электроника). Вначале Intel пришлось заниматься памятью, чтобы не быть раздавленной конкурентами: Fairchild Semiconductor и Texas Instruments.

За два года Нойс и Мур создали чип памяти 1103 размером с две стандартные печатные буквы. Каждый чип состоял из 4-х тысяч транзисторов, заменяя при этом работу тысячи керамических сердечников - и делая это много быстрее.

В 1969 году в Intel появились несколько человек из Busicom - молодой японской компании, занимающейся производством калькуляторов. Им требовалось около десяти интегральных схем в качестве основного элемента нового дешевого настольного калькулятора. Дизайн был разработан Масатоши Шима, который и представлял японскую сторону. Глядя на калькулятор Тедду Хоффу пришла идея сделать его с некоторыми возможностями программирования - как бы универсальным компьютером.

Развивая идею, в течение осени 1969 года Тедд Хофф, которому ассистировал Стэн Мейзор, определился с архитектурой будущего микропроцессора: 4-разрядное ЦПУ, ROM для сохранения программного обеспечения, RAM для сохранения данных и несколько портов для взаимодействия с внешними устройствами - клавиатура, принтер и т.п.

Первым был спроектирован и выпущен в ноябре 1970-го года чип 4001. Их тогда называли run (управлять, выполнять), и схема работала потрясающе.

За два года Нойс и Мур создали чип памяти 1103 размером с две стандартные печатные буквы. Каждый чип состоял из 4-х тысяч транзисторов, заменяя при этом работу тысячи керамических сердечников - и делая это много быстрее.

В 1969 году в Intel появились несколько человек из Busicom - молодой японской компании, занимающейся производством калькуляторов. Им требовалось около десяти интегральных схем в качестве основного элемента нового дешевого настольного калькулятора. Дизайн был разработан Масатоши Шима, который и представлял японскую сторону. Глядя на калькулятор Тедду Хоффу пришла идея сделать его с некоторыми возможностями программирования - как бы универсальным компьютером.

Развивая идею, в течение осени 1969 года Тедд Хофф, которому ассистировал Стэн Мейзор, определился с архитектурой будущего микропроцессора: 4-разрядное ЦПУ, ROM для сохранения программного обеспечения, RAM для сохранения данных и несколько портов для взаимодействия с внешними устройствами - клавиатура, принтер и т.п.

Первым был спроектирован и выпущен в ноябре 1970-го года чип 4001. Их тогда называли run (управлять, выполнять), и схема работала потрясающе.

В конце концов, именно из этого процессора после некоторых модификаций и началась эпоха семейства MCS-8, (Micro Computer System 8-bit), все эти знаменитые 8008, 8080 и так далее, которые появились в 1972 году.

К концу 70-х годов и отечественный рынок стали завоёвывать 8-разрядные процессоры второго поколения 8080 и 8085 от Intel, 6800 от фирмы Motorola и Z80 от Zilog.

Всем специалистам стало очевидно, что за микропроцессорами — будущее, и если не вкладывать деньги в эти технологии, то просто выпадешь из числа развитых стран. Прекрасно понимали это и консультанты правительства тогда еще существовавшего СССР. Но они также понимали, что, поскольку в этих работах мы шли с некоторым отставанием от американцев, разумно было бы просто скопировать уже разработанные за океаном процессоры, в которых решены многие из тех проблем, на самостоятельное решение которых ушли бы месяцы и годы, не говоря уже о больших деньгах. Другими словами, с целью экономии времени и средств было решено попросту «передрать» эти процессоры, самым что ни на есть пиратским способом.

Неясно было только, какой из процессоров нужно копировать — Intel‘овский, Motorol'овский или Zilog'овский. Каждый из них был по-своему хорош, да и исход конкурентной борьбы между ними предсказать было невозможно. В конце концов было принято соломоново решение — копировать все, а там видно будет.

Копировать Intel'овскую продукции было поручено отечественным предприятиям,

Motorol'овскую — болгарским,

а Zilog'овскую — немецким.

Вот так Intel, ни вложив ни доллара, завоевала советский рынок — ее продукты под нашими названиями (580ИК80, 1821ВМ85, 1810ВМ86, 1816ВЕ48, 1816ВЕ51 и т. д.) стали родными для российских, украинских, белорусских, прибалтийских и закавказских инженеров. Motorol'е же в результате этой разборки досталась маленькая Болгария, а не выдержавшему гонки на столь высоком уровне Zilog'у — и вовсе умершая ГДР.

До середины 90-х годов отечественные разработчики были практически незнакомы с какими-либо контроллерами, помимо Intel-совместимых.

Неясно было только, какой из процессоров нужно копировать — Intel‘овский, Motorol'овский или Zilog'овский. Каждый из них был по-своему хорош, да и исход конкурентной борьбы между ними предсказать было невозможно. В конце концов было принято соломоново решение — копировать все, а там видно будет.

Копировать Intel'овскую продукции было поручено отечественным предприятиям,

Motorol'овскую — болгарским,

а Zilog'овскую — немецким.

Вот так Intel, ни вложив ни доллара, завоевала советский рынок — ее продукты под нашими названиями (580ИК80, 1821ВМ85, 1810ВМ86, 1816ВЕ48, 1816ВЕ51 и т. д.) стали родными для российских, украинских, белорусских, прибалтийских и закавказских инженеров. Motorol'е же в результате этой разборки досталась маленькая Болгария, а не выдержавшему гонки на столь высоком уровне Zilog'у — и вовсе умершая ГДР.

До середины 90-х годов отечественные разработчики были практически незнакомы с какими-либо контроллерами, помимо Intel-совместимых.

Поэтому привлекательность в сравнении с х51 PIC-контроллеров или казавшихся еще пару лет назад необычайно перспективными контроллеров семейства Z8 резко уменьшилась. Вдобавок на рынке появились RISC-контроллеры семейства AVR все той же Atmel, превзошедшие по производительности изделия Microchip и унаследовавшие от х51 периферию. Эти особенности, а также доступность многих из средств поддержки разработки для них и их низкая цена способствовали оттоку симпатий многих разработчиков от недавних претендентов на звание контроллера номер 1. В итоге рынок сильно расслоился, и у каждого из контроллеров осталось достаточное количество его почитателей.

Вместе с тем активно развивающийся класс восьмиразрядных микроконтроллеров и микросхем поддержки может использоваться не только для создания простейших устройств управления: регуляторов, контроллеров различной техники, интеллектуальных периферийных модулей, но и для создания достаточно сложных локальных и распределенных комплексов, включая железнодорожную автоматику и телемеханику, таких как автоматизированная система управления и контроля движением поездов, системы учета энергоресурсов, телеизмерения, контроля доступа, сигнализации и других. Примерами подобных микроконтроллеров могут служить семейства PICmicro (Microchip Inc.), Z8 (Zilog Inc.), COP8 (National Semiconductor Со.), AT89, ATmega (Atmel).

Вопрос №2. Поколения ЭВМ.

Поэтому привлекательность в сравнении с х51 PIC-контроллеров или казавшихся еще пару лет назад необычайно перспективными контроллеров семейства Z8 резко уменьшилась. Вдобавок на рынке появились RISC-контроллеры семейства AVR все той же Atmel, превзошедшие по производительности изделия Microchip и унаследовавшие от х51 периферию. Эти особенности, а также доступность многих из средств поддержки разработки для них и их низкая цена способствовали оттоку симпатий многих разработчиков от недавних претендентов на звание контроллера номер 1. В итоге рынок сильно расслоился, и у каждого из контроллеров осталось достаточное количество его почитателей.

Вместе с тем активно развивающийся класс восьмиразрядных микроконтроллеров и микросхем поддержки может использоваться не только для создания простейших устройств управления: регуляторов, контроллеров различной техники, интеллектуальных периферийных модулей, но и для создания достаточно сложных локальных и распределенных комплексов, включая железнодорожную автоматику и телемеханику, таких как автоматизированная система управления и контроля движением поездов, системы учета энергоресурсов, телеизмерения, контроля доступа, сигнализации и других. Примерами подобных микроконтроллеров могут служить семейства PICmicro (Microchip Inc.), Z8 (Zilog Inc.), COP8 (National Semiconductor Со.), AT89, ATmega (Atmel).

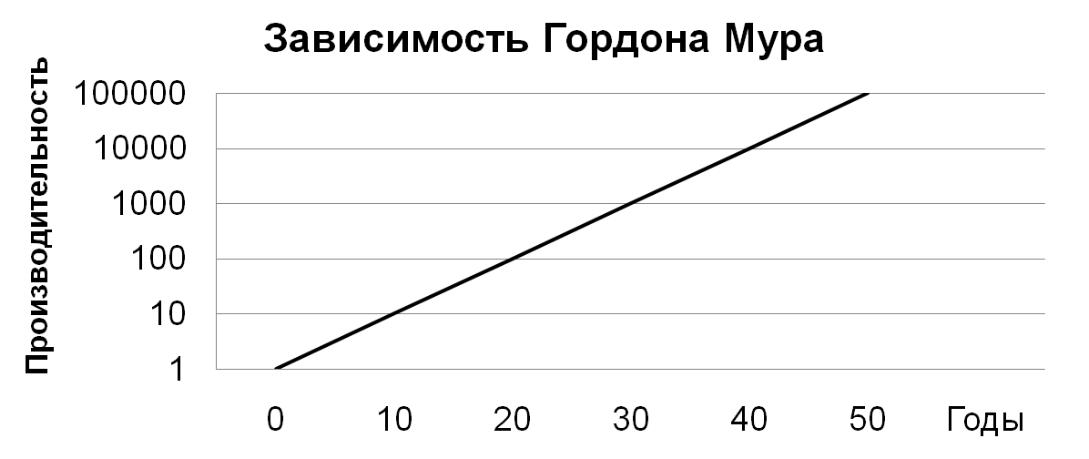

(Число транзисторов на кристалле удваивается каждые два года, 1965 г.)

Первое поколение

Первым поколением ЭВМ стали ламповые ЭВМ, промышленный выпуск которых был начат в начале 50-х годов.

В ЭВМ первого поколения использовались электронные лампы. Так, фирма IBM в 1952 году выпустила первый промышленный компьютер IBM-701, содержащий 4000 электронных ламп и 12000 германиевых диодов. Один компьютер этого типа занимал площадь порядка 30 кв. метров, потреблял много электроэнергии, имел низкую надежность. Поиск неисправности составлял 3-5 дней.

Повышение быстродействия ЭВМ шло за счет увеличения ее памяти и улучшения архитектуры.

Второе поколение

В 1948 году физики-теоретики Джон Бардин и Уильям Шокли совместно с ведущим экспериментатором фирмы "Белл телефон лабораториз" Уолтером Браттейном создали первый действующий транзистор. Это был точечно-контактный прибор, в котором три металлических "усика" контактировали с бруском из поликристаллического германия.

Первые компьютеры на основе транзисторов появились в конце 50-х годов, а к середине 60-х годов были созданы более компактные внешние устройства.

При советско-американском космическом полете "Союз-Аполлон" управление осуществлялось на новом комплексе БЭСМ-6 телеметрическая информация обрабатывалась за одну минуту, вся информация обрабатывалась почти на полчаса раньше, чем у коллег в США.

Третье поколение

За счет создания технологии производства интегральных микросхем (ИС) удалось добиться увеличения быстродействия и надежности полупроводниковых схем, а также уменьшения их габаритов, потребляемой мощности и стоимости. Интегральные микросхемы состоят из десятков электронных элементов, образованных в прямоугольной пластине кремния с длиной стороны не более 1 см. Такая пластина (кристалл) размещается в небольшом пластмассовом корпусе, размеры которого, как правило, определяются только числом “ножек” (выводов от входов и выходов электронной схемы, созданной на кристалле).

Четвертое поколение

Успехи в развитии электроники привели к созданию больших интегральных схем (БИС), где в одном кристалле размещалось несколько десятков тысяч электрических элементов. Это позволило разработать более дешевые ЭВМ, имеющие большую память и меньший цикл выполнения команды: стоимость байта памяти и одной машинной операции начала резко снижаться. Но так как затраты на программирование почти не сокращались, то на первый план вышла задача экономии человеческих, а не машинных ресурсов.

В начале 1977 года была зарегистрирована Apple Comp., и началось производство первого в мире персонального компьютера Apple.

Характерные свойства ЭВМ четвертого поколения:

Мультипроцессорность.

Параллельно-последовательная обработка.

Языки высокого уровня.

Появляются первые сети ЭВМ.

В настоящее время фирма Apple выпускает персональные компьютеры Macintosh, которые по большинству параметров превосходят компьютеры IBM PC.

У нас в основном используются ПК типа IBM PC. Это можно объяснить следующими причинами:

до начала 90-х годов США запрещали поставки в СССР передовых информационных технологий, к которым были отнесены и мощные компьютеры “Макинтош”;

“Макинтоши” были существенно дороже IBM PC (в настоящее время цены на них сблизились);

для IBM PC разработано значительно большее количество прикладных программ, что облегчает их использование в самых разных областях.

Пятое поколение

В конце 80-х годов появляются первые ЭВМ пятого поколения. Пятое поколение ЭВМ связывают с переходом к микропроцессорам. С точки зрения структурного построения характерна максимальная децентрализация управления. С точки зрения программного и математического обеспечения - переход на работу в программных средах и оболочках.

Производительность 108 – 109 операций в секунду. Для пятого поколения характерны многопроцессорные структуры созданные на упрощенных микропроцессорах, которых очень много (решающие поля или среды). Создаются ЭВМ ориентированные на языки высокого уровня.

В этот период существуют две диаметрально противоположных тенденции: персонификация ресурсов и коллективизация ресурсов (коллективный доступ - сети).

Благодаря операционной системе, обеспечивающей простоту общения с этой ЭВМ, большой библиотеке прикладных программ по различным отраслям человеческой деятельности, а также малой стоимости ЭВМ становится необходимой принадлежностью инженера, исследователя, экономиста, врача, агронома, преподавателя, редактора, секретаря и даже ребенка.

Шестое поколение

О шестом поколении можно пока только мечтать...

Нейрокомпьютер

Компьютер, созданный на основе нейронных сетей пока не существует самостоятельно, но активно моделируется на современных компьютерах.

Один из разработчиков нейрокомпьютеров А. Н. Горбань считает: "Пять поколений ЭВМ следуют друг за другом. Нарождающееся шестое настолько отличается от предыдущих, что лучше говорить не о поколениях и даже не о новых видах, родах или семействах, а о новом царстве - масштаб дистанции между нейрокомпьютерами и обычными ЭВМ соответствует различиям между царствами живых организмов. Чем отличаются машины второго царства?

Большое число параллельно работающих простых элементов - нейронов (от нескольких десятков до 106-108), что обеспечивает колоссальный скачок в быстродействии.

Место программирования занимает обучение (воспитание) - машина учится решать задачи, изменяя параметры нейронов и связей между ними".

Вопрос №3. Проблема внедрения ЭВМ на сети ж.д.

Разработки современных микропроцессорных управляющих систем направлены на наращивание мощности вычислителей, переход к 16, 32, и 64 разрядным контроллерам и промышленным персональным компьютерам (ПК), в использовании операционных систем (ОС), построении многоуровневой иерархии интерфейсов. Подобный подход, при всех его положительных сторонах: модульности, снижении трудоемкости разработки, стандартизации протоколов и т.д., не всегда применим на железной дороге в российских условиях. Выделим основные причины, усложняющие внедрение новых микропроцессорных устройств:

- значительная степень избыточности, приводящая к снижению надёжности и недопустимо высокой цене;

- необходимость резервирования оборудования, при этом должны быть разные схемные и программные решения одной логической функции, мажоритарное принятие решения;

- большая протяженность ж.д. и соответственно инерционность внедрения;

- быстро изменяющая номенклатура изделий затрудняет обслуживание и ремонт;

- суровые климатические условия повышают требования к качеству изготовления, приёмки в эксплуатацию и к самой эксплуатации;

- сложность в подготовке специалистов без соответствующей материальной базы.

Не всегда самое новое является самым лучшим для ж. д. транспорта.

Вопрос №4. Микропроцессор ,микро-ЗВМ, микропроцессорная система.

Разработки современных микропроцессорных управляющих систем направлены на наращивание мощности вычислителей, переход к 16, 32, и 64 разрядным контроллерам и промышленным персональным компьютерам (ПК), в использовании операционных систем (ОС), построении многоуровневой иерархии интерфейсов. Подобный подход, при всех его положительных сторонах: модульности, снижении трудоемкости разработки, стандартизации протоколов и т.д., не всегда применим на железной дороге в российских условиях. Выделим основные причины, усложняющие внедрение новых микропроцессорных устройств:

- значительная степень избыточности, приводящая к снижению надёжности и недопустимо высокой цене;

- необходимость резервирования оборудования, при этом должны быть разные схемные и программные решения одной логической функции, мажоритарное принятие решения;

- большая протяженность ж.д. и соответственно инерционность внедрения;

- быстро изменяющая номенклатура изделий затрудняет обслуживание и ремонт;

- суровые климатические условия повышают требования к качеству изготовления, приёмки в эксплуатацию и к самой эксплуатации;

- сложность в подготовке специалистов без соответствующей материальной базы.

Не всегда самое новое является самым лучшим для ж. д. транспорта.

МИКРОЭВМ (микропроцессорная ЭВМ) - электронная вычислительная машина основу, которой составляет микропроцессор, дополненный запоминающим устройством, устройствами ввода-вывода данных и набором средств связи. Отличается малыми габаритными размерами, удобством эксплуатации, низкой стоимостью. МикроЭВМ является универсальным, программно - управляемым устройством, т. е. настраивается на выполнение тех или иных функций с помощью хранимой в ее памяти программы.

В технологическом процессе на производстве отдельно микроЭВМ редко используются, при помощи средств связи они объединяются в единую сеть, образуя микропроцессорную систему.

МИКРОПРОЦЕССОРНАЯ СИСТЕМА – множество микропроцессорных элементов, находящихся в отношениях и связях друг с другом, образующих определенную целостность, единство, имеющих единый системный подход в системотехнике, анализе и т. д..

Организация микропроцессорных информационно-управляющих систем определяется видом периферийного оборудования, возможностями подключения дополнительных ВУ и способом связи основных элементов системы между собой.

Вопрос №5.Классификация микро-ЭВМ по конструктивному исполнению.

Классификация микроЭВМ

Все микроЭВМ по конструктивному исполнению можно разделить на три основных класса:

встраиваемые;

автономные;

персональные ЭВМ.

Характерным признаком встраиваемых микроЭВМ является отсутствие, как правило, в ее составе средств связи с пользователем. МикроЭВМ связана только с датчиками, вырабатывающими входные сигналы, и с объектами управления. Программы работы встраиваемых микроЭВМ размещаются в ПЗУ. Конструктивно встраиваемые микроЭВМ выполняют в виде отдельных БИС либо на основе МПК БИС различных серий в виде отдельной платы или набора плат с разъемами для подключения к электронным схемам изделия, в которое они встраиваются. В практике разработки и применения встраиваемых микроЭВМ, сложившейся к настоящему времени, можно выделить три основных направления.

а) Одноплатные микроЭВМ без средств связи со стандартными внешними устройствами, ориентированные на самостоятельное использование. Такого типа микроЭВМ принято называть микроконтроллерами.

Микроконтроллеры (МК) являются функционально закон-ченными устройствами, имеют программно-управляемые каналы связи с объектами управления, объемы ПЗУ (ППЗУ), достаточные для хранения программ работы МК и исключающие необходимость ввода программ с внешних носителей.

б) Одноплатные микроЭВМ, предназначенные как для самостоятельного использования, так и в составе автономных многоплатных микроЭВМ.

в) Однокристальные микроЭВМ.

Представляют собой набор функций, присущих микроЭВМ, выполненный в виде одной БИС

Автономные микроЭВМ выполняют на основе МПК БИС в виде конструктивно законченного изделия с собственным блоком питания. Такие микроЭВМ оснащают различными внешними устройствами: дисплеями, устройствами печати, накопителями на гибких магнитных дисках и магнитной ленте, устройствами сопряжения с каналами связи и т. д. Автономные микроЭВМ имеют, как правило, развитое программное обеспечение. Зачастую автономные микроЭВМ используют для разработки программного обеспечения встраиваемых микроЭВМ, программно с ними совместимых.

Персональные ЭВМ — это, по сути дела, автономные микроЭВМ, своей конструкцией, набором внешних устройств и составом программного обеспечения ориентированные на работу отдельного пользователя.

Вопрос№6

По доступу к структуре микроЭВМ выпускают модели двух видов: закрытая и открытая.

Закрытая модель ориентирована на самостоятельное использование и рассчитана на связь с объектом управления только по программируемым цифровым каналам ввода-вывода.

В

открытой модели МК предусмотрены

средства для расширения ее функциональных

возможностей за счет подключения

функциональных дополнительных модулей

через межмодульный параллельный

интерфейс (МПИ) и объединения нескольких

МК в малую локальную сеть по

последовательному системному каналу.

открытой модели МК предусмотрены

средства для расширения ее функциональных

возможностей за счет подключения

функциональных дополнительных модулей

через межмодульный параллельный

интерфейс (МПИ) и объединения нескольких

МК в малую локальную сеть по

последовательному системному каналу.

Вопрос №7.

П о

внутренней

структуре

существует два основных принципа

построения микропроцессоров:

о

внутренней

структуре

существует два основных принципа

построения микропроцессоров:

Гарвардская архитектура;

архитектура Фон Неймана.

Гарвардская архитектура организации памяти

В Гарвардской архитектуре принципиально различаются два вида памяти:

память программ;

память данных.

В Гарвардской архитектуре принципиально

невозможно производить операцию записи

в память программ, что исключает

возможность случайного разрушения

управляющей программы в случае

неправильных действий над данными или

неправильным выключением питания. Кроме

того, в ряде случаев для памяти программ

и памяти данных выделяются отдельные

шины обмена данными. Эти особенности

определили области применения этой

архитектуры построения микропроцессоров.

Гарвардская архитектура применяется

в микроконтроллерах, где требуется

обеспечить высокую надёжность работы

аппаратуры и в сигнальных процессорах,

где эта архитектура кроме обеспечения

высокой надёжности работы устройств

позволяет обеспечить высокую скорость

выполнения программы, за счёт одновременного

считывания управляющих команд и

обрабатываемых данных, а так же запись

полученных результатов в память данных.

Гарвардской архитектуре принципиально

невозможно производить операцию записи

в память программ, что исключает

возможность случайного разрушения

управляющей программы в случае

неправильных действий над данными или

неправильным выключением питания. Кроме

того, в ряде случаев для памяти программ

и памяти данных выделяются отдельные

шины обмена данными. Эти особенности

определили области применения этой

архитектуры построения микропроцессоров.

Гарвардская архитектура применяется

в микроконтроллерах, где требуется

обеспечить высокую надёжность работы

аппаратуры и в сигнальных процессорах,

где эта архитектура кроме обеспечения

высокой надёжности работы устройств

позволяет обеспечить высокую скорость

выполнения программы, за счёт одновременного

считывания управляющих команд и

обрабатываемых данных, а так же запись

полученных результатов в память данных.

Архитектура Фон-Неймана.

Фон - Неймановская архитектура организации памяти

Любой участок памяти может служить как памятью программ, так и памятью данных. Причём в разные моменты времени одна и та же область памяти может использоваться и как память программ и как память данных. Эта особенность архитектуры позволяет наиболее гибко управлять работой микропроцессорной системы, но создаёт принципиальную возможность искажения управляющей программы, что понижает надёжность работы аппаратуры. Эта архитектура используется в универсальных компьютерах и в некоторых видах микроконтроллеров.

Реализовать системы контроля, измерения и управления любым технологическим процессом, в том числе и информационно-управляющие системы, ориентированные на решение задач регулирования движения поездов, передачи данных, измерения параметров устройств автоматики и телемеханики, можно двумя способами:

жёстким (аппаратурным);

гибким (перепрограммируемым).

Первый способ заключается в построении электронных схем, способных однозначно решать поставленные задачи.

Второй способ используется в случае, если перечень рабочих функций значителен и возникает необходимость переориентации системы на решение тех или иных задач.

Вопрос №8.

По системе команд микропроцессоры отличаются огромным разнообразием, зависящим от фирмы производителя. Тем не менее, можно определить два варианта построения микропроцессоров:

архитектура SISC - со стандартным набором команд;

архитектура RISC - с ограниченным набором команд;

По оперированию АЛУ с данными существуют микропроцессоры трех видов:

аккумуляторные;

с регистрами общего назначения;

комбинированные.

В аккумуляторных процессорах математические операции могут производиться только над одной особой ячейкой памяти - аккумулятором. Для того, чтобы произвести операцию над произвольной ячейкой памяти её содержимое необходимо скопировать в аккумулятор, произвести требуемую операцию, а затем скопировать полученный результат в произвольную ячейку памяти.

В микропроцессорах с регистрами общего назначения математические операции могут выполняться над любой ячейкой памяти. В зависимости от типа операции команда может быть одноадресной, двухадресной или трёхадресной.

В настоящее время в чистом виде не существует ни та ни другая система команд. Все выпускаемые в настоящее время процессоры обладают системой команд с признаками, как аккумуляторных процессоров, так и микропроцессоров с регистрами общего назначения.

Вопрос №9.

В зависимости от разрядности оперирования с данными микропроцессоры изготавливаются:

4-разрядные - являются очень простыми и дешевыми устройствами, предназначенными для замены несложных схем на "жесткой" логике в системах с невысоким быстродействием. Типичные случаи применения - часы, калькуляторы, игрушки, простые устройства управления в промышленных устройствах и бытовой технике.

8-разрядные - наиболее многочисленная группа (оптимальное сочетание цены и возможностей), к этой группе относятся однокристальные микроЭВМ серии MCS-51 (Intel) и совместимые с ними, PIC (MicroChip), HC68 (Motorola), Z8 (Zilog) и др.

16-разрядные - MCS-96 (intel), MSP430 (Texas Instruments) и др. - более высокопроизводительные но более дорогостоящие.

32-разрядные - обычно являющиеся модификациями универсальных микропроцессоров, например i80186 или i386EX.

64-разрядные - SiS755 (Silicon Integrated Systems Corp.), Athlon64 (AMD) используются для оперирования с большими потоками данных.

Вопрос №10

По широте охвата сетей МПИУС:

локальные т.е. в ограниченном пространстве (одно здание);

кампусные - до нескольких километров (соседние здания);

городские - десятки километров (в пределах города);

широкомасштабные – сотни и тысячи километров (между городами);

глобальные – без ограничений расстояний (Интернет).

По доступу к информации:

интранет (intranet) - обозначает внутреннюю сеть организации, где важны два момента:

1) изоляция или защита внутренней сети от внешней (Интернет);

2) использование сетевого протокола IP и Web-технологий (прикладного протокола HTTP). В аппаратном аспекте применение технологии интранет означает, что все абоненты сети в основном обмениваются данными с одним или несколькими серверами, на которых сосредоточены основные информационные ресурсы предприятия;

и

нтернет

– с открытым доступом.

нтернет

– с открытым доступом.

Структура МПИУС

без открытого доступа (интранет)

Основой любой МПИУС является микроЭВМ, поэтому в первую очередь следует уделить особое внимание выбору этого элемента структуры, его подключению к объектам управления и контроля, а также основам программирования.

Структура МПИУС, с открытым доступом

По протоколу обмена:

Ethernet,

Token Ring,

100VG-AnyLAN,

ARCnet,

FDDI

другие

Оборудование подразделяется на:

активное — интерфейсные карты компьютеров, повторители, концентраторы и т. п. которым необходима подача энергии;

пассивное — кабели, соединительные разъемы, коммутационные панели и т. п.которым подачи энергии не требует.

По топологии и методов доступа к среде:

физическая топология - определяет правила физических соединений узлов (прокладку реальных кабелей);

логическая топологию, определяет направления потоков данных между узлами сети.

Логическая и физическая топологии относительно независимы друг от друга.

Виды физической топологии: а — шина, б — звезда, в — кольцо,

г — дерево, д — сетка

В логической шине информация (кадр), передаваемая одним узлом, одновременно доступна для всех узлов, подключенных к одному сегменту. Передачу считанных данных на вышестоящий уровень (LLC-подуровень) производит только тот узел (узлы), которому адресуется данный кадр.

Логическая шина реализуется на физической топологии шины, звезды, дерева, сетки. Метод доступа к среде передачи, разделяемой между всеми узлами сегмента, — вероятностный, основанный на прослушивании сигнала в шине (Ethernet), или детерминированный, основанный на определенной дисциплине передачи права доступа (ARCnet).

В логическом кольце информация передается последовательно от узла к узлу. Каждый узел принимает кадры только от предыдущего и посылает только последующему узлу по кольцу. Узел транслирует дальше по сети все кадры, а обрабатывает только адресуемые ему. Реализуется на физической топологии кольца или звезды с внутренним кольцом в концентраторе. Метод доступа — детерминированный. На логическом кольце строятся сети Token Ring и FDDI.

Современный подход к построению высокопроизводительных сетей переносит большую часть функций МАС - уровня (управление доступом к среде) на центральные сетевые устройства — коммутаторы. При этом можно говорить о логической звезде, хотя это название широко не используется.

Методы доступа к среде передачи делятся на вероятностные и детерминированные.

Вопрос№ 11.

В развитии схемотехники можно выделить три ветви:

аналоговая;

цифровая;

цифроаналоговая.

Каждая ветвь заняла своё место и применение той или иной схемы в первую очередь определяется поставленной задачей. Для микропроцессорных информационно-управляющих систем на нижнем уровне – измерения, управления и контроля наиболее подходит интегральная схемотехника.

Какой именно выбрать интегральный элемент системы определяется рядом факторов, в том числе и опытом конструктора систем и наличием дополнительных средств программирования и отладки.

Понятно что программируемые интегральные схемы имеют ряд преимуществ и сейчас нет сомнений – взять микропроцессор или разработать схему на дискретных компонентах. Скорее возникает вопрос - какой фирмы и с какой внутренней структурой выбрать микропроцессор или однокристальную микроЭВМ? Для этого нужно представлять как они устроены и чем грозит неправильно выбранное решение.

В опрос№12.

опрос№12.

Обобщённая схема микроконтроллера для информационно-управляющей системы на основе БИС серии MCS-51 может содержать следующие функциональные узлы:

микропроцессор (МП);

внешний или внутренний генератор стабильной частоты (ЗГ);

оперативное запоминающее устройство (ОЗУ);

постоянное запоминающее устройство или перепрограммируемое (ПЗУ или ППЗУ);

последовательная память (FLASH);

мультиплексор адрес – данные (MUX);

дешифратор адресов (DC);

параллельный порт ввода – вывода (ПВВ);

последовательный порт RS-232 (RS-232);

последовательный порт RS-485 (RS-485);

последовательную универсальную шину (USB);

преобразователь CAN (ETHERNET);

преобразователь код – напряжение (ЦАП);

преобразователь напряжение – код (АЦП);

гальваническую развязку между микроЭВМ и объектами управления и контроля (ISO);

масштабируемые усилители аналоговых сигналов (УАС);

усилители дискретных сигналов (УДС);

жидкокристаллический индикатор (ЖКИ);

матричную клавиатуру (МКЛ);

часы реального времени с независимым источником питания (TIME);

блок питания (БП);

другие (зависят от потребности).

Важными компонентами микроЭВМ являются соединительные элементы (разъёмы, зажимы, шлейфы и т. д.) и корпус соответствующего класса. Кроме этого должна быть подготовлена документация на разработанное устройство.

В зависимости от поставленной задачи отдельные элементы архитектуры микроЭВМ могут отсутствовать.

Вопрос №13.

Существует множество микроЭВМ с различными характеристиками и со временем их параметры фирмы-разработчики улучшают, но все они имеют общие принципы построения. Для первого знакомства лучше взять наиболее популярную однокристальную микроЭВМ серии MCS-51 (в лабораторном стенде используется АТ89С52).

МикроЭВМ семейства 8051 имеют следующие аппаратные особенности:

внутреннее ОЗУ объемом 128 байт;

четыре двунаправленных побитно настраиваемых восьмиразрядных порта ввода-вывода;

два 16-разрядных таймера-счетчика;

встроенный тактовый генератор;

адресация 64 Кбайт памяти программ и 64 Кбайт памяти данных;

две линии запросов на прерывание от внешних устройств;

интерфейс для последовательного обмена информацией с другими микроконтроллерами или персональными компьютерами.

МикроЭВМ 8751 снабжен УФ ПЗУ объемом 4 Кбайт, AT89C52 имеет электрически перепрограммируемое ПЗУ 8 Кбайт, а AT89S52 ещё и последовательный интерфейс программирования.

Вопрос №14

Vss — потенциал общего провода ("земли");

Vcc — основное напряжение питания +5 В;

XTAL1, XTAL2 — выводы для подключения кварцевого резонатора;

RESET — вход общего сброса микроконтроллера;

PSEN — разрешение внешней памяти программ, выдается только при обращении к внешнему ПЗУ;

ALE — строб адреса внешней памяти;

ЕА — отключение внутренней программной память; уровень 0 на этом входе заставляет микроконтроллер выполнять программу только внешнее ПЗУ; игнорируя внутреннее (если последнее имеется);

P0 — восьми битный двунаправленный порт ввода-вывода информации: при работе с внешними ОЗУ и ПЗУ по линиям порта в режиме временного мультиплексирования выдается адрес внешней памяти, после чего осуществляется передача или прием данных;

P1 — восьми битный квази двунаправленный порт ввода/вывода: каждый разряд порта может быть запрограммирован как на ввод, так и на вывод информации, независимо от состояния других разрядов, также этот порт используется при программировании внутренней памяти программ;

P2 — восьми битный квази двунаправленный порт, аналогичный Р1; кроме того, выводы этого порта используются для выдачи адресной информации при обращении к внешней памяти программ или данных (если используется 16-битовая адресация последней). Выводы порта используются при программировании 8751 для ввода в микроконтроллер старших разрядов адреса;

РЗ — восьми битный квази двунаправленный порт, аналогичный Р1; кроме того, выводы этого порта могут выполнять ряд альтернативных функций, которые используются при работе таймеров, порта последовательного ввода-вывода, контроллера прерываний, и внешней памяти программ и данных.

RxD – последовательные данные приёмника;

TxD – последовательные данные передатчика;

INT0 – вход внешнего прерывания 0;

INT1 – вход внешнего прерывания 1;

T0 – вход таймера/счётчика 0;

T1 – вход таймера/счётчика 1;

WR – выход стробирующего сигнала при записи во внешнюю память;

RD – выход стробирующего сигнала при чтении из внешней памяти.

Вопрос №15.

Р1 — РЗ триггеры на полевых транзисторах с внутренней нагрузкой.

P0 — на транзисторах с открытым стоком.

Каждая линия любого из портов может независимо использоваться как для ввода, так и для вывода информации (для линий портов P0 и Р2 это справедливо тогда, когда они не используются для обращения к внешней памяти).

При переводе любой линии портов Р1 — РЗ в режим ввода информации выходной полевой транзистор отключается.

Внутренний нагрузочный резистор как бы «подтягивает» потенциал вывода к напряжению питания, в то время как внешняя нагрузка может сделать его нулевым. Внутренняя нагрузка становятся источниками тока для микросхемы или транзистора, нагруженных на данный вывод.

Выходные каскады порта P0 имеют иную структуру. Нагрузочный полевой транзистор линии порта включен только тогда, когда порт выводит 1 при обращении к внешней памяти. В остальных случаях нагрузочный транзистор отключен, что позволяет использовать линии порта P0 как выводы с высокоимпедансным состоянием.

Режимы энергототребления:

Нормальный – все элементы внутренней структуры работают;

Холостого хода – блокируется CPU, регистры в режиме хранения информации, выход из этого режима через прерывание или RESET;

Микропотребление – остановка генератора, выход из этого режима только RESET.

Пониженное потребление – питание ОЗУ через вход RESET (для n-МОП).

Вопрос №16.

Архитектура MCS-51

EPROM – память программ (4Кбайт);

RAM – память данных (128 байт);

PC – счётчик команд;

DPTR – двухбайтовый регистр-указатель данных;

DPL – младший байт регистра-указателя данных;

DPH – старший байт регистра-указателя данных;

RAR – регистр-указатель данных и автоматического вычисления следующего адреса резидентной памяти программ;

SP – Регистр указатель стека

PSW – схема формирования признаков результата операции;

ALU – 8-битное арифметико-логическое устройство;

DCU – схема десятичной коррекции;

T1 и T2 – программно-недоступные регистры, предназначенные для временного хранения операндов;

A – Аккумулятор

B – Регистр расширитель аккумулятора

CU – Устройство управления;

IR – регистр команд;

OSC – внутренний генератор;

P0 – Порт 0; - четыре двунаправленных побитно настраиваемых восьмиразрядных порта ввода-вывода;

P1 – Порт 1;

P2 – Порт 2;

P3 – Порт 3;

PCON – Регистр управления мощностью;

IE – Регистр маски прерывания;

IP – Регистр приоритетов;

TMOD – Регистр режимов таймеров счетчиков;

TCON – Регистр управления статуса таймеров;

TIMER0 – таймер 0;

TH0 – старший байт таймера 0;

TL0 – младший байт таймера 0;

TIMER1 – таймер 1;

TH1 – старший байт таймера 1;

TL1 – младший байт таймера 1;

SCON – регистр управления приемопередатчиком;

SBUF – буфер приемопередатчика 0

Вопрос №17.

Общая характеристика:

архитектура SISC - со стандартным набором команд;

111 основных команд;

длина команд – один, два или три байта, 94% – одно- или двухбайтные;

все команды выполняются за один или два машинных цикла (соответственно 1 или 2 мкс при тактовой частоте 12 МГц), исключение – команды умножения и деления, которые выполняются за четыре машинных цикла (4 мкс);

прямая, непосредственная, косвенная и неявная, адресация данных;

при прямом способе адрес операнда содержится в теле команды (код регистра),

при непосредственном способе 8-битный операнд записывается во втором байте команды,

при косвенном - адрес операнда размещается в одном из адресных регистров (R0 или R1),

при неявном способе в КОП содержится неявное указание на один из операндов;

имеется также возможность адресации отдельных бит некоторых регистров блока прерываний, таймеров и последовательного порта путем использования прямого 8-битного адреса (bit). При этом косвенная адресация невозможна.;

операнды команд могут использовать отдельные биты, четырехбитные цифры, байты и двухбайтные слова;

большое число операций ввода вывода и ветвлений программы.

Группы команд.

Система команд семейства MCS-51 содержит 111 базовых команд,

которые по функциональному признаку можно подразделить на пять:

пересылки данных;

арифметических операций;

логических операций;

операций над битами;

передачи управления.

Типы операндов

Состав операндов включает в себя операнды четырёх типов:

биты;

4-битные цифры;

байты;

16-битные слова.

Типы команд.

Всего микроЭВМ выполняют 13 типов команд, они приведены в таблице. Как следует из нее, первый байт команды всегда содержит код операции (КОП), а второй и третий (если они присутствуют в команде) – адреса операндов или их непосредственные значения.

Тип команды |

Первый байт D7...D0 |

Второй байт D7...D0 |

Третий байт D7...D0 |

тип 1 |

КОП |

|

|

тип 2 |

КОП |

#d |

|

тип 3 |

КОП |

ad |

|

тип 4 |

КОП |

bit |

|

тип 5 |

КОП |

rel |

|

тип 6 |

КОП |

а7...a0 |

|

тип 7 |

КОП |

ad |

#d |

тип 8 |

КОП |

ad |

rel |

тип 9 |

КОП |

ads |

add |

тип 10 |

КОП |

#d |

rel |

тип 11 |

КОП |

bit |

rel |

тип 12 |

КОП |

ad16h |

ad16l |

тип 13 |

КОП |

#d16h |

#d16l |

Обозначения, используемые при описании команд:

Rn (n = 0, 1,..., 7) – регистр общего назначения в выбранном банке регистров;

@Ri(i= 0, 1) – регистр общего назначения в выбранном банке регистров, используемый в качестве регистра косвенного адреса;

ad – адрес прямо адресуемого байта;

ads – адрес прямо адресуемого байта-источника;

add – адрес прямо адресуемого байта-получателя;

ad11 – 11-разрядный абсолютный адрес перехода;

ad16 – 16-разрядный абсолютный адрес перехода;

rel – относительный адрес перехода;

#d – непосредственный операнд;

#d16 – непосредственный операнд (2 байта);

bit – адрес прямо адресуемого бита;

/bit – инверсия прямо адресуемого бита;

А - аккумулятор;

РС – счетчик команд;

DPTR – регистр указатель данных;

( ) – содержимое ячейки памяти или регистра,

Обозначения, используемые при описании команд:

Rn (n = 0, 1,..., 7) – регистр общего назначения в выбранном банке регистров;

@Ri(i= 0, 1) – регистр общего назначения в выбранном банке регистров, используемый в качестве регистра косвенного адреса;

ad – адрес прямо адресуемого байта;

ads – адрес прямо адресуемого байта-источника;

add – адрес прямо адресуемого байта-получателя;

ad11 – 11-разрядный абсолютный адрес перехода;

ad16 – 16-разрядный абсолютный адрес перехода;

rel – относительный адрес перехода;

#d – непосредственный операнд;

#d16 – непосредственный операнд (2 байта);

bit – адрес прямо адресуемого бита;

/bit – инверсия прямо адресуемого бита;

А - аккумулятор;

РС – счетчик команд;

DPTR – регистр указатель данных;

( ) – содержимое ячейки памяти или регистра,

Пример подпрограммы на языке ASSEMBLER:

m1: ;метка

mov a,#88h ;перемещение числа 88h в аккумулятор

mov dptr,#8003h ;перемещение числа 8003h в DPTR

movx @dptr,a ;перемещение числа из аккумулятора в устройство

;по адресу DPTR

mov A,#55H ;перемещение числа 55h в аккумулятор

mov dptr,#8000h ;перемещение числа 8000h в DPTR

movx @dptr,a ;перемещение числа из аккумулятора в устройство

;по адресу DPTR

mov dptr,#8001h

movx @dptr,a

mov dptr,#8002h

movx a,@dptr

SWAP A ; Обмен местами тетрад в аккумуляторе

;(A0…3) ↔ (A4…7)

mov dptr,#8002h

movx @dptr,a

mov P1, #0dFh ;перемещение числа 0dfh в параллельный порт P1

ret ;возврат из подпрограммы

end

Вопрос №18.

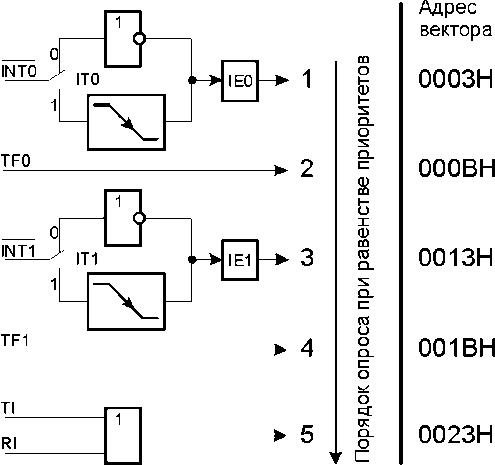

Упрощенная схема прерываний микроЭВМ 8051 показана на рисунке.

Схема прерываний.

Выполнение подпрограммы прерывания.

Система прерываний формирует аппаратный вызов (LCALL) соответствующей подпрограммы обслуживания, если она не заблокирована одним из следующих условий:

в данный момент обслуживается запрос прерывания равного или высокого уровня приоритета;

текущий машинный цикл — не последний в цикле выполняемой команды;

выполняется команда RETI или любая команда, связанная с обращением к регистрам IЕ или IP.

Отметим, что если флаг прерывания был установлен, но по одному из указанных выше условий не получил обслуживания и к моменту окончания блокировки уже сброшен, то запрос прерывания теряется и нигде не запоминается.

По аппаратно сформированному коду LCALL система прерывания помещает в стек только содержимое счетчика команд (PC) и загружает в него адрес вектора соответствующей подпрограммы обслуживания. По адресу вектора должна быть расположена команда безусловной передачи управления (JMP) к начальному адресу подпрограммы обслуживания прерывания. В случае необходимости она должна начинаться командами записи в стек (PUSH) слова состояния программы (PSW), аккумулятора, расширителя, указателя данных и т.д. и должна заканчиваться командами восстановления из стека (POP). Подпрограммы обслуживания прерывания должны завершаться командой RETI, по которой в счетчик команд перезагружается из стека сохраненный адрес возврата в основную программу. Команда RET также возвращает управление прерванной основной программе, но при этом не снимут блокировку прерываний, что приводит к необходимости иметь программный механизм анализа окончания процедуры обслуживания данного прерывания.

Регистр масок прерывания (IE)

|

Разряд регистра IE |

|

|

|

|

|||||||

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

|

||

0A8: |

EA |

- |

- |

ES |

ET1 |

EX1 |

ET0 |

EX0 |

168 |

IE |

0x000000B |

|

Символ |

Позиция |

Имя и назначение |

EA |

IE.7 |

Снятие блокировки прерывания. Сбрасывается, программно для запрета всех прерываний независимо от состояний IE.4 - IE.0 |

|

IE.6 |

Не используется |

|

lE.5 |

Не используется |

ES |

IE.4 |

Бит разрешения прерывания, от приемопередатчика Установка/сброс программой для разрешения/запрета прерываний от флагов TI или RI . |

ET1 |

IE.3 |

Бит разрешения прерывания от таймера. Установка/сброс программой для разрешения/запрета прерываний от таймера 1 |

EX1 |

IE.2 |

Бит разрешения внешнего прерывания 1. Установка/сброс программой для разрешения/запрета прерывания 1 |

ET0 |

IE.1 |

Бит разрешения прерывания от таймера 0. Установка/сброс программой для разрешения/запрета прерываний от таймера 0 . |

EX0 |

IE.0 |

Бит разрешения внешнего прерывания 0. Установка/сброс программой для разрешения/запрета прерывания 0 |

Регистр приоритетов прерываний (IP).

|

Разряд регистра IP |

|

|

|

|

||||||||||

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

|

|||||

0B8: |

- |

- |

- |

PS |

PT1 |

PX1 |

PT0 |

PX0 |

184 |

IP |

xx000000B |

||||

Символ |

Позиция |

Имя и назначение |

- |

IP.7 - IP.5 |

Не используется |

PS |

IP.4 |

Бит приоритета приемопередатчика. Установка/сброс программой для присваивания прерыванию от приемопередатчика высшего/низшего приоритета |

РТ1 |

IP.3 |

Бит приоритета таймера 1. Установка/сброс программой для присваивания прерыванию от таймера 1 высшего/низшего приоритета |

РХ1 |

IP.2 |

Бит приоритета внешнего прерывания 1. Установка/сброс программой для присваивания высшего/низшего приоритета внешнему прерыванию INT1 |

РТ0 |

IP.1 |

Бит приоритета таймера 0. Установка/сброс программой для присваивания прерыванию от таймера 0 высшего/низшего приоритета |

РХ0 |

IP.0 |

Бит приоритета внешнего прерывания 0. Установка/сброс программой для присваивания высшего/низшего приоритета внешнему прерыванию INT0 |

Таймеры / счетчики микроЭВМ семейства 8051

В базовых моделях семейства имеются два программируемых 16-битных таймера/счетчика (T/C0 и T/C1), которые могут быть использованы как в качестве таймеров, так и в качестве счетчиков внешних событий.

В первом случае содержимое соответствующего таймера/счетчика (Т/С) инкрементируется в каждом машинном цикле, т.е. через каждые 12 периодов колебаний кварцевого резонатора.

Во втором оно инкрементируется под воздействием перехода из 1 в 0 внешнего входного сигнала, подаваемого на соответствующий (T0,T1) вывод микро-ЭВМ 8051. Так как на распознавание периода требуются два машинных цикла, максимальная частота подсчета входных сигналов равна 1/24 частоты резонатора. На длительность периода входных сигналов ограничений сверху нет. Для гарантированного прочтения входной сигнал должен удерживать значение 1, как минимум, в течение одного машинного цикла микро-ЭВМ.

Для управления режимами работы Т/С и для организации их взаимодействия с системой прерываний используются два регистра специальных функций (TCON и TMOD), описание которых приведено ниже.

Шестнадцатеричный адрес |

|

Имя регистра Битовый адрес |

|

|

Десятичный адрес |

Состояние после сброса |

|

|

|

|

|

||||||||

|

Разряд регистра управления таймеров - счётчиков |

|

|

|

|

||||||||||||||

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

|

|||||||||

88h: |

TF1 8F |

TR1 8Е |

TF0 8D |

TR0 8С |

IE1 8В |

IT1 8А |

IE0 89 |

IT0 88 |

136 |

TCON |

00h |

||||||||

|

Разряд регистра управления таймеров - счётчиков |

|

|

|

|

||||||||||

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

|

|||||

88h: |

TF1 8F |

TR1 8Е |

TF0 8D |

TR0 8С |

IE1 8В |

IT1 8А |

IE0 89 |

IT0 88 |

136 |

TCON |

00h |

||||

Блок прерываний, таймеров и последовательного порта

Символ |

Позиция |

Имя и назначение |

TF1 |

TCON.7 |

Флаг переполнения таймера 1. Устанавливается аппаратно при переполнении таймера/счетчика. Сбрасывается при обслуживании прерывания аппаратно |

TR1 |

TCON.6 |

Бит управления таймера 1. Устанавливается, / сбрасывается программой для пуска/останова |

TF0 |

TCON.5 |

Флаг переполнения таймера 0. Устанавливается аппаратурно. Сбрасывается при обслуживании прерывания |

TR0 |

TCON.4 |

Бит управления таймера 0. Устанавливается / сбрасывается программой для пуска/останова таймера/счетчика |

IE1 |

TCON.3 |

Флаг фронта прерывания 1. Устанавливается аппаратно, когда детектируется срез внешнего сигнала INT1. Сбрасывается при обслуживании прерывания |

IT1 |

TCON.2 |

Бит управления типом прерывания 1. Устанавливается / сбрасывается программно для спецификации запроса INT1 (срез/низкий уровень) |

IE0 |

TCON.1 |

Флаг фронта прерывания 0. Устанавливается по срезу сигнала INT0. Сбрасывается при обслуживании прерывания |

IT1 |

TCON .0 |

Бит управления типом прерывания 0. Устанавливается / сбрасывается программно для спецификации запроса INT0 (срез/низкий уровень) |

Символ |

Позиция |

Имя и назначение |

GATE |

TMOD.7 для Т/С1 и TMOD.3 для Т/СО |

Управление блокировкой. Если бит установлен, то таймер/счетчик "x" разрешен до тех пор, пока на входе "lNTx" высокий уровень и бит управления "TRx" установлен. Если бит сброшен, то Т/С разрешается, как только бит управления "TRx" устанавливается |

С/Т |

TMOD.6 для T/C1 и TMOD.2 для Т/СО |

Бит выбора режима таймера или счетчика событий. Если бит сброшен, то работает таймер от внутреннего источника сигналов синхронизации. Если; установлен, то работает счетчик от внешних сигналов на входе "Tx" |

M1 |

TMOD.5 для T/C1 и TMOD.1 для Т/СО |

|

Пример программы с использованием таймера и прерывания.

lcall m0

org 0bh

lcall n1

mov tcon,00h

mov TL0, #0f5h ;value set by user

mov TH0, #0fah ;value set by user

setb TR0 ;TCON.4 start timer

n1: reti

ORG 30h

m0: lcall init_special_interrupts

lcall init_timer0

m1: ljmp m1