- •1. Электронные ключи

- •2. Логические функции

- •3. Характеристики и параметры потенциальных логических элементов (лэ).

- •5. Цифровые компараторы.

- •6.Счетчики импульсов.

- •6.1.Их назначение, классификация и основные показатели. Методы описания работы счетчиков.

- •6.2.Основы построения суммирующих, вычитающих и реверсивных счетчиков.

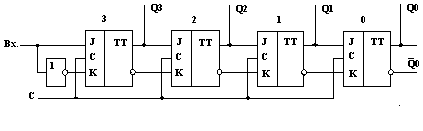

- •6.3.Примеры схем счетчиков на dv- и jк-триггерах.

- •6 .5.Счетчики промышленных серий.

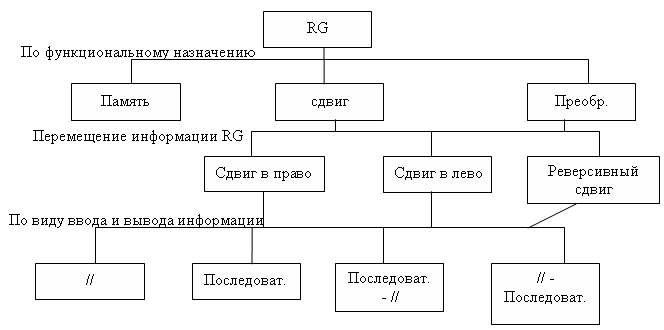

- •7.Регистры.

- •7.1.Их назначение, классификация и типы.

- •7.2.Основы построения схем регистров.

- •7.3.Свойства регистров с обратными связями.

- •7.4.Примеры схем регистров на dv-, jк-триггерах.

- •7.5.Организация зу на регистре параллельного действия.

- •7.6.Регистры на имс. См. В шиле(любой регистр например к155ир1 стр 105).

- •7.7.Применение регистров в кмоп-структурах.

- •8.2 Статические и динамические зу на биполярных и моп- структурах.

- •8.3 Элементы памяти озу и пзу.

- •8.4 Режимы записи, хранения и считывания информации в зу.

- •8.5 Репрограммируемые пзу, организация, работа.

- •8.8 Программируемые логические матрицы (плм).

- •8.9 Режимы программирования бис пзу.

- •10. Генераторы линейно изменяющегося напряжения (глин) их характеристики и параметры.

Выход Q – основной, по нему судим, в каком состоянии находится триггер.

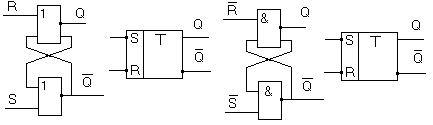

Триггер на элементах или/не

![]()

![]()

![]()

Асинхронные и синхронные триггеры RS-типа.

По способу приема информации триггеры подразделяют на асинхронные и синхронные. Асинхронные триггеры реагируют на информационные сигналы в момент их появления на входе. Синхронные – при наличии разрешающего сигнала специально предусмотренном входе С.

Асинхронный RS – триггер.

Имеет два информационных входа: S и R для установки "1" и "0" соответственно, а также два входа прямой Q и инверсный `Q.

С хемы

триггера на ЛЭ ИЛИ-НЕ и И-НЕ приводятся

на рисунке

хемы

триггера на ЛЭ ИЛИ-НЕ и И-НЕ приводятся

на рисунке

Активным называют логический уровень, действующий на вход ЛЭ и однозначного определяющий логический уровень выходящего сигнала (независимо от уровней действующих на других входах). Для ЛЭ ИЛИ-НЕ за активный уровень принимают высокий уровень (H), а для элемента И-НЕ – низкий (L – уровень). Уровни, подача которых на один из входов не приводит к изменению логического уровня на выходе, называют пассивными. Уровни Qt+1 и `Qt+1 обозначают логические уровни на выходе триггера после подачи информации на его входы.

Для триггера с прямыми входами при

S=1 и R=0 Qt+1=1

S=0 R=1 Qt+1=0

S=0 R=0 Qt+1=Qt

S=1 R=1 – состояние триггера будет неопределенным, так как во время действия информационных сигналов ЛУ на выходах триггера одинаковы: Qt+1=`Qt+1=0, а после окончания их действия триггер может равновероятно принять любое из устойчивых состояний. Поэтому такая комбинация является запрещенной.

Режим S=1, R=0 называют режимом записи "1" (так как Qt+1=1); режим S=0, R=0 называется режимом хранения информации, так как информация на входе остается неизменной.

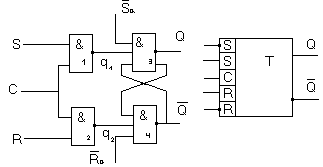

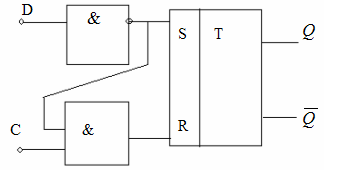

Синхронный RS – триггер.

Синхронный (тактируемый) RS–триггер получается из асинхронного путем подключения к его входам схемы управления.

Здесь Sа и Ra – асинхронные входы, а S и R информационные входы. Вход С – тактовый (синхронизированный), q1 и q2 – внутренние сигналы, управляют соответственно триггером, который, как его асинхронный аналог на элементе И-НЕ, переключается сигналами нулевого уровня.

Триггеры Т-, ТV-, D-, DV-типов.

Q2

Q1

T

1

T

S2

C

R2

S1

C

R1

C (T)

Q2=1

![]()

![]()

![]()

С приходом такта

перепады напряжения

![]() и 1 триггер 1

переключается, а 2ой в это время закрыт

по входу С.

и 1 триггер 1

переключается, а 2ой в это время закрыт

по входу С.

Для 1ого перепад отрицательный, для второго положительный, триггер переключится

После окончания

такта ситуация на выходе второго триггера

изменится.

T

Получаем счетный

триггер

V

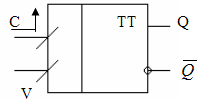

D-триггер имеет информационный вход D и вход синхронизации. Одна из возможных схем однотактного D-триггера и его условные обозначения приведены на рисунке. Д-триггер отличается от RS-триггера тем, что у него один информационный вход. Таблица истинности: (Dn= Qn+1)

Dn |

Qn |

Qn+1 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

Е

Существуют D-триггеры, в которых параллельно С-сигналу на входные элементы заведен еще один разрешающий сигнал – V-сигнал. Такие триггеры называются DV-триггерами. Разрешением на прием D-уровня является конъюнкция сигналов на С- и V-входах.

DV-триггер – это синхронный D-триггер, который работает следующим бразом: Если V =1, то триггер работает как D-триггер. Если V=0, то триггер хранит информацию.

|

V |

D |

Q n |

Q n+1 |

V=0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

|

0 |

0 |

0 |

0 |

|

0 |

1 |

1 |

1 |

|

V=1 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

|

1 |

1 |

0 |

1 |

|

1 |

1 |

1 |

1 |

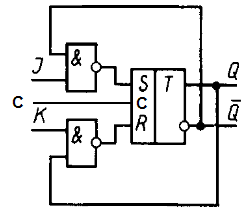

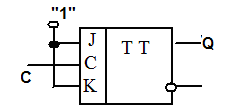

Двухтактные триггеры JК-типов

JK-триггер имеет два информационных входа (J, K), а также вход для подачи тактовых импульсов (С).

На схемах JK- триггер

обозначается следующим образом: JK-

триггер отличается от синхронного

RS-триггера тем, что не имеет запрещенной

комбинации. Если J=K=1, то триггер работает

в режиме счетного триггера Qn+1=![]() n.

n.

На схемах

двухступенчатый JK-триггер обозначают:

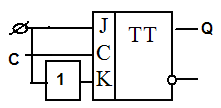

Организация триггеров других типов на основе JK-триггера.

Поскольку JK-триггер считается универсальным, то на его основе можно построить другие триггеры.

Тактируемый

триггер получается автоматически:

![]() ;

подключен инвертор

;

подключен инвертор

к входу K

входу K

Счетный триггер, который будет делить тактовую частоту вдвое.

Триггеры на ЭСЛ, МОП-, КМОП-структурах.

Промышленность выпускает большое количество интегральных микросхем триггеров, построенных на эммитерно-связанной логике (ЭСЛ), комплементарных полевых транзисторах (КМОП), МОП-транзисторах.

Основная деталь ЭСЛ-логики — схема потенциального сравнения, собранная не на диодах (как в ДТЛ и ТТЛ), а на транзисторах. Схема представляет из себя транзисторы, соединённые эмиттерами и подключенные к корпусу (или питанию) через резистор. При этом транзистор у которого напряжение на базе выше пропускает через себя основной ток. Как правило один транзистор в схеме сравнения подключен к опорному уровню единицы (обычно просто стабилитрон), а остальные транзисторы являются входами. Выходные цепи схемы сравнения поступают на усилительные транзисторы, а с них — на выходные эмиттерные повторители.

МОП (металл-окисел-полупроводник) — это самый простой тип полевого транзистора. Полевые транзисторы создавались для преодоления недостатков обычных биполярных транзисторов и особенно преодоления частоты в 100 МГц. Но из-за слишком простой конструкции МОП-транзистор работает очень медленно. Особенно это касается p-МОП схем где носителем зарядя являются малоподвижные ионы кристаллической решётки.

МОП-транзистор часто называют электронным аналогом лампового триода. Своим электрическим полем (на выводе затвора) он индуцирует переход практически в обычном биполярном транзисторе. При этом появляется переход по которому течёт ток. При изменении полярности на затворе переход исчезает, ток не проходит. Логический МОП-элемент представляет из себя два транзистора n-МОП или p-МОП с резисторами смещения. В зависимости от напряжения на входе включается либо первый либо второй транзистор, при этом на выход поступает либо напряжение питания либо корпус. Для повышения степени интеграции и экономичности в ходе усовершенствований удалось избавиться от «не нужных» резисторов.

В технологии КМОП используются полевые транзисторы с изолированным затвором с каналами разной проводимости. Отличительной особенностью схем КМОП по сравнению с биполярными технологиями (ТТЛ, ЭСЛ и др.) является очень малое энергопотребление в статическом режиме (в большинстве случаев можно считать, что энергия потребляется только во время переключения состояний). Отличительной особенностью структуры КМОП по сравнению с другими МОП-структурами (N-МОП, P-МОП) является наличие как n-, так и p-канальных полевых транзисторов; как следствие, КМОП-схемы обладают более высоким быстродействием и меньшим энергопотреблением, однако при этом характеризуются более сложным технологическим процессом изготовления и меньшей плотностью упаковки.

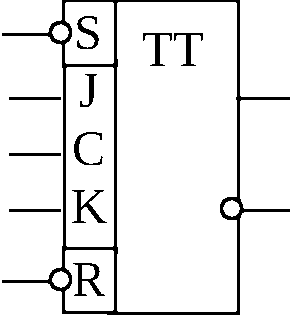

Классификация и условное обозначение триггеров согласно ГОСТу.

Условное обозначение интегральных микросхем триггеров состоит из обозначения серии (трех или четырех цифер), функционального назначения (двух букв) и порядкового номера разработки (от одной до трех цифр). По функциональному назначению триггеры имеют следующие обозначения: ТР – SR-триггеры, ТВ – JK-триггеры, ТМ – D-триггеры, ТТ – Т-триггеры, ТП – прочие триггеры.

6.Счетчики импульсов.

Счетчик – функциональный узел, предназначенный для подсчета числа входных сигналов и запоминания кода этого числа соответствующими триггерами. Результат счета в них записывается в двоичном коде. Максимальное число N, которое может быть записано в счетчике равно (2n –1), где n-число разрядов счетчика. Каждый разряд счетчика включает в себя триггер.

6.1.Их назначение, классификация и основные показатели. Методы описания работы счетчиков.

По направлению счета счетчики делятся на: суммирующие, вычитающие, реверсивные.

В суммирующих счетчиках с приходом очередного импульса результат увеличивается на 1, а в вычитающих - уменьшается на 1. Реверсивные счетчики могут работать как в том, так и в другом режиме. Направление счета задается управляющим сигналом.

По способу организации внутренних связей: с последовательным переносом(асинхронные счетчики), с параллельным переносом (синхронные счетчики), с комбинированным переносом(счетчики с параллельно-последовательным переносом).

В асинхронных счетчиках подсчитываемые импульсы поступают на вход только первого триггера. Каждый последующий триггер управляется сигналом предыдущего. В синхронных счетчиках входные импульсы обычно подаются одновременно на вход С всех триггеров. Переключение только нужных из них осуществляется с помощью логических цепей, имеющихся на J – м и К- м входах отдельных триггеров. Комбинированный перенос применяется при построении многоразрядных счетчиков

Основные параметры счетчиков:

1. Емкость счетчика

(это количество импульсов, которое

необходимо подать на его вход, чтобы он

вернулся в исходное состояние). Если он

m-разрядный, то его емкость

![]() .

.

2. Быстродействие( оно характеризуется либо максимальной частотой счета, либо минимально допустимым интервалом между моментами поступления счетных импульсов).

Счетчики предназначены для коммерческого учета активной электроэнергии в однофазных и трехфазных цепях переменного тока номинальной частотой 50 Гц и работают как автономно, так и в составе АСКУЭ.

6.2.Основы построения суммирующих, вычитающих и реверсивных счетчиков.

В начальный момент времени все триггеры

устанавливаются сигналом Уст 0 в состояние

“0”. После прихода первого счетного

импульса триггер Тг1 перейдет в состояние

“1” и в счетчике зафиксируется код

001.Второй импульс, пришедший на вход,

переведет Тг1 снова в состояние “0”.

При этом возникает импульс переноса,

который устанавливает следующий триггер

Тг2 в состояние “1” и в счетчике

зафиксируется код 010. После третьего

входного сигнала Тг1 вновь прейдет в

состояние “1”, а остальные триггеры

останутся в прежнем состоянии. Так будет

продолжаться до тех пор, пока счетчик

не просуммирует максимальное для трех

разрядов число 710=1112.

Восьмой импульс переведет Тг1 в состояние

“02, возникший перенос поступит на Тг2

и также переведет его в состояние “0”.

В свою очередь, импульс переноса со

второго разряда переведет в состояние

“0” и Тг3. В результате этого счетчик

установится в исходное нулевое состояние

(000).

начальный момент времени все триггеры

устанавливаются сигналом Уст 0 в состояние

“0”. После прихода первого счетного

импульса триггер Тг1 перейдет в состояние

“1” и в счетчике зафиксируется код

001.Второй импульс, пришедший на вход,

переведет Тг1 снова в состояние “0”.

При этом возникает импульс переноса,

который устанавливает следующий триггер

Тг2 в состояние “1” и в счетчике

зафиксируется код 010. После третьего

входного сигнала Тг1 вновь прейдет в

состояние “1”, а остальные триггеры

останутся в прежнем состоянии. Так будет

продолжаться до тех пор, пока счетчик

не просуммирует максимальное для трех

разрядов число 710=1112.

Восьмой импульс переведет Тг1 в состояние

“02, возникший перенос поступит на Тг2

и также переведет его в состояние “0”.

В свою очередь, импульс переноса со

второго разряда переведет в состояние

“0” и Тг3. В результате этого счетчик

установится в исходное нулевое состояние

(000).

Построения вычитающего счетчика.

Первый счетчик будет изменять свое состояние на каждый отрицательный фронт входного импульса. Т.к. выход первого триггера инверсный, то второй триггер будет изменять свое состояние на каждый положительный фронт импульса для прямого выхода Q1. Третий счетный триггер срабатывает на положительный фронт импульса на прямом выходе Q2. Таким образом состояния будут уменьшаться на 1. Т.е. чтобы получить вычитающий счетчик, нужно взять сигнал с инверсного выхода. Если изменить тип входа счетчика, то также изменится и направление счета.

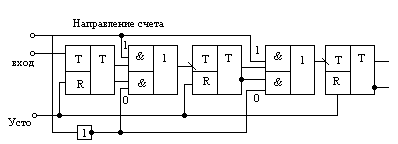

Построение реверсивного счетчика.

Между триггерами стоят мультиплексоры, которые позволяют пропускать сигнал или с прямого или с инверсного выхода предыдущего триггера, что влияет на направление счета.

Если на направлении счета 1, то счетчик будет суммирующим, если 0, то вычитающим.

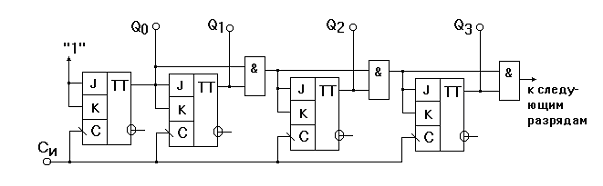

Все рассмотренные счетчики являются счетчиками с последовательным переносом и их максимальная задержка может быть в m раз больше, чем у одного триггера, т. е. в число каскадов раз. Избавляются от этого недостатка с помощью синхронных счетчиков. Синхронными они называются потому, что в них все триггеры срабатывают одновременно и максимальная задержка равна задержке одного триггера.

Работа таких счетчиков основана на том, что переключение каждого триггера происходит тогда, когда на всех предшествовавших триггерах единичное состояние.

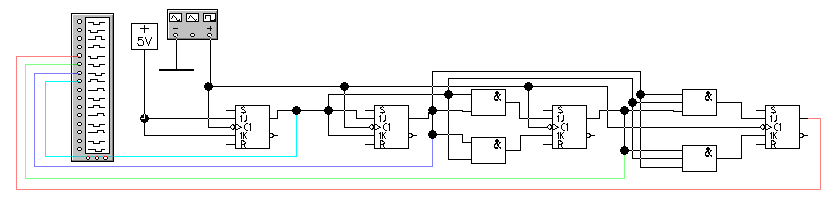

6.3.Примеры схем счетчиков на dv- и jк-триггерах.

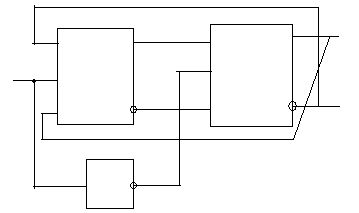

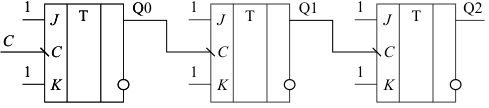

П ример

асинхронного трехразрядного двоичного

суммирующего счетчика

приведен на рис. Для построения этого

счетчика

использованы JK-триггеры

с динамической синхронизацией по спаду

синхросигнала. Каждый JK-триггер

в счетчике

включен в режим инвертирования своего

состояния при переключении синхросигнала

с высокого уровня на низкий.

ример

асинхронного трехразрядного двоичного

суммирующего счетчика

приведен на рис. Для построения этого

счетчика

использованы JK-триггеры

с динамической синхронизацией по спаду

синхросигнала. Каждый JK-триггер

в счетчике

включен в режим инвертирования своего

состояния при переключении синхросигнала

с высокого уровня на низкий.

Синхронный последовательный счетчик.

П о

способу подачи синхроимпульсов такие

счетчики параллельные, т.е. синхроимпульсы

поступают на все триггеры счетчика

параллельно, а по способу управления

(подачи управляющих импульсов) -

последовательные. Схема синхронного

последовательного счетчика, реализованного

на JK-триг-герах, приведена на рис.

о

способу подачи синхроимпульсов такие

счетчики параллельные, т.е. синхроимпульсы

поступают на все триггеры счетчика

параллельно, а по способу управления

(подачи управляющих импульсов) -

последовательные. Схема синхронного

последовательного счетчика, реализованного

на JK-триг-герах, приведена на рис.

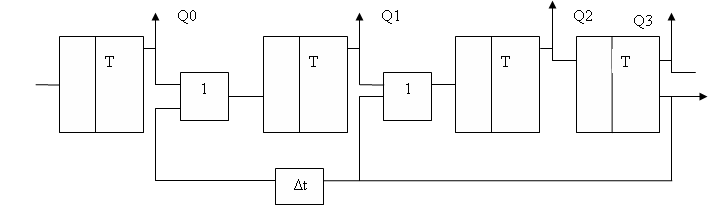

6.4. 2-10-счетчики, их организация и проектирование.

![]() - возникает

задача организовать счетчик. Для

организации таких счетчиков приходится

использовать логические связи введение

обратной связи.

- возникает

задача организовать счетчик. Для

организации таких счетчиков приходится

использовать логические связи введение

обратной связи.

Частный случай: 2- 10 счетчик. Он строится на основе 4-х триггеров, двоичных счетчиков, но N= 16, лишние комбинации (6 шт) надо куда- то деть. В преобр. технике используется большое число 2-10 счетчиков, но наибольшее распространение получили 8-4-2-1 и 2-4-2-1.

![]() ,

где Qi – двоичные числа в разрядах кодовой

комбинации, ai –некоторые

постоянные числа называемые весами.

Такие коды наз. взвешенные. Они применяются

в преобразователях в цифро – аналоговых

и аналогово – цифровых и т. д.

,

где Qi – двоичные числа в разрядах кодовой

комбинации, ai –некоторые

постоянные числа называемые весами.

Такие коды наз. взвешенные. Они применяются

в преобразователях в цифро – аналоговых

и аналогово – цифровых и т. д.

неQ3

Δt – задержка времени.

6 .5.Счетчики промышленных серий.

- реверсивный

счетчик

- реверсивный

счетчик

- однонаправленный

счетчик

- однонаправленный

счетчик

1,2,4,8 - входы параллельной загрузки счетчика

РЕ - вход разрешения параллельной загрузки счетчика

R0- вход установки счетчика в нулевое состояние

+1 - вход счетчика в режиме суммирования

-1 - вход счетчика в режиме вычитания

У счетчика два выхода ( 15, 0), которые используются при наращивании разрядности счетчика.

7.Регистры.

Регистром называют последовательностное цифровое устройство, предназначенное для хранения или хранения и сдвига данных. В первом случае их называют регистрами памяти, а во втором - регистрами сдвига.

7.1.Их назначение, классификация и типы.

Назначение регистров – хранение и преобразование много разрядных двоичных чисел. Регистры наряду со счетчиками и запоминающими устройствами являются наиболее распространенными последовательностными устройствами цифровой техники. Регистры обладают большими функциональными возможностями. Они используются в качестве управляющих и запоминающих устройств, генераторов и преобразователей кодов, счетчиков, делителей частоты, узлов временной задержки.

По наличию синхронизации различают асинхронные и синхронные, а также статические и динамические.

Работа RG описывается таблицей переходов. Любой RG состоит из отдельных одинаковых блоков, каждый из них содержит триггер и устройство управления. Наиб. распространение получили статические RG. Каждому разряду слова соотв. разряд RG, выполненный на основе статич. триггеров.

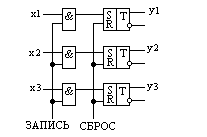

7.2.Основы построения схем регистров.

Построение регистров сдвига на одноступенчатых триггерах со статическим входом невозможно.

П остроение

регистра памяти на RS-триггерах.

остроение

регистра памяти на RS-триггерах.

Регистр памяти представляет собой совокупность RS-триггеров. Чем больше информации нужно хранить, тем больше триггеров нужно использовать, т.к. один триггер хранит один бит информации.

Те входы триггеров, на которых присутствует ноль, будут обеспечивать режим хранения, а где единица - режим записи. Чтобы записать правильную информацию, нужно регистр очистить, т.е. перед началом установить сброс. Это является недостатком таких регистров, от которого можно избавиться, построив регистр на D-триггерах.

Рассмотрим построение регистров памяти на D-триггерах.

Такой регистр представляет собой совокупность D-триггеров, управляемых одновременно.

Входы D - это входы регистра, входы R - входы сброса, входы С объединяются и служат входом записи. Регистры перед записью могут находиться в любом состоянии и их состояние определяется состоянием входа D, то перед записью их необязательно сбрасывать в ноль.

Аналогично регистры памяти можно построить на JK-триггерах, но в этом случае схема будет сложнее.

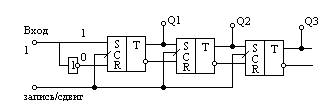

Построение регистров сдвига.

Т.к. это

регистр сдвига, то входы должны быть

динамическими. Такой регистр представляет

собой цепочку триггеров, в которой входы

последующих триггеров соединены с

выходами предыдущих.

Т.к. это

регистр сдвига, то входы должны быть

динамическими. Такой регистр представляет

собой цепочку триггеров, в которой входы

последующих триггеров соединены с

выходами предыдущих.

С приходом положительного фронта входного импульса информация записывается в первый триггер, а затем она будет переписываться в последующие и будет сдвигаться на один разряд. При таком построении считывание будет параллельным, а ввод информации - последовательным.

Таким образом основным предназначением регистров сдвига является преобразование кода из последовательного представления в параллельное.

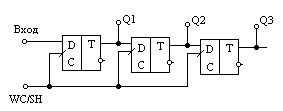

П остроение

регистров сдвига на D-триггерах.

остроение

регистров сдвига на D-триггерах.

При подаче положительного фронта импульса информация записывается в первый триггер, а затем одновременно во второй, потом - в третий. И, до прихода следующего тактирующего импульса, информация запоминается, т.е. триггеры находятся в режиме хранения.

Те же триггеры соединили в обратном порядке. При этом освобождается крайний правый разряд и информация сдвигается на один триггер в обратную сторону.

Для построения реверсивного регистра сдвига нужно поставить между каждым из триггеров мультиплексор. Один вход соединить с предыдущим триггером, а второй вход с последующим. Если в регистр нужно загрузить данные, то схему усложняют.

РЕ- вход разрешения параллельной загрузки. Если на оба входа V подается нулевой уровень, а на РЕ-вход единица, то при этом разрешается прохождение информации на вход триггера. Аналогично осуществляется загрузка счетчика.

7.3.Свойства регистров с обратными связями.

1. преобразование параллельного кода в последовательный. В регистр загружаются данные, а затем сдвигаются по битам, при этом выходом будет служить выход Q1.

2. преобразование последовательного кода в параллельный. Данные при этом подаются на вход и сдвигаются.

3. используются при умножении и делении.

4. задерживают передачу информации на n-тактов, где n - число разрядов регистра.

5. для построения кольцевых счетчиков или распределителей импульсов.

6. для построения счетчиков Джонсона.

7. для построения памяти типа “очередь” (FIFO, принцип такого построения: ”первым вошел, первым вышел”).

8. для построения буферной памяти типа “очередь”(LIFO, принцип такого построения : ”последним вошел, первым вышел”). Это используется для построения стека.

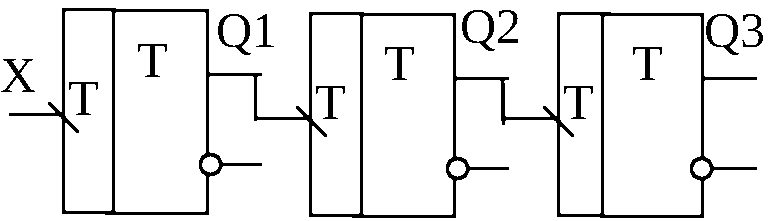

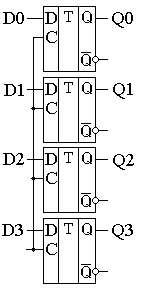

7.4.Примеры схем регистров на dv-, jк-триггерах.

С

оставляется

регистр сдвига из соединенных

последовательно триггеров, в которые

записываются разряды обрабатываемого

кода. При наличии разрешающих сигналов

импульс, приходящий на тактовый вход

регистра, вызывает перемещение записанной

информации на один разряд влево или

вправо. На рис. приведена структурная

схема регистра сдвига на синхронных

JK-триггерах.

оставляется

регистр сдвига из соединенных

последовательно триггеров, в которые

записываются разряды обрабатываемого

кода. При наличии разрешающих сигналов

импульс, приходящий на тактовый вход

регистра, вызывает перемещение записанной

информации на один разряд влево или

вправо. На рис. приведена структурная

схема регистра сдвига на синхронных

JK-триггерах.

Пример. Схема четырехразрядного параллельного регистра.

7.5.Организация зу на регистре параллельного действия.

Регистры хранения обеспечивают запись, хранение и выдачу

информации в параллельном коде. От количества триггеров,

входящих в состав регистра, зависит разрядность записанного числа.

Так, при наличии четырех триггеров можно записать четырехразрядное

слово, восьми – восьмиразрядное и т. д. Схема простейшего параллельного

регистра хранения приведена на рис. Информация в триггеры DD2, DD4 и

D D6

записываются по срезу импульса на входе

С.

D6

записываются по срезу импульса на входе

С.

7.6.Регистры на имс. См. В шиле(любой регистр например к155ир1 стр 105).

7.7.Применение регистров в кмоп-структурах.

Регистры применяются непосредственно для создания таких структур: счетчиков и регистров, а также в процессоре хранения данных, и в качестве буфера на шинах ввода-вывода в этих структурах. Пример: К561ИЕ11 двоичный реверсивный счетчик на КМОП-логике; К561ИР9 – четырех-разрядный последовательно-параллельный регистр на КМОП –структуре.

8.Запоминающие устройства (ЗУ). 8.1 Типы ЗУ, организация ЗУ.

Память - функциональная часть ЭВМ, микроконтроллера, микропроцессора предназначенная для записи, хранения и выдачи данных. ЗУ - устройство реализующее ф-и памяти данных.

ЗУ делят на: ОЗУ(для использования в высоком темпе обработки информации) и ПЗУ(для хранения однажды записанной информации).

По способу хранения память: статическая и динамическая

По способу организации обмена данных: с произвольной выборкой(RAM), с последов. обращением.

По характеру обращения: с адресным обращением, с ассоциативной выборкой.

Основные эл.параметры ЗУ:

1.Емкость –кол-во информации которое можно записать в ЗУ. N=2m

(m-разрядность двоичного кода, все ячейки с информацией пронумерованы(№ячейки-адрес))

2.Быстродействие характеризуется:

tв- время между подачей команды и получением данных,

tц-время между командой на запись и командой на выдачу информации.

8.2 Статические и динамические зу на биполярных и моп- структурах.

С татические

ЗУ(СЗУ)- в

которых состояния носителя, соответствующие

записанному коду, неподвижны относительно

носителя информации(СЗУ м.б. устойчивыми,

в которых информация сохраняется

неограниченно долго (триггерах, ферритовых

сердечниках), и неустойчивыми, обладающими

свойством самопроизвольного стирания

информации (конденсаторные ЗУ, запоминающие

электроннолучевые трубки). Любое ОЗУ

состоит из накопителя и схем управления

татические

ЗУ(СЗУ)- в

которых состояния носителя, соответствующие

записанному коду, неподвижны относительно

носителя информации(СЗУ м.б. устойчивыми,

в которых информация сохраняется

неограниченно долго (триггерах, ферритовых

сердечниках), и неустойчивыми, обладающими

свойством самопроизвольного стирания

информации (конденсаторные ЗУ, запоминающие

электроннолучевые трубки). Любое ОЗУ

состоит из накопителя и схем управления

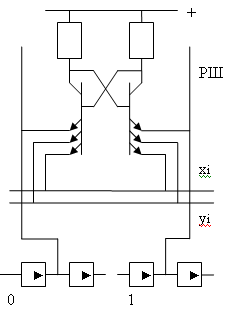

З апоминающая

ячейка статического типа.

апоминающая

ячейка статического типа.

Если шина xi и yi активированы, то триггер переходит в активный режим и в него можно записать 0/1 или считать. Выход с эмиттера обеспечивает меньшее выходное сопротивление триггера.

Динамические ЗУ – которых последовательность сигналов, соответствующая фиксируемому коду, циркулирует по замкнутому контуру, включающему линии задержки. Динамические МОП структуры –ячейки памяти.

П о

команде открывается транзистор V1

и емкость подключается ко входу это же

напряжение подключается к емкости. Если

V3

открыт, то на шине появляется напряжение

которое имеется наконденсаторе.

о

команде открывается транзистор V1

и емкость подключается ко входу это же

напряжение подключается к емкости. Если

V3

открыт, то на шине появляется напряжение

которое имеется наконденсаторе.

8.3 Элементы памяти озу и пзу.

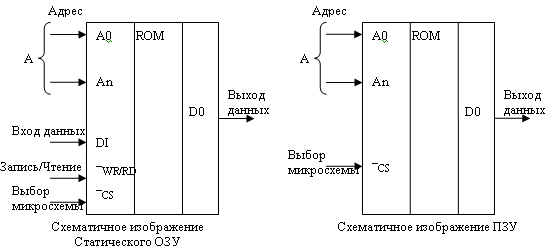

ОЗУ состоит из накопителя и схем управления. Накопитель пространства памяти состоит из заполняющих ячеек, каждая из которых хранит 1бит, а схема управления организует запись, выборку и считывание информации. Пространством памяти управляет дешифратор.

Организация пространства памяти- матричная (имеется матрица из m рядов и n колонок). Количество ячеек определяет емкость накопителя(m*n), в ячейку можно записать 1бит.

ПЗУ являются преобразователями кода адреса в код слова, т. е. комбинационной системой с n входа- ми и m выходами. Накопитель ПЗУ обычно выполняется в виде системы взаимно перпендикулярных шин, в пересечениях которых либо стоит (логическая 1), либо отсутствует (логический 0) элемент, связывающий между собой соответствующие горизонтальную и вертикальную шины. Выборка слов производится так же, как и в ОЗУ, при помощи дешифратора. Выходные транзисторы усилителей могут быть с открытым коллектором или с третьим состоянием. Тогда при стробирующем сигнале V=1 микросхема отключается от выходной шины, что позволяет наращивать память простым объединением выходов микросхем ПЗУ.

Самым простым ПЗУ является ПЗУ на диодах(диод-элемент памяти).

8.4 Режимы записи, хранения и считывания информации в зу.

ОЗУ может работать в режимах записи, считывания и хранения информации, а ПЗУ работает только в режимах хранения и считывания. Описать работу схем пункта 8.6. (Шило стр.161)

8.5 Репрограммируемые пзу, организация, работа.

Е сли

мд истоком и затвором подать импульс

U,

то происходит пробой. Часть ¯e

переходят в плавающий затвор и заряжают

его отрицательно.

сли

мд истоком и затвором подать импульс

U,

то происходит пробой. Часть ¯e

переходят в плавающий затвор и заряжают

его отрицательно.

В результате в подзатворной области меняется тип электропроводности и канал оказывается закрытым(это аналогично отсутствию диода) заряд хранится до 1000ч. Для того чтобы репродуктировать мд истоком и затвором подается импульс др.зарядности , значит происходит пробой→¯e уходят в подложку или исток.

8.6 Функциональные схемы ОЗУ и ПЗУ в интегральном исполнении. Примеры ЗУ в интегральном исполнении.

Примеры ОЗУ:К155РУ1, К155РУ3

ПЗУ: К155ПР6, К155ПР7

8.7 Методы увеличения емкости ЗУ.

Для увеличения емкости микросхемы подключаются параллельно. ВК- выбор кристалла.

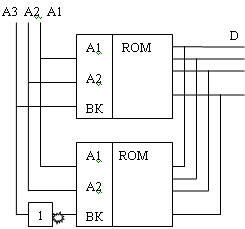

8.8 Программируемые логические матрицы (плм).

Программирование логической матрицы

Если дешифратор вкл по схеме «И», то ПП (пространство памяти) вкл по схеме «ИЛИ»

Т.к. имеется матрица реализующая функцию «и» и «или» то такая структура является универсальным устройством.

Мы можем запрограммировать матрицу дешифратора и получить необходимые нам коды, слова.

С помощью, которого можем выполнять любые логические функции.

8.9 Режимы программирования бис пзу.

БИС- большие интегральные схемы относятся к классу полузаказных микросхем высокой степени интеграции. Они могут проектироваться на основе базового матричного кристалла. Он представляет собой полупроводник. Кристалл на котором в определенном порядке размещены на определенных местах не скомутированные активные и пассивные элементы. Эти элементы объединены в блоки или топологические ячейки. Ячейки размещаются регулярно образуя матрицу повторяющихся ячеек.

Проектирование того или иного устройства состоит в следующем: сначала коммутируются ¯e внутри ячейки→ коммутируются выводы, дополнительные элементы. Коммутация состоит в нанесении металлизированного проводника.

8.10 Перспективные направления разработки ЗУ.

Новыми возможностями использования ПЗУ м.б.:

- возможность запрограммировать матрицу так чтобы на выходе был сигнал пилообразной формы.

- поскольку матрица может выполнять любые функции, то возможно построить элемент памяти.

8.11 Методы и средства диагностики и контроля цифровых устройств, в том числе ЗУ.

9.Генераторы электрических сигналов

9.1 Генераторы импульсных сигналов.

Генераторы электрических сигналов.

Генераторы импульсных сигналов.

Наиболее распространенные генераторы прямоугольных и линейно изменяющихся (пилообразных) импульсов напряжения.

Генераторы импульсных сигналов могут работать в одном в одном из трех режимов: автоколебательном, ждущем или синхронизации. В автоколебательном режиме генератор непрерывно формирует импульсные сигналы без внешнего воздействия. В ждущем режиме генератор формирует импульсный сигнал лишь по приходе внешнего (запускающего) сигнала. В режиме синхронизации генератор вырабатывает импульсы напряжения, частота которых равна или кратна частоте синхронизирующего сигнала.

Условия самовозбуждения автогенераторов.

Г енераторы

реализуются с помощью усилителей,

охваченных положительной ОС.

енераторы

реализуются с помощью усилителей,

охваченных положительной ОС.

![]()

При выполнении этих условий в усилителе возникают незатухающие колебания.

Амплитудная характеристика усилителя нелинейна, имеется участок насыщения, на котором Ku уменьшается. Наступает равновесие, когда Ku·β = 1. Устанавливается стационарное значение амплитуды.

Баланс фаз – фазовый сдвиг усилителя и цепи ОС равен нулю.

Если условия выполнябтся для одной частоты, то получим генератор колебаний синусоидальной формы, если для многих частот – то сложной формы.

М етод

стабилизации частоты генератора.

етод

стабилизации частоты генератора.

Для повышения высокой стабильности частоты вместо времязадающего конденсатора часто включают кварцевый резистор. При этом вследствие высокой добротности кварцевого резонатора форма импульсов отличается прямоугольной.

Мультивибраторы на интегральных логических элементах, интегральных таймерах и операционных усилителях. Состав, режим работы, эпюры напряжений.

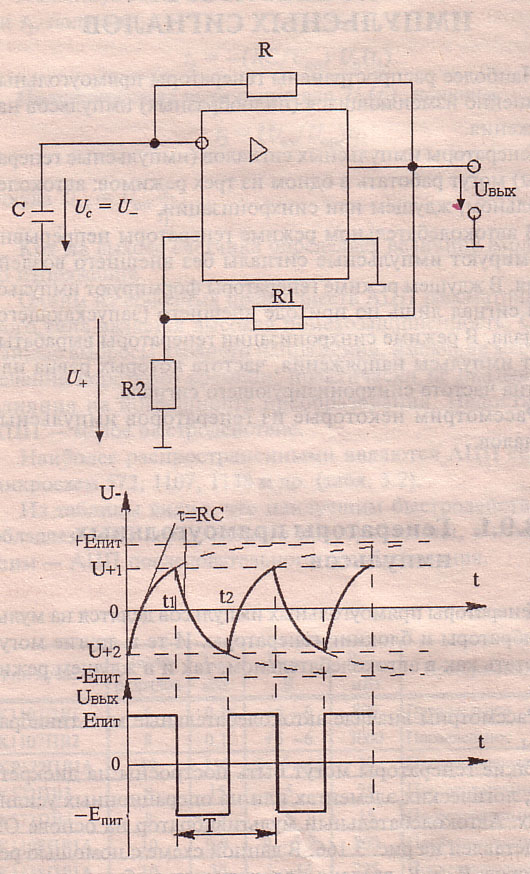

Мультивибратор на основе ОУ.

С помощью резисторов R1

и R2

введена положительная обратная связь

(ОС), что является необходимым условием

для возникновения в схеме электрических

колебаний. В зависимости от напряжений

на входе (которое может быть равно либо

+Епит, либо –Епит, где Епит – напряжение

питания ОУ) на инвертирующем входе ОУ

устанавливается или напряжение U+1,

или напряжение U+2.

помощью резисторов R1

и R2

введена положительная обратная связь

(ОС), что является необходимым условием

для возникновения в схеме электрических

колебаний. В зависимости от напряжений

на входе (которое может быть равно либо

+Епит, либо –Епит, где Епит – напряжение

питания ОУ) на инвертирующем входе ОУ

устанавливается или напряжение U+1,

или напряжение U+2.

Емкость С, входящая в цепь отрицательной ОС, перезаряжается с постоянной времени τ=RC.Напряжение Uc на емкости, равно напряжению U- на инвертирующем входе, стремится либо к уровню +Епит (при Uвых=+Епит) либо к уровню –Епит (при Uвых= - Епит). До момента времени t1 U+ - U-=U+1 – Uc>0, следовательно ОУ находится в режиме насыщения и на его выходе удерживается напряжение +Епит. Начиная с момента времени t1 эта разность меняет знак, что приводит к изменению напряжения на выходе ОУ на –Епит. После момента времени t1 емкость С перезаряжается, причем ее напряжение стремится к уровню –Епит. Очевидно, что до момента времени t2 U+ - U-=U+2 – Uc<0, что и удерживает выходное напряжение ОУ на уровне –Епит. Начиная с момента времени t2, эта разность вновь меняет знак, происходит изменение напряжения Uвых и т.д.Таки образом, данный мультивибратор формирует прямоугольные импульсы напряжения.

Период следования импульса определяется:

Т=2RCln(1+2*R1/R2)

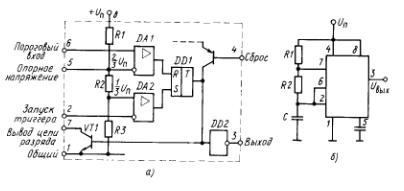

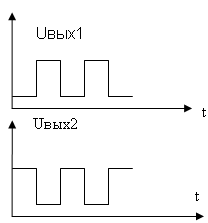

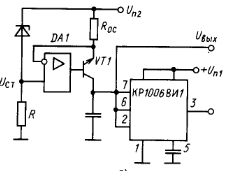

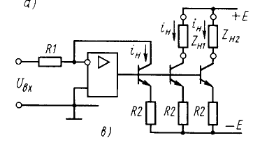

М ультивибратор

на интегральных таймерах. КР1006ВИ1

ультивибратор

на интегральных таймерах. КР1006ВИ1

(а)Ключ S выполнен на транзисторе VT1, на входе установлен дополнительный буферный элемент DD2, а роль источников опорных напряжений U1,U2 выполняет делитель напряжений на резисторах R1,R2,R3. Схема включения его мультивибратором на рис (б). Конденсатор С заряжается через резисторы R1,R2 , до напряжения U2=⅔Uп, а разряжается через резистор R1до напряжения U1=⅓Uп. Длительность стадий зарядки и разрядки (Т1 и Т2) конденсатора С , а так же частоту генерируемых импульсов можно рассчитать по формулам.

Т1≈0.693(R1+R2)C; T2≈0.693R2C; F=1/(T1+T2).

Cследует отметить, что минимальное значение Т2 ограничено параметрами ключа VT1.

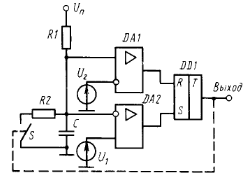

Процессы заряда и разряда хронирующей емкости. Работа мультивибраторов в автоколебательном и ждущем режимах, в режиме синхронизации и деления частоты.

Автоколебательный мультивибратор – это генератор, у которого нет устойчивого состояния.

Обратная связь здесь «+» и является широкополосной. Включим питание ТТЛ элемента 5В и наличие «+» о.с. приведет к тому, что первый элемент открыт, а второй закрыт. На выходе 1 высокий потенциал τз = R2C1.

Напряжение на С1↑, на R2 ↓. Напряжение на сопротивлении, т. е на вход DD2 станет < Uоп. В результате DD2 закрывается.

Э лемент

DD2 переключается и скачек напряжения

через С2 попадает на DD1 и элемент DD1

открывается. Емкость С2 начинает

заряжаться. На R1(+ -) удерживает. DD1 в

открытом состоянии. Емкость С1 разряжается

через выход открывается элемент DD1,

через общую шину, через сопротивление

R2 на «-» емкость. На R2 сформировалось

отрицательное напряжение, которое

закрывает DD2. Если R1=R2 и С1=С2, то получим

симметричное напряжение.

лемент

DD2 переключается и скачек напряжения

через С2 попадает на DD1 и элемент DD1

открывается. Емкость С2 начинает

заряжаться. На R1(+ -) удерживает. DD1 в

открытом состоянии. Емкость С1 разряжается

через выход открывается элемент DD1,

через общую шину, через сопротивление

R2 на «-» емкость. На R2 сформировалось

отрицательное напряжение, которое

закрывает DD2. Если R1=R2 и С1=С2, то получим

симметричное напряжение.

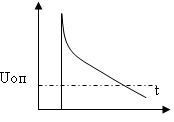

10. Генераторы линейно изменяющегося напряжения (глин) их характеристики и параметры.

Такие генераторы можно создать на основе автогенератора, если его конденсатор С заряжать не через резистор R, а через источник стабильного тока I=const, то напряжение на конденсаторе будет изменяться в соответствии с уравнением

![]()

Разряд конденсатора должен происходить за малый промежуток времени (время восстановления). Для этого резистор в схеме рисунка 1 следует замкнуть накоротко. На рисунке 2 приведена схема ГЛИН. В ней резистор R1 заменён на источник постоянного тока, выполненный на ОУ DA1 и транзисторе VT1 по схеме рис 3 а резистор R2 взят равным нулю.

рис1 рис2

рис3

Для

нормальной работы источника постоянного

тока необходимо, чтобы Ucт

было больше

![]() на 1,5 –2 В. Это требование вызвано тем,

что для нормальной работы источника

постоянного тока транзистор VT1

должен находиться в активном режиме.

на 1,5 –2 В. Это требование вызвано тем,

что для нормальной работы источника

постоянного тока транзистор VT1

должен находиться в активном режиме.

ГЛИН

обычно характеризуется следующими

параметрами: начальным уровнем выходного

напряжения

![]() ;

размахом(величиной) ЛИН

;

размахом(величиной) ЛИН

![]() ;

длительностью рабочего хода

;

длительностью рабочего хода

![]() ;

длительностью обратного хода или

временем восстановления

;

длительностью обратного хода или

временем восстановления

![]() ;периодом

повторения импульсов

;периодом

повторения импульсов

![]() ;

скоростью рабочего хода

;

скоростью рабочего хода

![]() и средней скоростью рабочего хода

и средней скоростью рабочего хода

![]() ;

коэффицентом нелинейности

;

коэффицентом нелинейности

![]() ,

где

,

где

![]() и

и

![]() значения скорости в начале и конце

рабочего хода; коэффициентом использования

напряжения питания

значения скорости в начале и конце

рабочего хода; коэффициентом использования

напряжения питания

![]() .

В зависимости от целевого назначения

ГЛИН обычно получают следующие параметры

выходного напряжения: Тр несколько

мкс-десятки с;

.

В зависимости от целевого назначения

ГЛИН обычно получают следующие параметры

выходного напряжения: Тр несколько

мкс-десятки с;![]() 0,01 до 10%.

0,01 до 10%.

ГЛИН с токостабилизирующим элементом в зарядно-разрядной цепи.

1. Когда разрядная цепь закрыта, то формируется возрастающее напряжение, С заряжается; под воздействием Uу открывается разрядная цепь и С разряжется через неё.

2. Подается Uу, коммутирующая цепь открывается, емкость быстро заряжается до напряжения Е, разряжается через разрядную цепь.

![]()

Чтобы получить хорошую линейность длин, надо заряжать конденсатор постоянным током. Зарядная цепь болжна представлять собой источник тока или генератор стабильного тока.

М етоды

повышения линейности формируемого

напряжения.

етоды

повышения линейности формируемого

напряжения.

В

цепи заряда вместо резистора Rк

используют ГСТ. Ёмкость заряжается

постоянным током, и напряжение возрастает

линейно. Напряжение на базе V1

застабилизировано, V1

включен по схеме «общая база».

цепи заряда вместо резистора Rк

используют ГСТ. Ёмкость заряжается

постоянным током, и напряжение возрастает

линейно. Напряжение на базе V1

застабилизировано, V1

включен по схеме «общая база».Применение следящей ОС по напряжению или току.

Применение ёмкостной ОС.

Применение микросхем-таймеров.

Генераторы функций.

Ф ормирование

функций, в том числе линейно изменяющегося

напряжения, возможно на основе

преобразования ступенчатых функций

φ(t)

на интервале [t0,

…, tn-1],

таком чтобы |φ(t)-φk(t)|≤δ.

ормирование

функций, в том числе линейно изменяющегося

напряжения, возможно на основе

преобразования ступенчатых функций

φ(t)

на интервале [t0,

…, tn-1],

таком чтобы |φ(t)-φk(t)|≤δ.

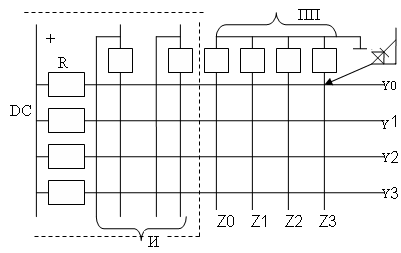

Н а

схеме: ГТИ – генератор тактовых импульсов,

СЧ – счётчик, DC

– дешифратор, ЦАП – цифро-аналоговый

преобразователь, ФНЧ – фильтр низких

частот.

а

схеме: ГТИ – генератор тактовых импульсов,

СЧ – счётчик, DC

– дешифратор, ЦАП – цифро-аналоговый

преобразователь, ФНЧ – фильтр низких

частот.