- •15.Двоичная и десятичная системы счисления. Перевод из одной системы в другую. Задание фал с помощью десятичных чисел.

- •3. Способы задания фал. Таблица истинности. Геометрическая интерпретация. Задание с помощью десятичных чисел. Задание с помощью формул.

- •6. Аксиомы алгебры логики. Закон нулевого и единичного множества, повторения, двойного отрицания, логического нуля и логической единицы.

- •7. Аксиомы алгебры логики. Переместительный, сочетательный и распределительный законы. Закон упрощения. Формулы де Моргана.

- •8. Стандартные формы фал.

- •21 .Минимизация фал с помощью карт Карно.

- •30. Особенные классы фал. Функции, сохраняющие константу 0 и 1. Линейные, монотонные, самодвойственные функции.

- •11. Теоремы о том, что функция Вебба и Шеффера образуют базис.

- •9. Понятие о функционально полных системах фал. Минимальные функционально-полные системы. Доказательство того, что системы (и, или, не}, {или, не}, (и, не} образуют базис.

- •Понятие о дискретном элементе и ду. Примеры дискретных элементов. Классификация релейных устройств

- •Общее число фал от п переменных. Фал от одной переменной.

- •Фал от двух переменных.

- •10. Понятие о суперпозиции фал. Представление фал в базисах {или, не} и {и, не}.

- •22. Анализ многотактных схем. Понятие о внутреннем состоянии и о полном состоянии схемы. .Составление таблиц переходов и выходов. Закон работы многотактной схемы.

- •24. Составление таблиц переходов по временной диаграмме. Минимизация таблицы переходов.

- •25. Состязания в многотактных схемах. Понятие о критических и некритических состязаниях.

- •26. Исключение критических состязаний за счет введения задержек и путем преобразования таблицы переходов.

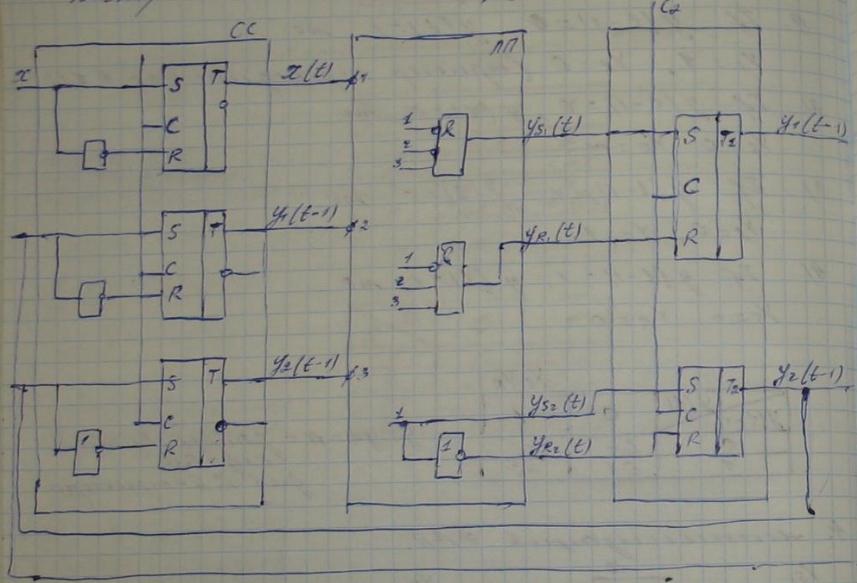

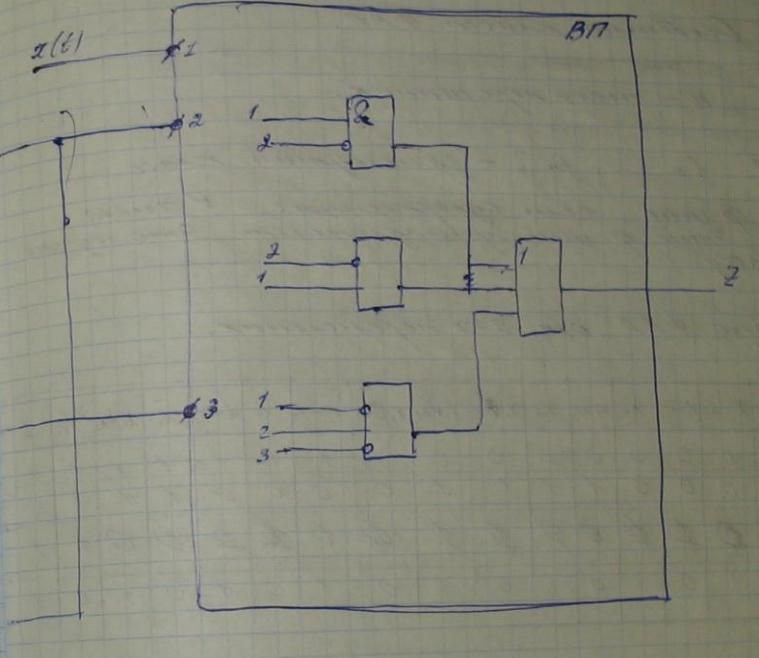

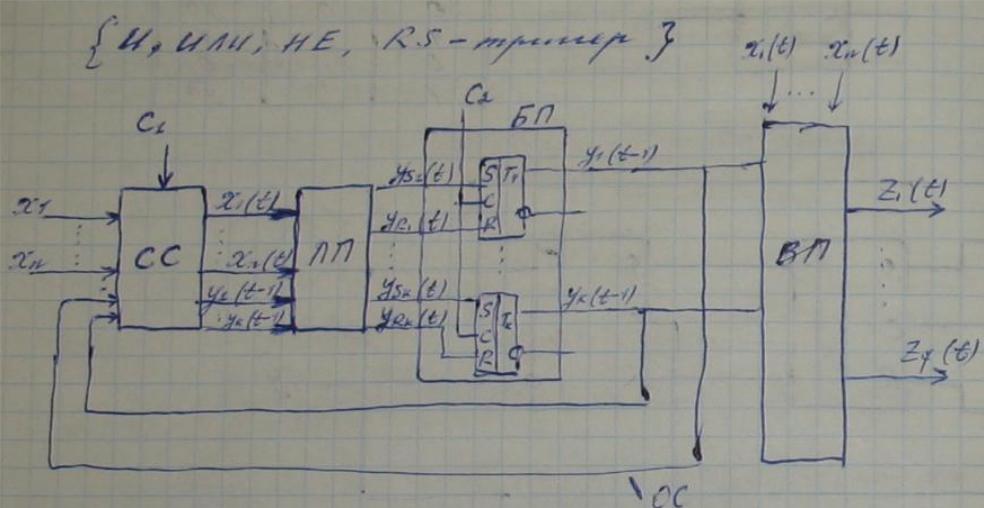

- •29. Синтез синхронного автомата на rs - триггерах по заданным таблицам переходов и выходов.

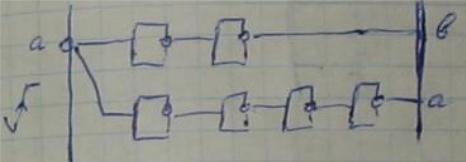

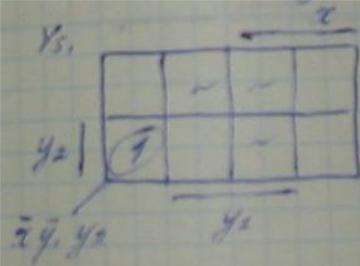

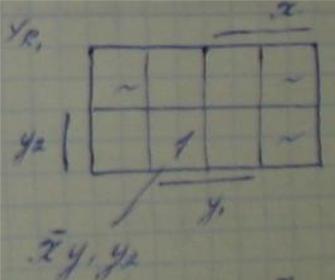

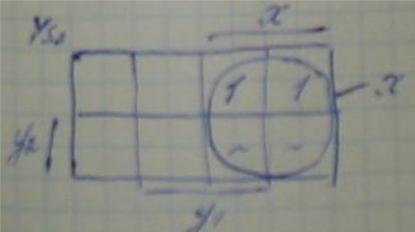

29. Синтез синхронного автомата на rs - триггерах по заданным таблицам переходов и выходов.

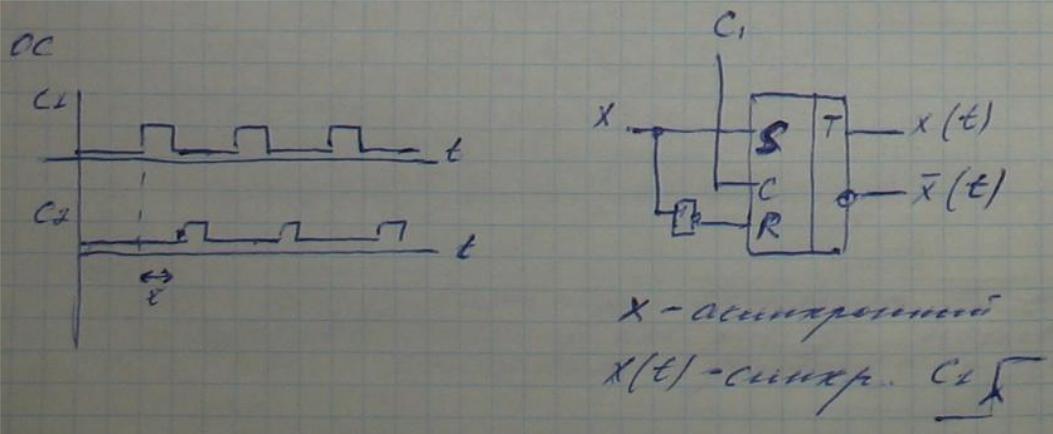

БП-блок питания, ЛП-логичный преобразователь, вычисляет ф-ции ys, yr, ВП-выходной преобразователь, вычисляет ф-цию z(t); СС – схема синхронизации.

Дискретное время

![]()

В течение ∆t входные сигналы неизменны, все переходные процессы заканчиваются. ЛП: у3, уr вычисляются.

с 2=0,

τ>t,

t-время

по самому длинному пути ЛП.

2=0,

τ>t,

t-время

по самому длинному пути ЛП.

С2=1. сигналы на выходе на ЛП установятся. БП у1(t-1) …yk(t-1) – сигналы появляются неодновременно. С1=0 τ>tm, t – время переключения самого медленного триггера.

Алгоритм синтеза синхронных схем.

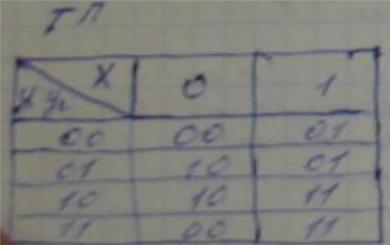

1. осуществляется кодирование строк (произвольное)

У1 у2

1-00 2-01

3-10 4-11

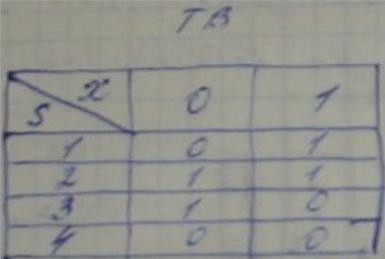

2. составляются кодирование ТП и ТВ

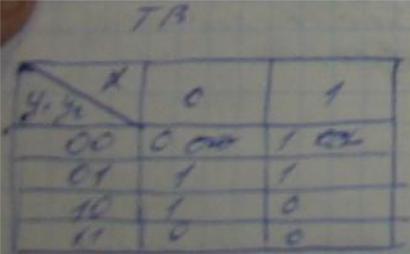

составляется таблица истинности

![]()

Мимизация ФАЛ

Построение схемы по функции