- •Микропроцессоры: определение, назначение, основные понятия: мп, мпс, мк и др.

- •Классификация мп

- •Основные параметры мп

- •Системы эвм

- •5 Обобщенная структурная схема мп

- •6 Типичный машинный цикл

- •7 Пути обработки командного и информационного слова

- •8 Архитектура процессоров. Принстонская и гарвардская архитектуры.

- •10 Система команд мп: операции над числами с ф.З. И Пл.З. Условные и безусловные переходы, циклы и др.

- •11 Форматы команд и способы адресации.

- •12 Организация подсистемы прерываний мпс. Классы прерываний. Структурная схема системы. Приоритеты прерываний.

- •13 Контроллер прерываний кр580вн59: схема, режим работы.

- •14 Семейства бис кр580; фирмы Intel

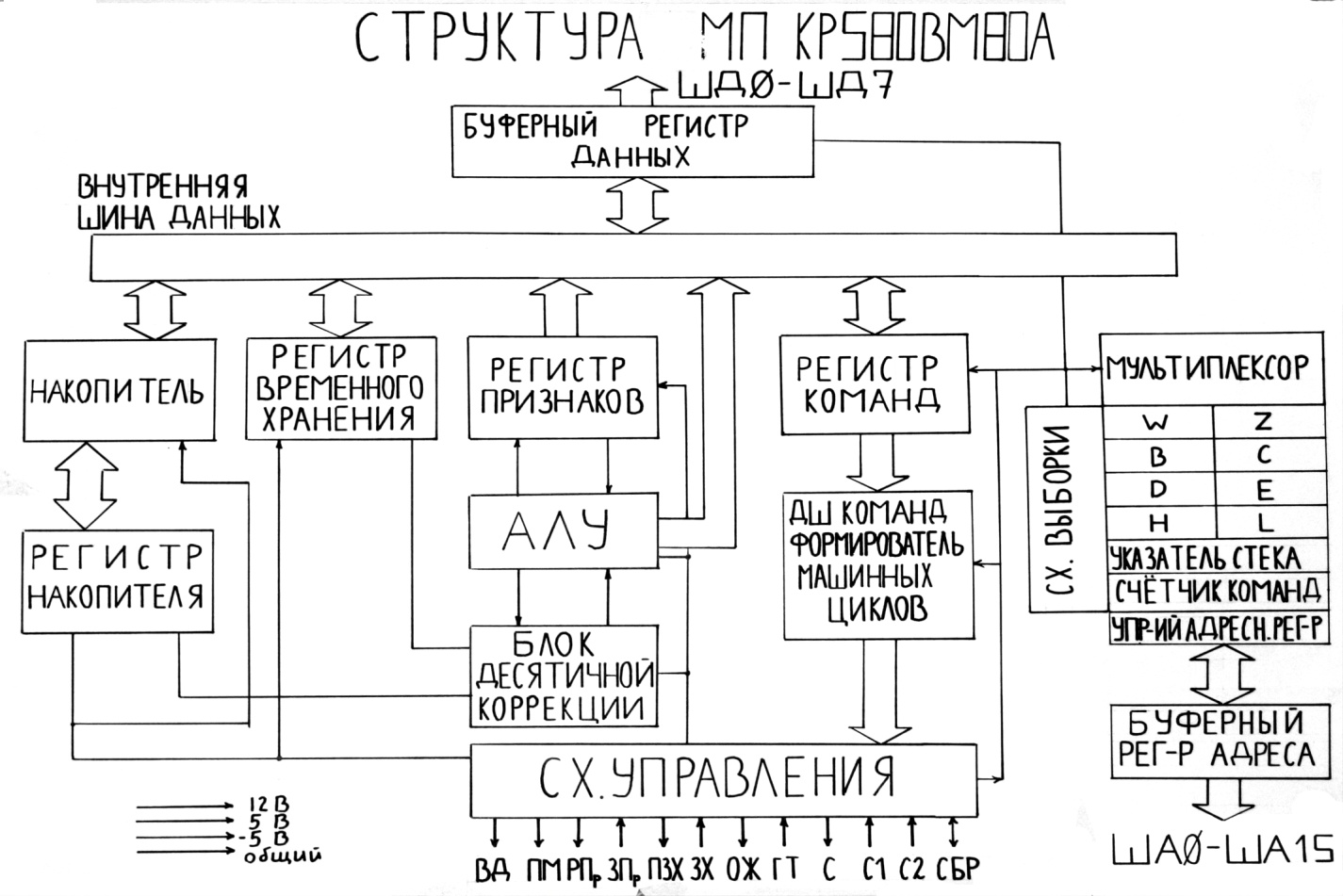

- •15 Микропроцессор кр580вм80а: принципы функционирования, уго, структурная схема.

- •16 Микропроцессор кр580вм80а: уго, схема временные диаграммы командного цикла.

- •17 Микропроцессор бис кр580вм8а уго, схема вд цикла прерываний

- •18 Микропроцессор бис кр580вм8а уго, схема, вд ввода/вывода

- •19 Параллельный интерфейс бис кр580вв55, уго, схема, режимы работы.

- •2 0 Последовательный интерфейс бис кр580вв51.

- •21 Организация режима прямого доступа в память (пдп). Контроллер пдп кр580вт57, уго, схема, режимы работы.

- •22 Организация службы времени. Программируемый таймер кр580ви53. Уго, схема, режимы работы.

- •23 Контроллер видеотерминала кр580вг75: уго структурная схема принцип действия.

- •24 Схема включения контроллера бис кр580вг75 в мпс.

- •25 Особенности архитектуры мп 80486: структурная схема, вд работы. Режимы работы: реальный, защищенный.

- •26 Особенности архитектуры мп Pentium: структурная схема, вд работы.

- •27 Семейство микро-эвм, ключевые мс пк imb pc и совместимые с ними.

- •28 Микроконтроллеры: определение, назначение, структурная схема технологической системы управления.

- •29 Архитектура мк cisk, risk.

- •30 Типы мкс.

- •31 Типовая структура мк

- •32 Функциональная схема мк

- •33 Цпу мк. Архитектура цпу.

- •34 Организация памяти мк.

- •35 Параллельные порты ввода-вывода мк.

- •36 Последовательные порты ввода-вывода мк.

- •37 Функциональная схема ацп мк sasb 80c515

- •38. Блок таймеров и поддержка режима «реального времени».

- •39. Сторожевой таймер.

- •40. Эволюция архитектуры мк: 4-х, 8-и, 16-и, 32-х, 64-х – разрядные мк.

- •41. Интегрированная среда разработки по (ис рпо) для семейства мк avr.

- •42. Программирование мк на языке Ассемблер: процедуры, подпрограммы, директивы.

- •43. Интерфейс встраиваемых мпс: физический и логический. Шины pci, vmEи др.

- •44. Шина usb: характеристики, топология, режимы работы.

- •45. Jtag – интерфейс системные функции на его основе.

- •46. Программируемые логические матрицы и плис.

- •47. Вычислительные системы: определение, назначение, классификация.

- •48. Многопроцессорные вс. Структурная схема.

- •49. Многомашинные вс. Вс с коммутационной матрицей, структурные схемы.

- •50.Проектирование мпс. Средства и методы комплексной отладки мпс.

14 Семейства бис кр580; фирмы Intel

14 Семейства БИС% МПК серии КР580; фирмы Intel (про интел видимо бред…)

МПК БИС серии кр580 предназначен для построения 8-разрядных контроллеров, микро-ЭВМ и МПС разного назначения.

Функциональная законченность МПК, относительная простота разработки МПС на его основе, достаточно высокое быстродействие, относительно низкая потребляемая мощность обуславливают возможность его широкого применения в различных областях. МПК выполнен по n-МОП технологии. Уровни сигналов соответствуют уровням распространенных серий.

Кроме того, с ним совестимы серии ИМС К589, выполненные по ТТЛШ технологии.

состав серии

кр58вм80а - микропроцессор, частота 2,5 МГц. +5, -5, +12 В

кр58вв51 - последовательный интерфейс. 2 МГц, 5В

кр58вв55 параллельный интерфейс 2МГЦ, 5 В

кр58ви53 программируемый таймер 2МГц, 5В

кр58вт57 программируемый контроллер ПДП 2МГц, 5В

кр58вн 59 программируемый контроллер прерываний 2МГц, 5В

кр580вг75 программируемый контроллер ЭЛТ 3МГц, 5В

15 Микропроцессор кр580вм80а: принципы функционирования, уго, структурная схема.

В

осьмиразрядный

однокристальный МП КР580ВМ8А с фиксированной

системой команд предназначен для

построения средств обработки данных,

применяемых в контроллерах, микро-ЭВМ,

устройствах цифровой автоматики и тд.

Он помещен в пластиковом корпусе с 40

выводами. Потребляемая мощность 750мВт.

частота 2,5МГцМП имеет 8-разрядную ШД.

Обмен информацией между внутренней ШД

и ШД МПС осуществляется через буферный

регистр данных. 16-разрядная ША позволяет

МП-ру осуществлять непосредственную

адресацию до 64 кб памяти. Буферные

регистры адресов и данных имеют выходы

с тремя состояниями, что позволяет их

отключать и реализовать ПДП. 8-разрядное

АЛУ позволяет осуществлять операции

над данными, представленными в двоичной

или двоично-десятичной форме, и

находящимися в регистре накопителя или

регистре временного хранения. Результат

выполнения операции поступает по

внутренней ШД или записывается в

накопитель. Блок десятичной коррекции

позволяет при необходимости корректировать

тетрады результата, из которых не возник

перенос.

осьмиразрядный

однокристальный МП КР580ВМ8А с фиксированной

системой команд предназначен для

построения средств обработки данных,

применяемых в контроллерах, микро-ЭВМ,

устройствах цифровой автоматики и тд.

Он помещен в пластиковом корпусе с 40

выводами. Потребляемая мощность 750мВт.

частота 2,5МГцМП имеет 8-разрядную ШД.

Обмен информацией между внутренней ШД

и ШД МПС осуществляется через буферный

регистр данных. 16-разрядная ША позволяет

МП-ру осуществлять непосредственную

адресацию до 64 кб памяти. Буферные

регистры адресов и данных имеют выходы

с тремя состояниями, что позволяет их

отключать и реализовать ПДП. 8-разрядное

АЛУ позволяет осуществлять операции

над данными, представленными в двоичной

или двоично-десятичной форме, и

находящимися в регистре накопителя или

регистре временного хранения. Результат

выполнения операции поступает по

внутренней ШД или записывается в

накопитель. Блок десятичной коррекции

позволяет при необходимости корректировать

тетрады результата, из которых не возник

перенос.

В схеме имеется регистр признаков, в который заносится информация о результате выполнения команды. Z устанавливается в 1 при нулевом результате, C - перенос, s - единичное значение старшего разряда результата, AC - дополнительный перенос из младшей тетрады в старшую, p - четность (четное число единичных битов)

Блок регистров МП включает 8 8-разрядных РОНов . 6 из них b,c,d,e,h,l используются как самостоятельные регистры, либо как регистровые пары, а w,z программно не доступны и используются для хранения промежуточных результатов при выполнении команд.

Управляемый адресный регистр служит для адресации и может ин-/декрементировать передаваемую информацию, что упрощает адресацию.

Также в блок регистров МП входят16-разрядный УС и 16-разр СК

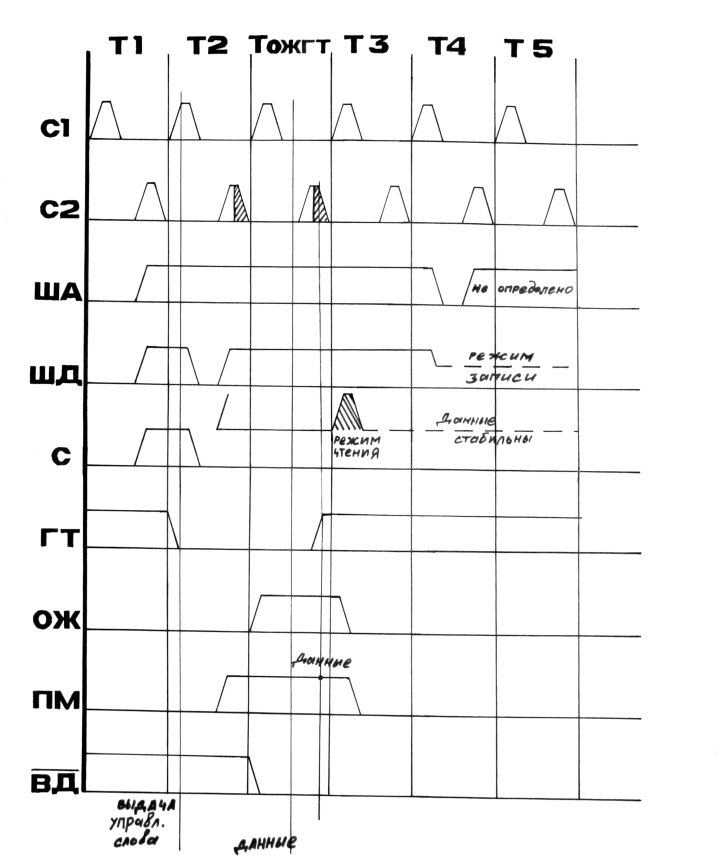

16 Микропроцессор кр580вм80а: уго, схема временные диаграммы командного цикла.

УГО и схема в ответе №15

Машинный (командный) цикл МП включает 3-5 тактов и соответствует чтению или записи в ВУ/ЗУ одного байта информации.

длина команд 1-3 байт.

При выполнении команды в первом такте Т1 содержимое СК выдается на ША и в этом же такте МП выдает на ШД 8-разрядное управляющее слово и формирует спец сигнал С, по которому оно записывается в буферный регистр внешней схемы управления и указывает тип машинного цикла.

В Т2 СК увеличивается на 1 и осуществляется анализ управляющих сигналов, в зависимости от них происходит переход к Т3 или в одно из состояний ожидания, выход из которого возможен только при поступлении внешних управляющих сигналов.

В Т3 данные принимаются из ЗУ/ВУ и записываются в РК или в один из свободных регистров МП (в РОНы)

в тактах 4 и 5 команда выполняется

в последнем такте последнего цикла команды, а также в состоянии Тож проверяется уровень сигнала на входе ЗПР. при высоком уровне и установленном ранее триггере РПР, МП по тактовому импульсу С устанавливает внутренние триггеры прерывания и обслуживает прерывание.