- •Микропроцессоры: определение, назначение, основные понятия: мп, мпс, мк и др.

- •Классификация мп

- •Основные параметры мп

- •Системы эвм

- •5 Обобщенная структурная схема мп

- •6 Типичный машинный цикл

- •7 Пути обработки командного и информационного слова

- •8 Архитектура процессоров. Принстонская и гарвардская архитектуры.

- •10 Система команд мп: операции над числами с ф.З. И Пл.З. Условные и безусловные переходы, циклы и др.

- •11 Форматы команд и способы адресации.

- •12 Организация подсистемы прерываний мпс. Классы прерываний. Структурная схема системы. Приоритеты прерываний.

- •13 Контроллер прерываний кр580вн59: схема, режим работы.

- •14 Семейства бис кр580; фирмы Intel

- •15 Микропроцессор кр580вм80а: принципы функционирования, уго, структурная схема.

- •16 Микропроцессор кр580вм80а: уго, схема временные диаграммы командного цикла.

- •17 Микропроцессор бис кр580вм8а уго, схема вд цикла прерываний

- •18 Микропроцессор бис кр580вм8а уго, схема, вд ввода/вывода

- •19 Параллельный интерфейс бис кр580вв55, уго, схема, режимы работы.

- •2 0 Последовательный интерфейс бис кр580вв51.

- •21 Организация режима прямого доступа в память (пдп). Контроллер пдп кр580вт57, уго, схема, режимы работы.

- •22 Организация службы времени. Программируемый таймер кр580ви53. Уго, схема, режимы работы.

- •23 Контроллер видеотерминала кр580вг75: уго структурная схема принцип действия.

- •24 Схема включения контроллера бис кр580вг75 в мпс.

- •25 Особенности архитектуры мп 80486: структурная схема, вд работы. Режимы работы: реальный, защищенный.

- •26 Особенности архитектуры мп Pentium: структурная схема, вд работы.

- •27 Семейство микро-эвм, ключевые мс пк imb pc и совместимые с ними.

- •28 Микроконтроллеры: определение, назначение, структурная схема технологической системы управления.

- •29 Архитектура мк cisk, risk.

- •30 Типы мкс.

- •31 Типовая структура мк

- •32 Функциональная схема мк

- •33 Цпу мк. Архитектура цпу.

- •34 Организация памяти мк.

- •35 Параллельные порты ввода-вывода мк.

- •36 Последовательные порты ввода-вывода мк.

- •37 Функциональная схема ацп мк sasb 80c515

- •38. Блок таймеров и поддержка режима «реального времени».

- •39. Сторожевой таймер.

- •40. Эволюция архитектуры мк: 4-х, 8-и, 16-и, 32-х, 64-х – разрядные мк.

- •41. Интегрированная среда разработки по (ис рпо) для семейства мк avr.

- •42. Программирование мк на языке Ассемблер: процедуры, подпрограммы, директивы.

- •43. Интерфейс встраиваемых мпс: физический и логический. Шины pci, vmEи др.

- •44. Шина usb: характеристики, топология, режимы работы.

- •45. Jtag – интерфейс системные функции на его основе.

- •46. Программируемые логические матрицы и плис.

- •47. Вычислительные системы: определение, назначение, классификация.

- •48. Многопроцессорные вс. Структурная схема.

- •49. Многомашинные вс. Вс с коммутационной матрицей, структурные схемы.

- •50.Проектирование мпс. Средства и методы комплексной отладки мпс.

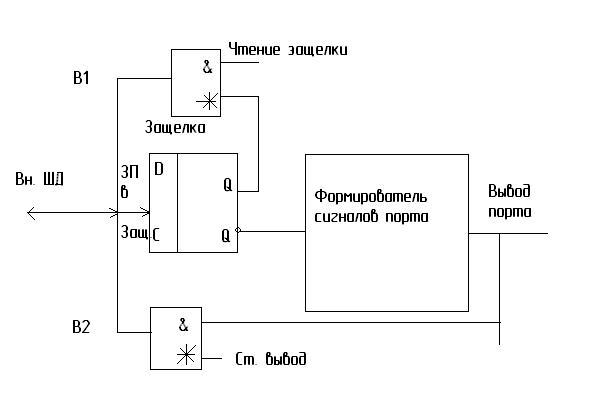

35 Параллельные порты ввода-вывода мк.

Порты ввода вывода/вывода параллельной информации.

Для связи МК с объектом управления ( с датчиками и ИУ) в структуре МК имеются специальные средства обеспечивающие ввод – вывод как дискретных так и аналоговых сигналов

В МК отдельные линии ввода-вывода дискретных сигналов объединяются в параллельные n разрядные порты ( обычно 8) которые позволяют непосредственно вводить и выводить из МК данные в виде параллельного цифрового кода. ПП являются двунаправленными

Каждый из разрядов порта ввода вывода состоит из триггера-защелки и вентилей В1, В2 реализованных на схемах «И» , формирователя выхода порта и входного буфера В2. запись данных в триггер защелку осуществляется под управлением внутреннего сигнала запись в защелку. При выполнении команд, в которых порт является приемником.

При выводе данные внутренней шины записываються в триггер защелку порта и из него поступают на внешние выводы. Выход триггера Q через вентиль В1 может быть подключен к внутренней шине с помощью внутреннего сигнала чтение защелки. Благодаря такой организации разряда порта обеспечивается программное чтение защелки, и возможность побитовой обработки сигналов порта с последующей записью результата обратно в защелку. При вводе данных работу порта поддерживает вентиль В2 управляемый внутренним сигналом «чтение вывода» данные с внешнего контакта порта при поступлении сигнала чтения вывода через вентиль В2 поступают на вн. Шину МК и далее обрабатываются ЦПУ.

Все порты МК являются двунаправленными, важной особенностью которых является возможность программирования отдельных линий.

36 Последовательные порты ввода-вывода мк.

Последовательные порты

Обмен данными между МК и удаленными датчиками, используемыми исполнительным устройством часто осуществляется по последовательным каналам, встроенных в архитектуру МК последовательных портов.

Обычно в МК встраивается универсальный асинхронный последовательный приемо-передатчик UART поддерживающий протокол RS232c кроме того используются RS485, rs422a и другие. Важным назначением последовательного порта является не только обеспечение связи с удаленными датчиками и но и организация связи с другими ВМ. Мощные МК содержат несколько последовательных портов.

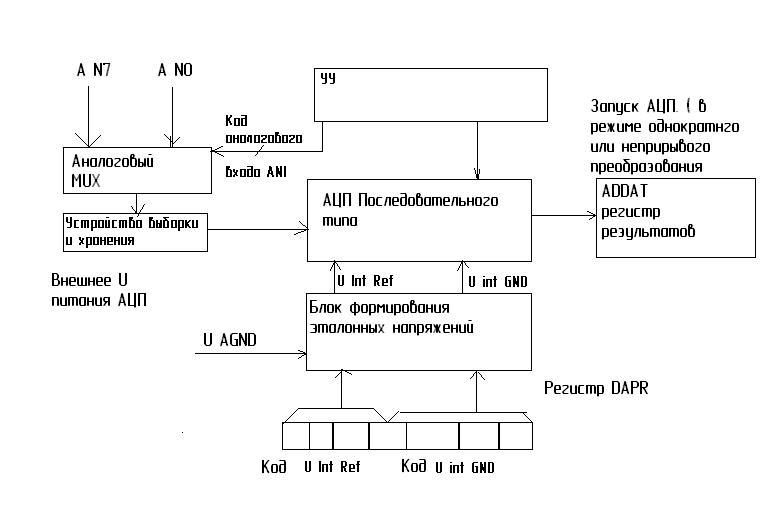

37 Функциональная схема ацп мк sasb 80c515

Размещается на кристалле МК. Встроенные средства обеспечивают связь МК с аналоговыми датчиками и ИУ объекта управления, с их помощью входные аналоговые сигналы от датчиков преобразуются в цифровой код для последующей обработки процесса. А так же проводится формирование аналоговых управляющих воздействий. Для преобразования аналоговых сигналов в цифровой код используется АЦП В схеме МК содержится 8-разрядный АЦП который обеспечивает преобразование аналоговых сигналов в диапазоне от 0 до 5,12В в цифровой 8 или 10 разрядный код Запуск преобразования может производится программно или аппаратно. На рисунке представлена схема АЦП последовательного приближения. Встроено в МК SAB 80C515. Схема состоит из 8-канального аналогового мультиплексора, устройства выборки и

хранения входного аналогового сигнала, собственно аналогового преобразователя последовательного приближения, блока формирования внутренних опорных напряжений и устройство управления. Аналоговый мультиплексор позволяет использовать АЦП для преобразования аналогового сигналов от несколько датчиков. Устройство выборки и хранения формирует из непрерывного меняющегося аналогового сигнала Ut последовательность отдельных цифровых сигналов Un, n - кол - во дискретов, которые с помощью АЦП преобразуется в цифровой код. Блок формирования эталонных напряжений. Используется для задания опорных напряжений сравнения. Для преобразования аналогового сигнала в цифровой код, чаще всего используется АЦП реализующее метод поразрядного уравновешивания называемого методом последовательного приближения.

В соответствии с этим методом осуществляется последовательное сравнение входного аналогового сигнала с целым рядом формирующих эталонных напряжений, и выбирается такое напряжение которое близко к значению входного сигнала, результат цифрового аналогового цифрового преобразователя фиксируется в регистре результата. Формирование эталонных напряжений и реализуется с помощью внутреннего ЦАП,

который преобразует цифровой n-разрядный код на выходе регистра результата в эталонный аналоговый сигнал. Уравновешивание начинается со старшего разряда регистра результата. Для управления АЦП используется регистр DAPR он предназначен для задания внутренних опорных напряжений используемых для формирования эталонного сравнения для каждого диапазона входных сигналов. Для управления АЦП используется трехбитный код аналогового входа подключенного через мультиплексор в устройствах выборки и хранения и один бит ADM с помощью которого программируется режим работы АЦП, при ADM = 0 задается режим одиночного преобразователя. При ADM = 1 преобразователь переводится в режим непрерывного преобразования, то есть автоматически по завершении очередного преобразования выполняется следующая. Повышение точности преобразования достигается за счет увеличения времени преобразования и выполняется в два последовательных цикла. В первом цикле

производится грубое измерение входного сигнала и формируется восьмибитный результат. При загрузке режима DAPR результатом грубого измерения инициируется повторное преобразование, сравнения с опорным значением, благодаря этому формируется более менее ступени сравнения, происходит более точное измерение, формируется 16-разрядный результат