- •Микропроцессоры: определение, назначение, основные понятия: мп, мпс, мк и др.

- •Классификация мп

- •Основные параметры мп

- •Системы эвм

- •5 Обобщенная структурная схема мп

- •6 Типичный машинный цикл

- •7 Пути обработки командного и информационного слова

- •8 Архитектура процессоров. Принстонская и гарвардская архитектуры.

- •10 Система команд мп: операции над числами с ф.З. И Пл.З. Условные и безусловные переходы, циклы и др.

- •11 Форматы команд и способы адресации.

- •12 Организация подсистемы прерываний мпс. Классы прерываний. Структурная схема системы. Приоритеты прерываний.

- •13 Контроллер прерываний кр580вн59: схема, режим работы.

- •14 Семейства бис кр580; фирмы Intel

- •15 Микропроцессор кр580вм80а: принципы функционирования, уго, структурная схема.

- •16 Микропроцессор кр580вм80а: уго, схема временные диаграммы командного цикла.

- •17 Микропроцессор бис кр580вм8а уго, схема вд цикла прерываний

- •18 Микропроцессор бис кр580вм8а уго, схема, вд ввода/вывода

- •19 Параллельный интерфейс бис кр580вв55, уго, схема, режимы работы.

- •2 0 Последовательный интерфейс бис кр580вв51.

- •21 Организация режима прямого доступа в память (пдп). Контроллер пдп кр580вт57, уго, схема, режимы работы.

- •22 Организация службы времени. Программируемый таймер кр580ви53. Уго, схема, режимы работы.

- •23 Контроллер видеотерминала кр580вг75: уго структурная схема принцип действия.

- •24 Схема включения контроллера бис кр580вг75 в мпс.

- •25 Особенности архитектуры мп 80486: структурная схема, вд работы. Режимы работы: реальный, защищенный.

- •26 Особенности архитектуры мп Pentium: структурная схема, вд работы.

- •27 Семейство микро-эвм, ключевые мс пк imb pc и совместимые с ними.

- •28 Микроконтроллеры: определение, назначение, структурная схема технологической системы управления.

- •29 Архитектура мк cisk, risk.

- •30 Типы мкс.

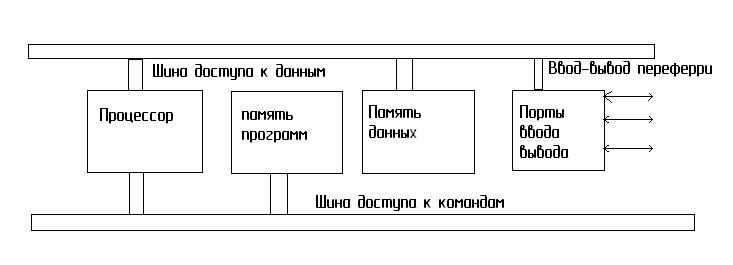

- •31 Типовая структура мк

- •32 Функциональная схема мк

- •33 Цпу мк. Архитектура цпу.

- •34 Организация памяти мк.

- •35 Параллельные порты ввода-вывода мк.

- •36 Последовательные порты ввода-вывода мк.

- •37 Функциональная схема ацп мк sasb 80c515

- •38. Блок таймеров и поддержка режима «реального времени».

- •39. Сторожевой таймер.

- •40. Эволюция архитектуры мк: 4-х, 8-и, 16-и, 32-х, 64-х – разрядные мк.

- •41. Интегрированная среда разработки по (ис рпо) для семейства мк avr.

- •42. Программирование мк на языке Ассемблер: процедуры, подпрограммы, директивы.

- •43. Интерфейс встраиваемых мпс: физический и логический. Шины pci, vmEи др.

- •44. Шина usb: характеристики, топология, режимы работы.

- •45. Jtag – интерфейс системные функции на его основе.

- •46. Программируемые логические матрицы и плис.

- •47. Вычислительные системы: определение, назначение, классификация.

- •48. Многопроцессорные вс. Структурная схема.

- •49. Многомашинные вс. Вс с коммутационной матрицей, структурные схемы.

- •50.Проектирование мпс. Средства и методы комплексной отладки мпс.

33 Цпу мк. Архитектура цпу.

ЦПУ современных МК представляет собой N-разрядный МП с фиксированной разрядностью и списком выполняемых команд.

В настоящее время наибольшая доля мирового рынка МК принадлежит 8-ми разрядным устройствам ( около 50% в денежном выражении ). За ними следуют 16-ти разрядные и цифровые сигнальные процессоры (DSP) каждая из них занимает приблизительно 20% рынка. DSP ориентированы на использование в системах цифровой обработки сигналов. Оставшиеся 10% остальные типы МК.

Основой ЦПУ является операционный блок, включающий АЛУ и регистровый файл. (ОЗУМК)взаимодействие отдельных блоков МК как внутри ЦПУ так и с блоками внутренней периферии осуществляется по внутренней шине МК. Связь МК с внешними устройствами реализуется через внешние выводы параллельных и последовательных портов.

При реализации современных МК используется весь спектр архитектурных решений, реализованных в МП. Ранние модели МК, широко применяемые в настоящее время, содержат одноадресный процессор с регистром-аккумулятором. В таком процессоре один из исходных операндов арифметических и логический операций по умолчанию размещается в аккумуляторе. И в него же помещается результат. Второй операнд адрес, которого указывается в команде содержаться в одном из регистров регистрового файла.

На основе одноадресной аккумуляторной архитектуры реализуются сильно распространенные 8ми разрядные МК семейства MCS-51 и других семейств.

Достоинства аккумуляторной архитектуры.

простота структуры

позволяет сократить формат команд ( уменьшение времени выборки)

НЕДОСТАТКИ

Снижена производительность

Более производительными являются многоадресное ЦПУ ( 2, 3 адреса) в которых оба операнда и результат могут размещать в любой ячейке интегрированного в кристалл регистрового файла.

Архитектуру ЦПУ МК подобного типа регистр-регистр или много аккумуляторная архитектура. Требует более сложного формата команд и имеет следующие преимущества: отсутствие необходимости предварительной загрузки одного из операндов в аккумулятор перед выполнением операции. При этом резко уменьшается операций по пересылке данных и возрастает скорость вычислений появляется возможность расширения системы команд высокопроизводительными 3-х операндными командами

В целом ЦПУ различных типов МК характризуються широким диапазоном производительности и зависящей от нее стоимости. Внутренняя память данных МК представлена в виде RАМ объем зависит от типа МК. И может различаться не только в разных семействах но даже в разных моделях МК одного семейства. Например 256 байт в МК семейства MCS51 и 232-1000 байт в MCS96.

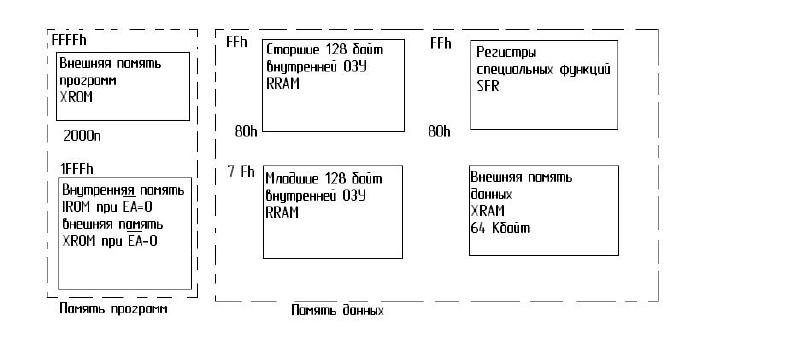

34 Организация памяти мк.

Особенности организации памяти МК

Отличительной архитектурной особенностью МК является то, что в них для хранения команд и данных используются разделенные физически, а часто и логически блоки памяти. Это обусловлено тем, что поскольку программы МК после отладки обычно не меняются, их размещают в ПЗУ. В отличие от команд переменные в ходе выполнения программы могут меняться, поэтому для их размещения используют ОЗУ. Архитектура ВМ, в которых программы и данные храниться в разделенных областях памяти, получила гарвардской архитектуры.

Полное адресное пространство памяти.

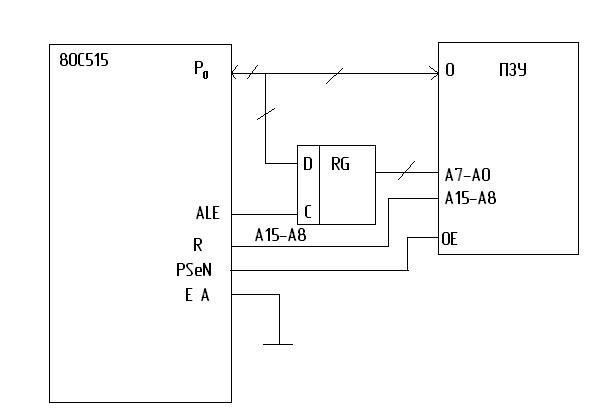

Функциональная схема подключения МК sab80c515

В соответствии с гарвардской архитектурой реаклизуются МК MCS-51 и совместимы с ними. Фирмы – сименс, атмел, авр.

Некоторые семейства, например mcs96 реализуются по принстонтской архитектуре, предполагающей размещение команд и данных в едином адресном пространстве памяти. В МК данной архитектуры память команд и данных разделены только физически.

Объем внутренней памяти программ в МК разных типов варьируется в широких пределах: 1-32 кб, при этом, в некоторых моделях МК память пргог может вообще отсуствовать (ситстемы с внешней памятью программ). Расширение памяти программ допускается за счет подключения дополнительных БИС, подключаемых через внешную магистраль. Производятся МК с программируемым ПЗУ и ППЗУ и смасочным непрограммируемым. Также может быть флеш-память.

Регистровый файл данных RRAM в большинстве случаев в МК объединяет две области памяти – ОП общего назначения, используемую пользователем по своему усмотрению, и регистр спец. функций SFR.

Набор регистров блока SFR может существенно отличаться в МК разных семейств. Регистры SFR управляют внутренними ПУ МК, фиксируют их состояние и др.использование набора программируемых регистров SFR дает возможность программной настройки внутренних ПУ МК на требуемый режим, что расширяет сферу применения МК.

Некоторые МК например mcs96 содержат небольшую внутреннюю память RAM (128-512байт), в которой могут храниться как данные, так и команды. При размещении команд программы в этой памяти появляется возможность дистанционной модификации программ. Допускается расширения памяти МК за счет внешних БИС.

Некоторые МК содержат схемы выборки кристаллов – программные селекторы адресов – позволяют выбрать конкретные области адресного пространства для внешних устройств памяти, упрощающее их подключение.

Описание рисунка Функциональная схема подключения МК sab80c515

Память программ и данных разделены физически.

Память программ объемом 64 кб доступна только по чтению, она м.б. представлена либо в виде внешней памяти XROM, либо в виде XROM и IROM, если имеется внутренняя.

Элементы программной памяти адресуются с помощью 16-разрядного счетчика команд, в некоторых моделях – с помощью спец указателя DPTR.

Возможен запрет/разрешенимя доступа к

IROM сигналом

на одноименном входе МК. Объем IROM

зависти от типа МК.

на одноименном входе МК. Объем IROM

зависти от типа МК.

Внутренняя память IRAM размещенная на кристалле МК представлена двумя физически разделенными блоками:

1)реистровым файлом RRAМ

2) блоком регистров SFR

В отличии от МП в МК отсутствуют специальные выводы сигналов адреса и данных, предназначенные для подключения внешней памяти. При необходимости использования внешней памяти программ или данных для организации внешних шин использую линии портов Р0, Р2 при этом с помощью линии порта Р0 реализуется внешняя шина (адрес/данные) при этом младшие байты на линиях Р0 передаются а старшие на линиях Р2. Для демультиплексирования адреса на выходах порта Р0 имеется сигнал АLЕ с помощью которого младший байт адреса фиксируется во внешнем регистре адреса.

Чтение содержимого памяти осуществляется с помощью сигнала PSEN