- •Микропроцессоры: определение, назначение, основные понятия: мп, мпс, мк и др.

- •Классификация мп

- •Основные параметры мп

- •Системы эвм

- •5 Обобщенная структурная схема мп

- •6 Типичный машинный цикл

- •7 Пути обработки командного и информационного слова

- •8 Архитектура процессоров. Принстонская и гарвардская архитектуры.

- •10 Система команд мп: операции над числами с ф.З. И Пл.З. Условные и безусловные переходы, циклы и др.

- •11 Форматы команд и способы адресации.

- •12 Организация подсистемы прерываний мпс. Классы прерываний. Структурная схема системы. Приоритеты прерываний.

- •13 Контроллер прерываний кр580вн59: схема, режим работы.

- •14 Семейства бис кр580; фирмы Intel

- •15 Микропроцессор кр580вм80а: принципы функционирования, уго, структурная схема.

- •16 Микропроцессор кр580вм80а: уго, схема временные диаграммы командного цикла.

- •17 Микропроцессор бис кр580вм8а уго, схема вд цикла прерываний

- •18 Микропроцессор бис кр580вм8а уго, схема, вд ввода/вывода

- •19 Параллельный интерфейс бис кр580вв55, уго, схема, режимы работы.

- •2 0 Последовательный интерфейс бис кр580вв51.

- •21 Организация режима прямого доступа в память (пдп). Контроллер пдп кр580вт57, уго, схема, режимы работы.

- •22 Организация службы времени. Программируемый таймер кр580ви53. Уго, схема, режимы работы.

- •23 Контроллер видеотерминала кр580вг75: уго структурная схема принцип действия.

- •24 Схема включения контроллера бис кр580вг75 в мпс.

- •25 Особенности архитектуры мп 80486: структурная схема, вд работы. Режимы работы: реальный, защищенный.

- •26 Особенности архитектуры мп Pentium: структурная схема, вд работы.

- •27 Семейство микро-эвм, ключевые мс пк imb pc и совместимые с ними.

- •28 Микроконтроллеры: определение, назначение, структурная схема технологической системы управления.

- •29 Архитектура мк cisk, risk.

- •30 Типы мкс.

- •31 Типовая структура мк

- •32 Функциональная схема мк

- •33 Цпу мк. Архитектура цпу.

- •34 Организация памяти мк.

- •35 Параллельные порты ввода-вывода мк.

- •36 Последовательные порты ввода-вывода мк.

- •37 Функциональная схема ацп мк sasb 80c515

- •38. Блок таймеров и поддержка режима «реального времени».

- •39. Сторожевой таймер.

- •40. Эволюция архитектуры мк: 4-х, 8-и, 16-и, 32-х, 64-х – разрядные мк.

- •41. Интегрированная среда разработки по (ис рпо) для семейства мк avr.

- •42. Программирование мк на языке Ассемблер: процедуры, подпрограммы, директивы.

- •43. Интерфейс встраиваемых мпс: физический и логический. Шины pci, vmEи др.

- •44. Шина usb: характеристики, топология, режимы работы.

- •45. Jtag – интерфейс системные функции на его основе.

- •46. Программируемые логические матрицы и плис.

- •47. Вычислительные системы: определение, назначение, классификация.

- •48. Многопроцессорные вс. Структурная схема.

- •49. Многомашинные вс. Вс с коммутационной матрицей, структурные схемы.

- •50.Проектирование мпс. Средства и методы комплексной отладки мпс.

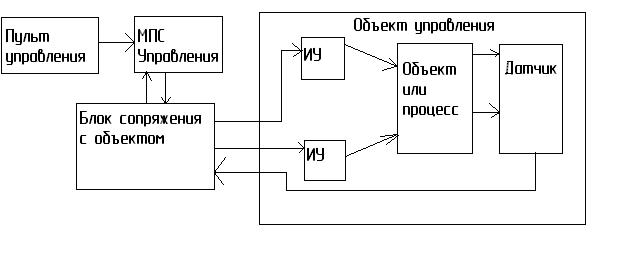

28 Микроконтроллеры: определение, назначение, структурная схема технологической системы управления.

МК называется программируемое, однокристальное ВУ с встроенным набором средств для ввода и вывода применяемых для решения задач управления и первичной обработки данных технологических систем.

Обобщенная структура типовой системы управления(контроллера)

В состав типовой системы управления контроллера входят:

Объект управления, содержащий собственно объект/процесс, исполнительные устройства и систему датчиков, контролирующих параметры объекта

УСО (устройство сопряжения с объектом), обеспечивающее согласование сигналов (как управляющих, та к и информационных) МКС и объекта управления.

Пульт управления, предоставляющий оператору возможность контролировать параметры процесса управления и при необходимости вносить корректировки

Цифровой регулятор (ЦР)

Конкретная реализация ЦР определяется типом системы обработки, зависит от сложности системы управления. На основе ВМ, ВК, ВС, функциональные возможности которых оказываются достаточными для управления данным объектом. Также управляющие устройства принято называть ЦР-ом. В н.в. ЦР чаще всего реализуют на МП-рных и МК-ных системах управления. ЦР чаще всего получает необходимую информацию от измерительных преобразователей (датчиков). Управляющее воздействие на объект управления поступает через ИУ – исполнительное устройство. Для связи ЦР с датчиками и ИУ исп спец. Электронные схемы сопряжения с объектом (УСО). В составе УСО имеются АЦП и ЦАП, буферные усилители сигналов, элементы гальванической развязки электрических цепей. При реализации ЦР на ЭВМ связь с УСО осуществляется через порты вв/выв и спец программы (драйверы).

29 Архитектура мк cisk, risk.

Список команд современного МП может включать большое число команд однако не все команды используются одинаково часто. Например передача регистр-регистр около 4% при целочисленных вычислениях, команда загрузки 28%

Очевидно, различные команды неравномерно используются в типовых программах. Это свойство системы команд МП стало предпосылкой для развития МП с RISC архитектурой то есть архитектура с сокращенным списком команд. МП с расширенным списком команд относятся к CISC, т.е с расширенным списком команд. Исторически первыми были разработаны CISC МП. Идея RISC родилась в середине 70х годов с переходом в программировании на ЯВУ

Первые МП с RISC были реализованы в начале 80х годов в калифорнийском университете города Беркли. Руководитель Паттерсон. В них повышение производительности достигалось за счет аппаратных средств. Увеличен набор РОНов. Регистровый файл от 128 до 256 РОНов. Он разбивался на группы по 32 регистра (Регистровые Окна).

В 1982 году в Стэнфорде под руководством Хенеси был разработан процессор RISC-2 с усиленной конвейерной обработкой. В настоящее время используются МП и МК с RISC-архитектурой активные разработки ведут SPARK и MIPS.

Основные принципы RISC архитектур:

одинаковая длинна команд, что облегчает их выборку из памяти. Все команды считываются за 1 такт одинаковой длины. Длинна 32бит

большое число РОНов. Позволяет уменьшить число обращений к памяти

большинство команд (арифметические и логические) трех адресные, включают КОП, адреса источников и адрес приемника

относительно простые схемы управления.

При одинаковых технологиях производства RISC часто быстрее чем CISC.

Процессоры Pentium, оставаясь CISC, содержат некоторые RISC ядро.