- •Микропроцессоры: определение, назначение, основные понятия: мп, мпс, мк и др.

- •Классификация мп

- •Основные параметры мп

- •Системы эвм

- •5 Обобщенная структурная схема мп

- •6 Типичный машинный цикл

- •7 Пути обработки командного и информационного слова

- •8 Архитектура процессоров. Принстонская и гарвардская архитектуры.

- •10 Система команд мп: операции над числами с ф.З. И Пл.З. Условные и безусловные переходы, циклы и др.

- •11 Форматы команд и способы адресации.

- •12 Организация подсистемы прерываний мпс. Классы прерываний. Структурная схема системы. Приоритеты прерываний.

- •13 Контроллер прерываний кр580вн59: схема, режим работы.

- •14 Семейства бис кр580; фирмы Intel

- •15 Микропроцессор кр580вм80а: принципы функционирования, уго, структурная схема.

- •16 Микропроцессор кр580вм80а: уго, схема временные диаграммы командного цикла.

- •17 Микропроцессор бис кр580вм8а уго, схема вд цикла прерываний

- •18 Микропроцессор бис кр580вм8а уго, схема, вд ввода/вывода

- •19 Параллельный интерфейс бис кр580вв55, уго, схема, режимы работы.

- •2 0 Последовательный интерфейс бис кр580вв51.

- •21 Организация режима прямого доступа в память (пдп). Контроллер пдп кр580вт57, уго, схема, режимы работы.

- •22 Организация службы времени. Программируемый таймер кр580ви53. Уго, схема, режимы работы.

- •23 Контроллер видеотерминала кр580вг75: уго структурная схема принцип действия.

- •24 Схема включения контроллера бис кр580вг75 в мпс.

- •25 Особенности архитектуры мп 80486: структурная схема, вд работы. Режимы работы: реальный, защищенный.

- •26 Особенности архитектуры мп Pentium: структурная схема, вд работы.

- •27 Семейство микро-эвм, ключевые мс пк imb pc и совместимые с ними.

- •28 Микроконтроллеры: определение, назначение, структурная схема технологической системы управления.

- •29 Архитектура мк cisk, risk.

- •30 Типы мкс.

- •31 Типовая структура мк

- •32 Функциональная схема мк

- •33 Цпу мк. Архитектура цпу.

- •34 Организация памяти мк.

- •35 Параллельные порты ввода-вывода мк.

- •36 Последовательные порты ввода-вывода мк.

- •37 Функциональная схема ацп мк sasb 80c515

- •38. Блок таймеров и поддержка режима «реального времени».

- •39. Сторожевой таймер.

- •40. Эволюция архитектуры мк: 4-х, 8-и, 16-и, 32-х, 64-х – разрядные мк.

- •41. Интегрированная среда разработки по (ис рпо) для семейства мк avr.

- •42. Программирование мк на языке Ассемблер: процедуры, подпрограммы, директивы.

- •43. Интерфейс встраиваемых мпс: физический и логический. Шины pci, vmEи др.

- •44. Шина usb: характеристики, топология, режимы работы.

- •45. Jtag – интерфейс системные функции на его основе.

- •46. Программируемые логические матрицы и плис.

- •47. Вычислительные системы: определение, назначение, классификация.

- •48. Многопроцессорные вс. Структурная схема.

- •49. Многомашинные вс. Вс с коммутационной матрицей, структурные схемы.

- •50.Проектирование мпс. Средства и методы комплексной отладки мпс.

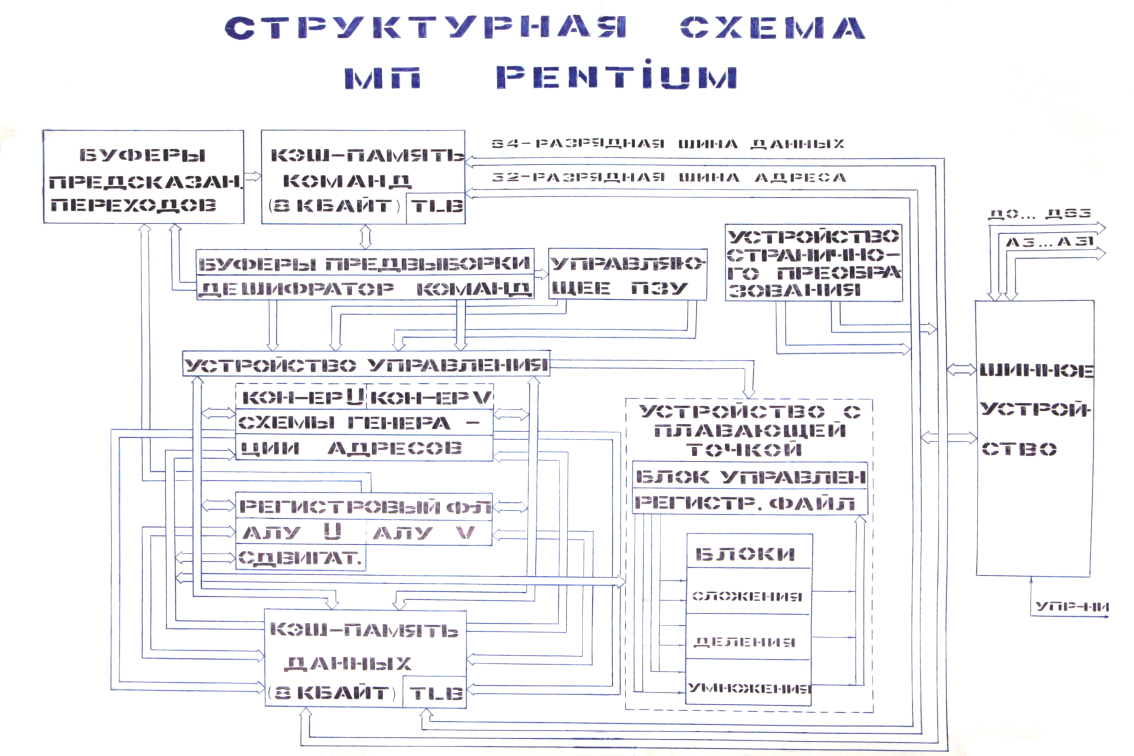

26 Особенности архитектуры мп Pentium: структурная схема, вд работы.

МП Pentium является представителем следующего после 386ого поколения. Представитель фирмы Intel. Он совместим со всеми предыдущими моделями типа 80Х86. новая архитектура, отдельные КЭШ памяти команд и данных, конвейерное устройство обеспечивают значительное повышение производительности. Кристалл данного МП содержит 3.1 млн. транзисторов, реализованных 0.8 микронными технологическими нормами.

Корпус выполнен в виде керамической матрицы с числом рядов 21 на 21 по 4 вывода в каждом ряду. Общее число выводов 273. Столбцы выводов пронумерованы с лева на право от ключа, буквами латинского алфавита от A до W , а строки снизу вверх арабскими цифрами от 1 до 21.

Структурная схема МП Pentium

В структуре можно выделить 2 целочисленных конвейера (2 АЛУ), устройство с плавающей запятой, КЭШ памяти данных и команд, УУ, управление пзу ПЗУ, буфер предварительной выборки, дешифратор команд, буфер предсказания перехода, устройство страничного преобразования, шинное устройство и др.

Два целочисленных конвейера аналогичны друг другу по структуре и порядку функций. В них конвейерный режим, как и в 486 МП реализован 5ти ступенях:

предварительная выборка (PF)

декодирование (D1)

Генерация адреса (D2)

Исполнение (EX)

Обратная запись, результат.(WB)

На первой ступени (PF) команда выбирается из КЭШ памяти или ОЗУ наличие независимых КЭШей данных и команд, исключает конфликты при выборке из памяти.

Два независимых буфера предварительной выборки по 32 байта работают совместно со схемой предсказания переходов.

На ступени D1 выполняется декодирование для запуска 1 или 2 команд одновременно.

Вычисление адресов операндов размещенных в памяти реализуется на ступени D2

На ступени ЕХ команды исполняются в АЛУ

На последней ступени WB фиксируется результат выполненной команды ( обратная запись )

Если на ступени ЕХ происходит задержка выполнения команды в одном из двух конвейеров – последующие команды не поступают пока на обоих конвейерах не завершиться. переход команд на ступень WB

Две КЭШ-памяти данных и команд по 8 кб каждая, реализованы по ассоциативной организации. И выдает информацию из памяти строками по 32 байта, что дает возможность при поиске информации просматривать ее последовательно по 2 строки.

Дешифратор команд преобразует коды выбранных команд для последующего их исполнения на конвейерах.

Управляющее ПЗУ осуществляет непосредственное управление работой двух конвейеров.

Устройство с плавающей запятой позволяет выполнять операции над мантиссами и порядками чисел за 1 такт и так же использует конвейерный режим. Однако выполнение операция в устройстве с плавающей запятой происходит за 8 ступеней.

Ступени 1-4 аналогичны целочисленным конвейерам, кроме того, реализуются операции над порядками, нормализуется результат, округление, сообщения об ошибках

Шинное устройство обеспечивает поддержку нескольких режимов шины в том числе. Групповую передачу данных, изменение длины передаваемых кодов.

Набор регистров МП Pentium аналогичен набору регистров МП Intel 80486

В МП Pentium имеется 16 регистров доступных программисту в том числе

1) 32-разрядные РОНы 8 шт.

2) флаги

3) сегментные регистры (16 бит.) хранящие коды для составления сегментных базовых адресов при обращении в память системы.

В наборе команд микропроцессора добавлены 3 новые прикладные команды. И 4 системные. Они обеспечивают возможности тестирования и отладки. Интерфейс шины МП Pentium близок к шинному интерфейсу МП 486 (расширенная ШД).