- •Теория микропроцессорных систем микроконтроллеры

- •Структура и функциональные возможности мк51

- •Электрический интерфейс мк51

- •Резидентная память данных

- •Работа блока управления и синхронизации

- •Элементы данных в мк51

- •Характеристика функциональных групп команд

- •2.5. Система команд семейства mcs-51.

- •2.5.1. Команды пересылки данных.

- •Команда обработки данных.

- •Команды передачи управления.

- •Характеристика периферийных блоков в составе мк51

- •Управление таймерами-счетчиками (т/с)

- •Описание вариантов конфигурации таймеров-счетчиков

- •Особенности реализации временных интервалов

- •Структура последовательного порта и принципы управления

- •Описание режимов работы уапп

- •Назначение и принципы функционирования системы прерываний

- •Управление приоритетами запросов прерываний

- •Работа системы обслуживания прерываний

- •Заполнение начальной области памяти программ

- •Шестнадцатиразрядные микроконтроллеры Motorola

- •Современные встраиваемые микроконтроллеры, выпускаемые производственной фирмой Freescale Semiconductor

- •Номенклатура и функциональный состав микроконтроллеров cемейства 68hcs12

- •2.1. Микроконтроллеры семейства 68нс12/912

- •2.1.3. Начальный запуск и обработка прерываний

- •2.1.4. Режимы работы и конфигурация микроконтроллеров

- •2.1.5. Функционирование и программирование Flash-памяти и эсппзу

- •2.1.6. Блок контроля функционирования и генератор тактовых импульсов

- •2.1.7. Параллельный ввод-вывод данных и подключение внешней памяти

- •2.1.8. Последовательные порты sci и spi

- •2.1.9. Таймерные модули и широтно-импульсные модуляторы

- •2.1.10. Модуль аналого-цифрового преобразователя atd

- •2.1.11. Модуль последовательного интерфейса msCan

- •2.1.12. Режим отладки bdm и установка контрольных точек

2.1.12. Режим отладки bdm и установка контрольных точек

Микроконтроллеры семейства 68HC(S)12 обеспечивают поддержку ряда механизмов, позволяющих существенно облегчить и ускорить процедуру отладки программного обеспечения. Основным из этих механизмов является режим отладки BDM (Background Debug Mode), который позволяет выполнить основные процедуры отладки - просмотр и модификацию содержимого регистров и ячеек памяти, а также ряд других функций.

В данном разделе описываются возможности выполнения процедур отладки, которые предоставляются пользователям при создании цифровых систем на базе микроконтроллеров семейства 68HC(S)12/912.

Режим отладки BDM. Встроенный блок отладки, реализующий режим BDM, обеспечивает выполнение специальных команд отладки, которые последовательно вводятся в микроконтроллер через вывод BKGD. Используемый при этом протокол последовательного обмена позволяет вводить команды и данные в микроконтроллер от персонального компьютера, выполняющего функции системы отладки, и получать необходимые данные из микроконтроллера по однопроводной линии связи, подключенной к этому выводу. Цикл передачи 1 бита по линии BKGD занимает 16 тактов (периодов Tt), длительность которых задается сигналами ECLOCK. Каждый цикл обмена инициируется компьютером путем подачи на эту линию отрицательного перепада потенциала.

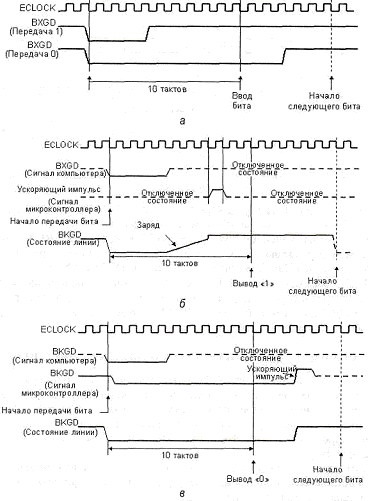

Рис. 2.40. Временные диаграммы циклов обмена при работе в режиме BDM

На рис. 2.40, а показаны временные диаграммы циклов передачи 0 и 1 от компьютера к микроконтроллеру (ввод бита). При передаче 1 компьютер инициирует цикл путем установки 0 на линии BKGD, а через 4 такта устанавливает на этой линии 1, которая поддерживается до начала следующего цикла. При передаче 0 этот уровень сохраняется в течение 13 тактов, после чего компьютер переводит линию в состояние 1. Микроконтроллер считывает состояние линии BKGD через 10 тактов после начала цикла, воспринимая таким образом имеющийся на линии уровень 0 или 1.

При пересылке данных от микроконтроллера к компьютеру их выходы, подключенные к линии BKGD, до начала цикла имеют высокоимпедансное (отключенное) состояние, и на этой линии поддерживается уровень 1 с помощью резистора, «подтягивающего» ее потенциал к напряжению питания. В начале цикла компьютер устанавливает 0 на линии BKGD, который поддерживается в течение четырех тактов. Если в данном цикле микроконтроллер должен передать 1 (рис. 2.40, б), то его выход BKGD сохраняет высокоимпедансное состояние. После отключения компьютера от этой линии потенциал на ней начинает медленно возрастать вследствие заряда паразитной емкости Сп. Для ускорения заряда микроконтроллер в 8-м такте выдает «ускоряющий» импульс, устанавливающий на линии уровень 1. Компьютер считывает состояние линии BKGD в 10-м такте, принимая передаваемую 1.

При передаче 0 выход BKGD микроконтроллера после начала цикла устанавливается в состояние 0, которое сохраняется в течение 13 тактов (рис. 2.40, в). Соответственно уровень 0 будет в течение этого времени поддерживаться и на линии BKGD. В 10-м такте компьютер считывает 0 с этой линии. В 14-м такте микроконтроллер выдает «ускоряющий» импульс, устанавливающий линию BKGD в состояние 1, а затем отключается от линии, переведя свой выход в высокоимпедансное состояние.

Таким образом однопроводной интерфейс BDM обеспечивает в процессе отладки обмен данными между компьютером и микроконтроллером.

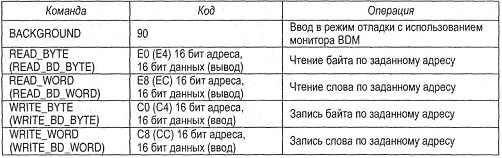

Часть команд отладки может выполняться микроконтроллером в процессе выполнения рабочей программы. При этом используются «холостые» (незанятые) циклы, которые возникают, когда рабочая программа не производит обращение к памяти. Если такие «холостые» циклы не возникают в течение 128 рабочих тактов, то блок BDM захватывает последующие циклы для выполнения поступившей команды отладки. Перечень этих команд отладки приведен в табл. 2.37.

Таблица 2.37. Команды отладки, выполняемые в рабочем режиме

Данные команды (кроме команды BACKGROUND) обеспечивают чтение или запись содержимого регистра или ячейки памяти с заданным адресом. Первый байт команды содержит код операции, далее следует 16-разрядный адрес регистра или ячейки памяти, затем передаются 16-разрядные данные, вводимые компьютером в микроконтроллер (команды WRITE) или выводимые из микроконтроллера для чтения компьютером (команды READ). Если в командах WRITE_BYTE, READ_BYTE указывается четный адрес, то адресуемый байт содержится в старшем байте передаваемых 16-разрядных данных; если указывается нечетный адрес, то адресуемый байт содержится в младшем байте данных. В командах WRITE_WORD, READ_WORD необходимо давать четные адреса, указывающие размещение старшего байта адресуемого 16-разрядного слова.

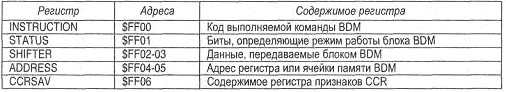

Команды с дополнением _BD_ (в табл. 2.37 коды этих команд указаны в скобках) обеспечивают обращение к памяти блока BDM, которая располагается в диапазоне адресов $FF00-FF (см. рис. 2.5). В этом адресном пространстве находятся 5 регистров блока BDM (табл. 2.38) и ПЗУ, в котором хранится программа-монитор BDM, обеспечивающая выполнение дополнительных команд отладки (см. табл. 2.39). Память блока BDM доступна только в режиме отладки. В рабочем режиме адреса $FF00-FF служат для размещения векторов прерываний и другой информации, необходимой для выполнения текущей задачи (см. 2.1.3 и 2.1.4).

Таблица 2.38. Адреса и содержимое регистров блока BDM

Команда BACKGROUND переводит микроконтроллер в режим работы под управлением монитора BDM, когда процессор прекращает выполнение основной программы и реализует процедуры отладки, задаваемые командами монитора (см. табл. 2.39). Эта команда выполняется только после инициализации монитора путем установки в 1 бита ENBDM в регистре состояния STATUS (рис. 2.41).

Регистры INSTRUCTION, ADDRESS содержат код операции и адрес, которые последовательно вводятся в микроконтроллер при поступлении соответствующей команды BDM (см. табл. 2.38, 2.39), а в регистр SHIFTER заносятся передаваемые данные. Регистр CCRSAV служит для временного сохранения содержимого регистра признаков CCR при работе блока BDM. В процессе работы этого блока содержимое данных регистров может быть только считано.

Для пользователя основной интерес представляет регистр состояния STATUS, задающий режим работы блока BDM. Биты этого регистра имеют следующее назначение (рис. 2.41):

ENBDM - разрешает при значении ENBDM=1 работу монитора BDM, который обеспечивает выполнение команд, приведенных в табл. 2.39;

BDMACT - признак активности монитора BDM (доступен только для чтения), принимает значение BDMACT=1, когда микроконтроллер входит в режим отладки под управлением монитора BDM и готов к приему команд монитора (см. табл. 2.39);

ENTAG - признак работы микроконтроллера в режиме тегирования команд, принимает значение 1 при поступлении команды отладки TAGGO (см. табл. 2.39);

SDV - признак заполнения данными регистра SHIFTER, принимает значение 1, когда введены 16-разрядные данные;

TRACE - признак работы микроконтроллера в режиме трассировки, принимает значение 1 при поступлении команды отладки TRACE1 (см. табл. 2.39);

CLKSW - определяет выбор тактового сигнала при работе микроконтроллера в режиме BDM (используется в моделях 68HC912D60, 68HC912DG128): при CLKSW=0 тактирование производится сигналами с частотой Fq/2, при CLKSW=1 тактирование производится сигналами с частотой Ft (если Ft < Fq/2, то для тактирования используются сигналы с частотой Ft при любом значении бита CLKSW).

При запуске микроконтроллера все биты регистра STATUS принимают значение 0. В процессе работы изменение битов ENDM, CLKSW производится с помощью команды WRITE_BD_BYTE с адресом $FF01 (обращение к регистру STATUS), в которой байт данных содержит требуемые значения соответствующих битов. Биты BDMACT, ENTAG, STV, TRACE автоматически устанавливают свои значения в зависимости от состояния блока BDM и поступивших команд отладки. Изменение их значения путем записи в регистр STATUS нового содержимого не допускается.

![]()

Рис. 2.41. Формат содержимого регистра состояния STATUS блока отладки BDM

Установка в регистре STATUS значения бита ENBDM=1 разрешает работу монитора BDM, который обеспечивает выполнение команд отладки, приведенных в табл. 2.39. После этого микроконтроллер переводится в режим отладки под управлением монитора BDM в следующих случаях:

при вводе команды BACKGROUND (см. табл. 2.37) от компьютера, выполняющего функции системы отладки;

при поступлении команды BGND (см. табл. 2.12);

при поступлении на исполнение команды, отмеченной тегами (при работе микроконтроллера в режиме тегирования);

при достижении определенной контрольной точки в ходе выполнения программы (при установке контрольных точек).

В каждом из этих случаев в регистре STATUS устанавливается значение бита BDMACT=1, процессор CPU12 прекращает выполнение текущей программы и ожидает поступления команд отладки (табл. 2.39), которые побитово вводятся в микроконтроллер от компьютера по линии BGND согласно описанному выше протоколу (см. рис. 2.40).

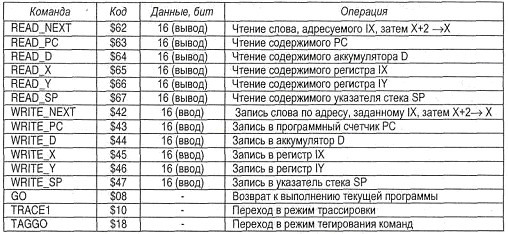

Таблица 2.39. Команды отладки, выполняемые монитором BDM

Основная группа команд отладки, осуществляемых под управлением монитора BDM, выполняет чтение (команды READ_x) или запись (команды WRITE_х) содержимого регистров процессора или ячейки памяти. При обращении к памяти (команды READ_NEXT, WRITYE_NEXT) адрес ячейки задается содержимым индексного регистра IX, которое затем автоматически увеличивается на 2 (автоинкремент) для адресации следующей ячейки. Команда GO обеспечивает возвращение к выполнению текущей программы. Команда трассировки TRACE1 вызывает выполнение следующей команды текущей программы, после чего процессор переводится в режим отладки (пошаговое выполнение программы). Команда TAGGO переводит микроконтроллер в режим тегирования команд, при котором на выходах TAGHI#, TAGLO# формируются сигналы (теги), которые являются признаком выборки очередной команды программы.

Таким образом, набор команд, реализуемых с помощью монитора BDM, обеспечивает в процессе отладки возможность полного контроля над содержимым всех регистров процессора и ячеек памяти (регистров периферийных устройств).

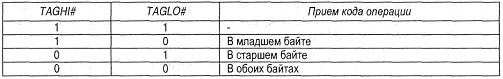

Режим тегирования. Как отмечено выше, данный режим реализуется при вводе в микроконтроллер команды отладки TAGGO. В этом случае микроконтроллер переходит к выполнению текущей программы, устанавливая при выборке из памяти очередного слова соответствующие значения сигналов на выводах TAGHI#, TAGLO# (табл. 2.40). Данные значения сигналов устанавливаются на этих выводах в конце каждого цикла обращения к памяти - при поступлении отрицательного перепада тактового сигнала ECLK. Выходы сигналов TAGHI#, TAGLO# совмещены с выходом строб-сигнала LSTRB# (см. 2.1.5) и выводом BKGD, который используется для ввода-вывода данных в режиме отладки. Тегирование обеспечивается только при работе микроконтроллера в рабочем режиме. При переходе в режим BDM (установка бита BDMACT=1 в регистре STATUS) тегирование прекращается и бит ENTAG в регистре STATUS сбрасывается в 0.

2.40. Значения сигналов TAGHI#, TAGLO# в режиме тегирования команд

В процессе отладки сигналы TAGHI#, TAGLO# используются внешним логическим анализатором для фиксации момента выборки очередной команды. Когда эта команда проходит очередь команд и готова к исполнению, микроконтроллер автоматически переводится в режим отладки с использованием монитора BDM. Таким образом реализуется совместная работа логического анализатора и системы отладки, использующей режим BDM.

Останов в контрольных точках. В микроконтроллерах семейства 68HC(S)12/912 (кроме модели 68НС812А4) реализуются следующие варианты отладки с остановом в контрольных точках:

останов при обращении по одному из двух заданных адресов (двухадресный останов) и выполнение команды прерывания SWI;

останов при обращении по одному из двух заданных адресов (двухадресный останов) и переход в режим отладки с использованием монитора BDM;

останов при обращении по заданному адресу с выборкой указанных данных (останов по заданным адресу или данным) и переход в режим отладки с использованием монитора BDM.

Останов с переходом в режим BDM выполняется только в том случае, если этот режим разрешен предварительной установкой бита ENBDM=1 в регистре STATUS. Значения адресов и данных, при обращении к которым производится останов, задаются путем их записи в специальные регистры BRKAH/L, BRKDH/L. В регистр BRKAH/L (адрес $0022-23) заносится 16-разрядный адрес (старший байт в регистр BRKAH, младший байт в регистр BRKAL), при обращении к которому реализуется останов. Для выполнения останова по заданным адресу или данным в регистр BRKDH/L (адрес $0024-25) записываются значения данных, при выборке которых производится останов. При двухадресном останове в регистр BRKDH/L заносится второй адрес останова.

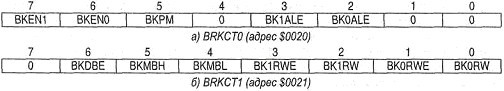

Процедура останова выполняется в соответствии с содержимым регистров управления BRKCT0, BRKCT1. Регистр BRKCT0 содержит следующие биты (рис. 2.42, а):

BKEN1-0 - задают используемый вариант останова: останов не выполняется при BKEN1-0 = 00, двухадресный останов с вызовом команды SWI при BKEN1-0 = 01, останов по заданным адресу или данным при BKEN1-0 = 10, двухадресный останов с переходом в режим BDM при BKEN1-0 =11;

ВКРМ - задает способ останова с переходом в режим BDM: при ВКРМ=0 останов происходит на следующей команде после обращения по заданному адресу, при ВКРМ=1 останов происходит, когда выбранная команда с заданным адресом готова к исполнению (прошла очередь команд);

BK1ALE - определяет использование регистра BRKDL (младший байт) при двухадресном останове: если BK1ALE=0, то 16-разрядный адрес останова определяется с учетом содержимого BRKDL, если BK1ALE=1, то останов производится без учета содержимого BRKDL (по совпадению старших разрядов адреса с содержимым BRKDH);

BK0ALE - определяет использование регистра BRKAL (младший байт) при задании адреса останова: если BK0ALE=0, то 16-разрядный адрес останова определяется с учетом содержимого BRKAL; если BK0ALE=1, то останов производится без учета содержимого BRKAL (по совпадению старших разрядов адреса с содержимым BRKAH).

Рис. 2.42. Формат содержимого регистров управления остановом в контрольной точке

Отметим, что бит ВКРМ определяет способ останова только при переходе в режим BDM (значения битов BKEN1-0 равны 10 или 11). Останов с выполнением команды SWI (значение ВKEN1-0=01) при любом значении ВКРМ происходит, когда выбранная команда с заданным адресом прошла очередь команд (готова к исполнению в следующем такте). Биты BK1ALE, BK0ALE позволяют выполнять останов при обращении к массиву адресов, заданных значением их старшего байта, который задается содержимым регистров BRKDH, BRKAH.

В регистре BRKCT1 содержатся биты, имеющие следующее назначение:

BKDBE - разрешает при значении BKDBE=1 использование регистра BRKDH/L для задания адреса или данных, вызывающих останов (в соответствии со значением битов BKEN1-0 в регистре BRKCT0), при BKDBE=0 реализуются одноадресные остановы по совпадению адреса с содержимым регистра BRKAH/L;

ВКМВН, BKMBL - при значении BKDBE=1 и BKEN1-0=10 (останов по заданным адресу или данным) запрещают использование регистра BRKDH (если ВКМВН=1) или регистра BRKDL (если BKMBL=1) при определении значения данных, вызывающих останов;

BK1RWE - при значении BK1RWE=1 обеспечивает реализацию останова при обращении по адресу, заданному в регистре BRKDH/L (двухадресный останов) с учетом типа выполняемого цикла (запись или чтение);

BK1RW - при значении BK1RWE=1 указывает тип цикла, при выполнении которого производится останов при обращении по адресу, заданному в регистре BRKDH/L: запись при BK1RW=0, чтение при BK1RW=0;

BK0RWE - при значении BK0RWE=1 обеспечивает реализацию останова при обращении по адресу, заданному в регистре BRKAH/L с учетом типа выполняемого цикла (запись или чтение);

BK0RW - при значении BK0RWE=1 указывает тип цикла, при выполнении которого производится останов при обращении по адресу, заданному в регистре BRKAH/L: запись при BK0RW=0, чтение при BK0RW=0.

Если в регистре BRKCT0 бит ВКРМ=1, то останов производится независимо от типа выполняемого цикла, т. е. при любых значениях битов BK1RWE, BK1RW, BK0RWE, BK0RW.

Таким образом, установкой соответствующих значений управляющих битов в регистрах BRKCT0 и BRKCT1 можно обеспечить различные варианты останова как в отдельных контрольных точках, так и при обращении к определенным массивам команд и данных.

Заключение

Семейство 68HCS12 содержит в настоящее время более 50 моделей микроконтроллеров, содержащих высокопроизводительный процессор (около 10 миллионов операций в секунду), программируемую в системе Flash-память значительного объема (до 256 Кбайт) и большой набор периферийных модулей. По сравнению с другими популярными семействами 16-разрядных микроконтроллеров это семейство имеет ряд преимуществ [5]. Часто применяемые в аппаратуре российских производителей микроконтроллеры семейств Intel 196, Intel 186 значительно (в 5-8 раз) уступают семейству HCS12 по объему внутренней памяти (ПЗУ и ОЗУ), имеют меньший набор периферийных модулей и требуют использования более сложных и дорогостоящих средств отладки. Микроконтроллеры семейства MSP430x компании Texas Instruments отличаются исключительно малой потребляемой мощностью (менее 1 мВт при тактовой частоте 1 МГц), наличием высокоточных АЦП с 12- и 14-битным разрешением, наиболее низкой стоимостью. Однако они имеют ограниченный набор команд и способов адресации, существенно меньший объем внутренней памяти (в 4-6 раз), более низкую производительность (в 3-4 раза), менее широкий набор периферийных модулей. Наиболее высокую производительность обеспечивают RISC-микроконтроллеры семейств C16x компании Infineon и ST10x компании STMicroelectronics (в 3-4 раза выше, чем HCS12), которые имеют сокращенный набор команд и способов адресации. По объему внутренней памяти и набору периферийных модулей эти микроконтроллеры близки к семейству HCS12. Их недостатками являются значительная потребляемая мощность (в 3 раза выше, чем для микроконтроллеров HCS12) и более высокая стоимость. Следует отметить, что по количеству реализуемых коммуникационных интерфейсов (до пяти CAN, до трех SCI и SPI, один I2C) микроконтроллеры серии Dx семейства HCS12 значительно превосходят своих конкурентов. Таким образом по совокупности основных показателей микроконтроллеры семейства HCS12 являются оптимальным решением для многих применений.

Широкий набор команд и способов адресации в микроконтроллерах HCS12 является весьма удобным для пользователя и эффективным для реализации разнообразных приложений. Аппаратная реализация основных процедур "нечеткой логики", операций умножения с накоплением, табличной интерполяции, поиска минимума-максимума позволяет создавать на основе этих микроконтроллеров устройства, использующие новые алгоритмы управления и преобразования данных.

Все модели семейства содержат сторожевой таймер и реализуют контроль рабочей частоты, что повышает надежность функционирования систем, в которых применяются эти микроконтроллеры.

Следует отметить наличие эффективных средств для поддержки отладки. В первую очередь, это реализация режима отладки BDM с использованием простого адаптера и всего одного вывода микроконтроллера. Данный режим позволяет проводить отладку в реальном масштабе времени без использования дорогостоящих схемных эмуляторов.

Номенклатура

семейства 68HCS12

позволяет реализовать большой круг

приложений в промышленной автоматике,

контрольно-измерительной аппаратуре,

автомобильной электронике и других

областях, требующих высокой

производительности процессора,

значительного объема внутренней памяти

и широкого набора периферийных устройств.

Микроконтроллеры этого семейства

обеспечивают весьма широкий спектр

применений, позволяя реализовать высокие

технико-экономические характеристики,

что делает их привлекательными для

использования в разнообразных разработках.

Номенклатура

семейства 68HCS12

позволяет реализовать большой круг

приложений в промышленной автоматике,

контрольно-измерительной аппаратуре,

автомобильной электронике и других

областях, требующих высокой

производительности процессора,

значительного объема внутренней памяти

и широкого набора периферийных устройств.

Микроконтроллеры этого семейства

обеспечивают весьма широкий спектр

применений, позволяя реализовать высокие

технико-экономические характеристики,

что делает их привлекательными для

использования в разнообразных разработках.

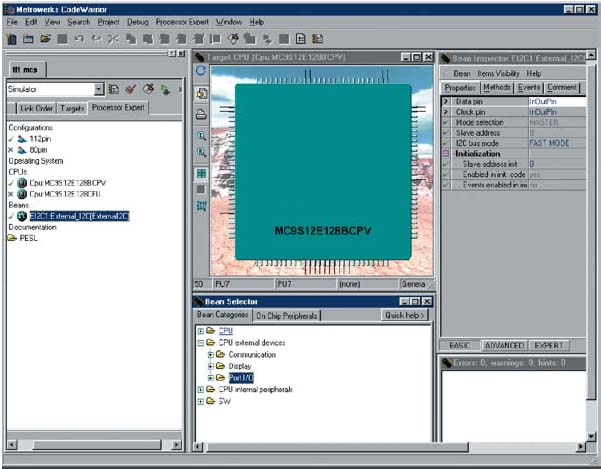

Пакет "CodeWarrior Development Studio" фирмы Metrowerks

Пакет включил в себя наиболее удачные утилиты от разных фирм, специализирующихся на разработке программного обеспечения для микроконтроллеров Motorolа . Основой пакета является интегрированная среда фирмы Metrowerks. Это IDE, менеджер проекта, ассемблер, C++-компилятор и линковщик.

Кроме этих привычных средств, в пакет включена новая мощная утилита - генератор кода фирмы UNIS. является средством визуального объектно-ориентированного программирования и напоминает программирование в среде Visual Basic или Delphi на персональном компьютере.

Кроме

того, пакет содержит программу-отладчик

от фирмы P&E Microcomputers, которая может

работать как симулятор, а также позволяет

отлаживать прикладную программу

непосредственно в целевой системе по

шагам и может управлять прошивкой

целевого микроконтроллера. Приятной

особенностью отладчика от фирмы P&E

является возможность создания визуальных

графических объектов, таких, как

светодиоды, кнопки, жидкокристаллический

индикатор, которые позволяют сделать

процесс отладки более наглядным.

Кроме

того, пакет содержит программу-отладчик

от фирмы P&E Microcomputers, которая может

работать как симулятор, а также позволяет

отлаживать прикладную программу

непосредственно в целевой системе по

шагам и может управлять прошивкой

целевого микроконтроллера. Приятной

особенностью отладчика от фирмы P&E

является возможность создания визуальных

графических объектов, таких, как

светодиоды, кнопки, жидкокристаллический

индикатор, которые позволяют сделать

процесс отладки более наглядным.

Пакет "CodeWarrior Development Studio" доступен в бесплатной редакции "Special Edition" и в коммерческих "Standard Edition" и "Professional Edition".

Версия "Special Edition" имеет ограничения по размеру кода до 12 Кбайт для С-компилятора, позволяет использовать в проекте не более 32 файлов и открывает доступ только к стандартным функциям генератора кода "Processor Expert". При этом поддерживаются все функции макро-aссемблера, симулятора и функции прошивки кристаллов.

Особенности пакета CodeWarrior Development Studio

Совместим с Windows 98/2000/NT4.0/XP;

Обеспечивается поддержка кристаллов нового семейства HCS12;

Предоставляются шаблоны проектов различной сложности - от программирования на ассемблере до проектов на С++;

Мощный ассемблер с поддержкой как абсолютного ассемблирования, так и перемещаемого кода;

Гибкая настройка оптимизации компилятора (до 50 опций);

Поддержка нескольких версий компиляции (targets); Анализатор эффективности кода;

Симулятор/дебаггер со средствами визуализации;

Поддержка отладки с использованием BDM-узла микроконтроллеров HCS12;

Поддержка форматов ELF/DWARF для внутрисхемных эмуляторов;

Поддержка программирующих средств от фирм Motorola, P&E Microcomputer Systems, SofTec Microcsystems, Abatron.