- •Теория микропроцессорных систем микроконтроллеры

- •Структура и функциональные возможности мк51

- •Электрический интерфейс мк51

- •Резидентная память данных

- •Работа блока управления и синхронизации

- •Элементы данных в мк51

- •Характеристика функциональных групп команд

- •2.5. Система команд семейства mcs-51.

- •2.5.1. Команды пересылки данных.

- •Команда обработки данных.

- •Команды передачи управления.

- •Характеристика периферийных блоков в составе мк51

- •Управление таймерами-счетчиками (т/с)

- •Описание вариантов конфигурации таймеров-счетчиков

- •Особенности реализации временных интервалов

- •Структура последовательного порта и принципы управления

- •Описание режимов работы уапп

- •Назначение и принципы функционирования системы прерываний

- •Управление приоритетами запросов прерываний

- •Работа системы обслуживания прерываний

- •Заполнение начальной области памяти программ

- •Шестнадцатиразрядные микроконтроллеры Motorola

- •Современные встраиваемые микроконтроллеры, выпускаемые производственной фирмой Freescale Semiconductor

- •Номенклатура и функциональный состав микроконтроллеров cемейства 68hcs12

- •2.1. Микроконтроллеры семейства 68нс12/912

- •2.1.3. Начальный запуск и обработка прерываний

- •2.1.4. Режимы работы и конфигурация микроконтроллеров

- •2.1.5. Функционирование и программирование Flash-памяти и эсппзу

- •2.1.6. Блок контроля функционирования и генератор тактовых импульсов

- •2.1.7. Параллельный ввод-вывод данных и подключение внешней памяти

- •2.1.8. Последовательные порты sci и spi

- •2.1.9. Таймерные модули и широтно-импульсные модуляторы

- •2.1.10. Модуль аналого-цифрового преобразователя atd

- •2.1.11. Модуль последовательного интерфейса msCan

- •2.1.12. Режим отладки bdm и установка контрольных точек

2.1.10. Модуль аналого-цифрового преобразователя atd

В состав большинства микроконтроллеров семейства 68HC(S)12.912 входят 1 или 2 модуля ATD, которые содержат 10-разрядные АЦП последовательного приближения, имеющие по 8 входных каналов. Эти каналы совмещены с выводами параллельных портов ввода данных AD.

Для функционирования модуля ATD необходимо подключить опорное напряжение к выводам Vrh (высокий потенциал), Vrl (низкий потенциал). Типовые значения потенциалов, подаваемых на эти выводы: Vrh = 5 В, Vrl = 0 В. При этом разрешающая способность преобразователя составляет около 5 мВ, а погрешность измерения 2,5 мВ.

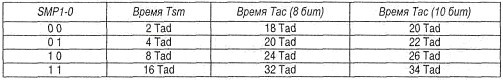

В процессе работы АЦП принимает потенциал, установленный на выбранном аналоговом входе AN7-0 порта AD, и формирует 10- или 8-разрядное число, соответствующее величине этого потенциала, которое записывается в один из восьми регистров результата ADR0H/L-ADR7H/L. Поступающий на аналоговый вход потенциал Vвх должен находиться в диапазоне Vап > Vвх > Vаз, где Vап, Vаз - потенциалы на выводах питания и «земли» АЦП. Общее время одного преобразования Tad составляет от 18Tad до 34Tad, где Tad - длительность цикла преобразования, который задается частотой тактирования преобразователя Fad=1/Tad. Значение Тас определяется значением битов SMP1-0 в регистре управления ADCTL4 (рис. 2.36, в).

АЦП может работать в режиме одноканального или многоканального опроса. При одноканальном опросе АЦП выполняет цикл из четырех или восьми последовательных преобразований данных, поступающих на один из аналоговых входов, записывая результаты в соответствующие регистры ADR0H/L-ADR7H/L. При многоканальном опросе АЦП выполняет преобразование данных, поступающих на группу из четырех или восьми аналоговых входов, записывая результат, полученный для каждого из опрошенных каналов в соответствующий регистр ADR0H/L-ADR7H/L. В режиме повторения (сканирования) одноканальный или многоканальный циклы преобразования непрерывно повторяются, а результаты, полученные в новом цикле, записываются в регистры ADR0H/L-ADR7H/L вместо результатов предыдущего цикла.

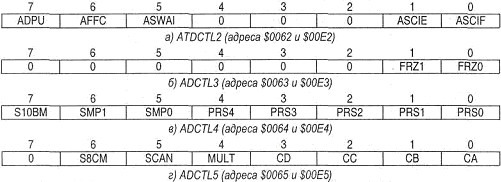

Режимы работы АЦП определяются содержимым регистров управления ATDCTL2-5 (рис. 2.36).

Так как в некоторых моделях (68HC912D60, DG128) содержатся два модуля ATD, то для адресов регистров будут указываться два значения - первый для модуля ATD0 (эти адреса используются и для обращения к АЦП в микроконтроллерах, содержащих один модуль ATD), второй - для модуля ATD1 (если данная модель содержит два АЦП).

В регистре управления ATDCTL2 (рис. 2.36, а) содержатся биты, имеющие следующее назначение:

Рис. 2.36. Формат содержимого регистров управления модулем ATD

ADPU - разрешает при значении ADPU=1 работу модуля ATD;

AFFC - определяет способ сброса в 0 признаков SCF, CCF7-0 в регистре состояния ATDSTAT (рис. 2.37): при AFFC=0 сброс признака SCF производится при записи нового содержимого в регистр ADCTL5 (запуск нового цикла преобразования), а признаки CCF7-0 сбрасываются после чтения содержимого регистра состояния ATDSTAT и последующего чтения соответствующего регистра результата; при AFFC=1 сброс признака SCF производится при чтении содержимого любого из регистров результата, а признаки CCF7-0 сбрасываются после чтения содержимого регистра результата, соответствующего данному каналу;

ASWAI - разрешает при значении ASWAI=1 работу модуля ATD в режиме ожидания;

ASCIE - разрешает при значении ASCIE=1 прерывание при установке признака ASCIF=1 (завершение очередного цикла преобразования);

ASCIF - признак завершения цикла преобразования (доступен только для чтения), принимает значение ASCIF=1 при окончании заданного цикла.

Регистр ATDCTL3 (рис. 2.36, б) содержит биты FRZ1-0, которые определяют возможность работы АЦП в режиме отладки BDM: при FRZ1-0=00 - продолжение работы АЦП, при FRZl-0=10 - завершение очередного цикла и последующая остановка, при FRZ 1-0=11 - остановка АЦП сразу после входа микроконтроллера в режим ВDM.

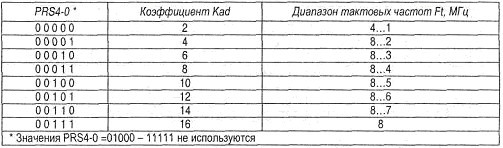

В регистре ATDCTL4 (рис. 2.36, в) бит S10BM задает разрядность выполняемого преобразования: 10 бит при S10BM=1, 8 бит при S10BM=1. Тактирование АЦП осуществляется сигналами, которые получаются путем деления частоты основных тактовых импульсов Ft на коэффициент Kad, задаваемый значением битов PRS4-0 в регистре ATDCTL4. При этом нормальная работа АЦП обеспечивается, если его тактирование производится сигналами с частотой Fad=Ft/Kad, которая должна находиться в диапазоне 2,0...0,5 МГц. Необходимые значения битов PRS4-0 в регистре ATDCTL4 устанавливаются в соответствии с табл. 2.31.

Биты SMP1-0 в этом регистре задают время выборки входного сигнала Tsm (табл. 2.32), значение которого выбирается пользователем в зависимости от скорости изменения потенциала на входах AN7-0.

Таблица 2.31. Значения коэффициента деления Kad для модуля ATD

Таблица 2.32. Время выборки Tsm и преобразования Тас аналогового

сигнала в АЦП

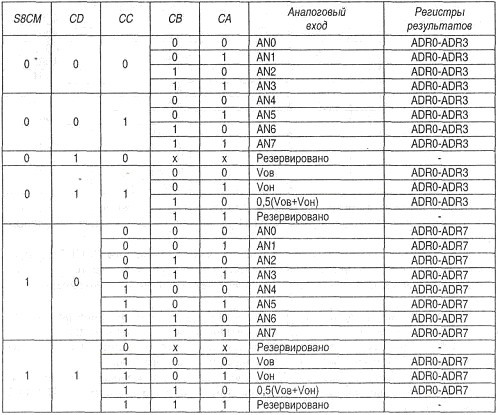

В регистре ADCTL5 (рис. 2.36, г) содержатся биты, определяющие режим преобразования:

S8CM - определяет количество выполняемых циклов преобразования: при S8CM=0 каждый цикл состоит из четырех преобразований, при S8CM=1 цикл состоит из восьми преобразований;

SCAN - задает при значении SCAN=1 режим повторения (сканирования), при котором одноканальный или многоканальный циклы преобразования непрерывно повторяются, а результаты, полученные в новом цикле, записываются в регистры ADR0-ADR3 вместо результатов предыдущего цикла; при SCAN=0 работа АЦП останавливается после выполнения первого цикла преобразований;

MULT - устанавливает многоканальный (при MULT=1) или одноканальный (при MULT=0) циклы преобразования;

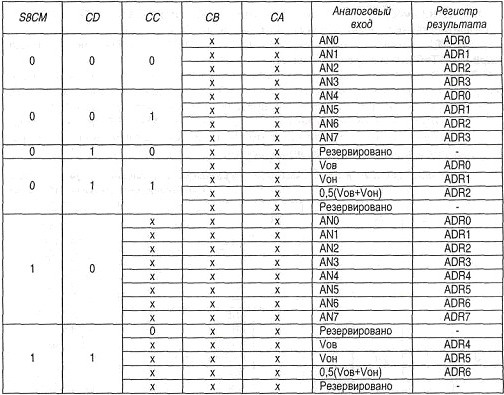

СА, СВ, СС, CD - осуществляют выбор аналогового входа и регистра для записи результата в соответствии с табл. 2.33 и 2.34 (измерение потенциалов Vrh, Vrl, 0,5(Vrh+Vrl) обычно производится при проверке правильности работы АЦП).

При запуске микроконтроллера все биты в регистре ADCTL5 принимают значение 1. Запись нового содержимого в этот регистр вызывает начало процесса преобразования в соответствии с заданным режимом.

Таблица 2.33. Выбор аналоговых входов и регистров результата при работе АЦП

в одноканальном режиме (MULT=0)

Таблица 2.34. Выбор аналоговых входов и регистров результата при работе АЦП

в многоканальном режиме (MUL Т=1)

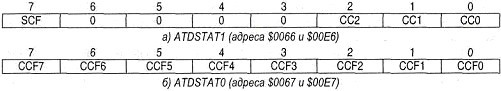

В 16-разрядном регистре ATDSTAT1/0 (рис. 2.37), содержимое которого доступно только для чтения, при работе АЦП устанавливаются значения следующих признаков:

SCF - признак завершения цикла при одноканальном опросе (MULT=0), принимает значение SCF=1 после окончания цикла из четырех или восьми преобразований (в режиме сканирования значение SCF=1 устанавливается по окончании первого цикла);

СС2-0 - счетчик выполненных преобразований, при одноканальном режиме его содержимое показывает, сколько преобразований проведено в данном цикле;

CCF7-0 - признаки получения результата, принимают значение CCFx=1, когда в регистр ADRxH/L поступает результат очередного преобразования.

Сброс в 0 признаков SCF и CCF7-0 производится с помощью описанных выше процедур в зависимости от значения бита AFFC в регистре ATDCTL2 (см. рис. 2.36, а).

Рис. 2.37. Формат содержимого регистра состояния модуля ATD

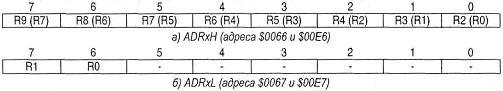

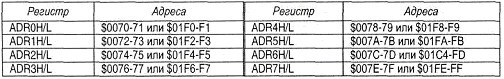

Результаты преобразований, представленные в виде 10- или 8-разрядных чисел R9-0 или R7-0, заносятся в 16-разрядные регистры ADRxH/L, адреса которых приведены в табл. 2.35. Размещение результата начинается со старшего бита R9 или R7 (рис. 2.38), при этом результат 8-разрядного преобразования, который получается при значении бита S10ВМ=0 в регистре ADCTL4, полностью располагается в регистре ADRxH.

Рис. 2.38. Формат содержимого регистров результатов модуля ATD

Таблица 2.35. Адреса регистров результата ADRxH/L

Следует отметить, что АЦП в микроконтроллерах семейства 68НС12/912 не вырабатывает запрос прерывания. Поэтому необходимо организовать считывание регистров результата ADRxH/L по результатам анализа значений признаков в регистре состояния ATDSTAT.

Порт AD, выводы которого PAD7-0 совмещены с аналоговыми входами AN7-0, может использоваться для ввода данных, считывание которых производится путем обращения к регистру PORTAD (адрес $006F). Считывание данных со входов порта AD может производиться и в процессе приема аналоговых сигналов, однако если значение потенциалов на этих входах не соответствует стандартным уровням 0 и 1, то введенные данные будут иметь произвольное значение.