- •Теория микропроцессорных систем микроконтроллеры

- •Структура и функциональные возможности мк51

- •Электрический интерфейс мк51

- •Резидентная память данных

- •Работа блока управления и синхронизации

- •Элементы данных в мк51

- •Характеристика функциональных групп команд

- •2.5. Система команд семейства mcs-51.

- •2.5.1. Команды пересылки данных.

- •Команда обработки данных.

- •Команды передачи управления.

- •Характеристика периферийных блоков в составе мк51

- •Управление таймерами-счетчиками (т/с)

- •Описание вариантов конфигурации таймеров-счетчиков

- •Особенности реализации временных интервалов

- •Структура последовательного порта и принципы управления

- •Описание режимов работы уапп

- •Назначение и принципы функционирования системы прерываний

- •Управление приоритетами запросов прерываний

- •Работа системы обслуживания прерываний

- •Заполнение начальной области памяти программ

- •Шестнадцатиразрядные микроконтроллеры Motorola

- •Современные встраиваемые микроконтроллеры, выпускаемые производственной фирмой Freescale Semiconductor

- •Номенклатура и функциональный состав микроконтроллеров cемейства 68hcs12

- •2.1. Микроконтроллеры семейства 68нс12/912

- •2.1.3. Начальный запуск и обработка прерываний

- •2.1.4. Режимы работы и конфигурация микроконтроллеров

- •2.1.5. Функционирование и программирование Flash-памяти и эсппзу

- •2.1.6. Блок контроля функционирования и генератор тактовых импульсов

- •2.1.7. Параллельный ввод-вывод данных и подключение внешней памяти

- •2.1.8. Последовательные порты sci и spi

- •2.1.9. Таймерные модули и широтно-импульсные модуляторы

- •2.1.10. Модуль аналого-цифрового преобразователя atd

- •2.1.11. Модуль последовательного интерфейса msCan

- •2.1.12. Режим отладки bdm и установка контрольных точек

2.1.9. Таймерные модули и широтно-импульсные модуляторы

В состав микроконтроллеров семейства 68НС12/912 входит 16-разрядный 8-канальный таймерный модуль, который имеет две модификации - TIM и ЕСТ, а также 16-разрядный счетчик внешних событий. Кроме того, все микроконтроллеры имеют отдельный таймер для реализации периодических прерываний.

Таймерный модуль TIM используется в моделях 68НС812А4, 68НС912В32, 68НС912ВС32. Он содержит 16-разрядный таймер-счетчик с программируемым делителем частоты и 8 каналов входа-выхода, индивидуально настраиваемых на работу в режиме захвата или в режиме сравнения. Сигналы захвата-сравнения поступают на выводы 8-разрядного порта Т. Неиспользуемые таймером линии этого порта могут служить для ввода-вывода данных.

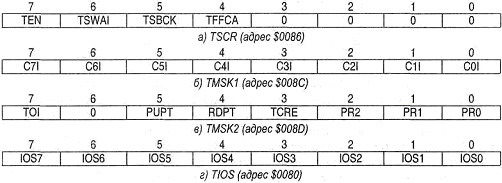

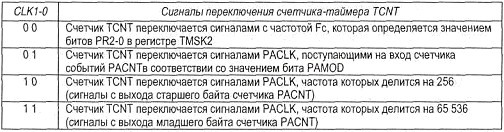

Таймер-счетчик TCNT располагается по адресу $0084-85 (старший байт - младший байт). Его содержимое доступно только для чтения, причем для получения правильного текущего значения следует считывать сразу 16-разрядное слово. Выбор переключающих сигналов для счетчика TCNT определяется значением битов CLK1-0 в регистре PACTL (см. рис. 2.29, а). При CLK1-0=00 частота переключения счетчика TCNT составляет Fc=Ft/Kc, где коэффициент деления Кс задается битами PR2-0 в регистре TMSK2 (рис. 2.25, в). При других значениях CLK1-0 переключение TCNT производится сигналами, поступающими от счетчика событий (см. табл. 2.26). Режим работы таймера-счетчика определяется содержимым регистров управления TSCR, TMSK1, TMSK2.

Рис. 2.25. Формат содержимого регистров управления таймерным модулем

Регистр TSCR (рис. 2.25, а) содержит следующие управляющие биты:

TEN - разрешает при значении TEN=1 работу таймерного модуля (включая счетчик TCNT);

TSWAI - останавливает работу таймера в режиме ожидания при значении TSWAI=1;

TSBCK - останавливает работу таймера в режиме отладки BDM (см. 2.1.12) при значении TSBCK=1;

TFFCA - обеспечивает при значении TFFCA=1 автоматический сброс в 0 признаков в регистрах TFLG1, TFLG2, PAFLG в случае выполнения определенных процедур, описанных ниже.

Регистр TMSK1 (рис. 2.25, б), содержит биты C7I-C0I, которые при значении CiI=1 разрешают формирование запроса прерывания в случае срабатывания i-ro канала таймера (при установке в регистре TFLG1 признака Cil=1).

Биты регистра TMSK2 (рис. 2.25, в) имеют следующее назначение:

TOI - разрешает при значении ТОI=1 формирование запроса прерывания при переполнении счетчика TCNT (в регистре TFLG2 признак TOF=1);

TCRE - обеспечивает при значении TCRE=1 перезапуск счетчика TCNT в случае совпадения в канале 7 таймерного модуля;

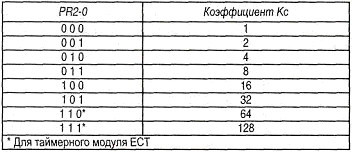

PR2-0 - определяет значение коэффициента деления Кс (табл. 2.24), задающего частоту переключения счетчика TCNT.

В регистре TMSK2 содержатся также бит PUPT, который при PUPT=1 вызывает подключение ко всем выводам порта Т резисторов, «подтягивающих» их потенциал к напряжению питания, и бит RDPT, который при RDPT=1 обеспечивает для выходов этого порта пониженные значения выходных токов (см. 2.1.7).

Таблица 2.24. Значения коэффициента деления частоты Кс

для счетчика-таймера

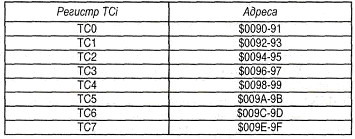

Таймерный модуль содержит 8 каналов с номерами от 0 до 7, каждый из которых может работать в режиме захвата или совпадения. Режим работы i-ro канала задается установкой значения соответствующего бита IOSi в регистре TIOS (рис. 2.25, г): при IOSi=0 канал работает в режиме захвата, при IOSi=l - в режиме совпадения. Входом (в режиме захвата) или выходом (в режиме совпадения) сигнала для i-ro таймерного канала является соответствующий вывод PTi порта Т. Каждый канал содержит 16-разрядный регистр TCi, в котором фиксируется время поступления входного сигнала ICi в режиме захвата или задается время выдачи выходного сигнала OCi в режиме совпадения. Адреса регистров TCi приведены в табл. 2.25.

Таблица 2.25. Адреса регистров TCi таймерных каналов

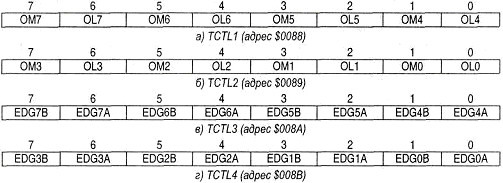

Работа каналов в режимах захвата и совпадения определяется содержимым регистров TCTL1, 2 и TCTL3, 4 (рис. 2.26). Биты OMi-OLi в регистрах TCTL1, 2 задают вид выходного сигнала OCi, формируемого на выходе i-ro канала (вывод PTi) при совпадении содержимого счетчика TCNT и соответствующего регистра TCi (см. табл. 1.71). Биты EDGiB-EDGiA в регистрах TCTL3, 4 определяют вид сигнала ICi, поступающего на входе i-ro канала (вывод PTi), который вызывает захват в регистр TCi текущего содержимого счетчика TCNT (см. табл. 1.71). При значениях OMi=OLi=0 или EDGiB=EDGiA=0 соответствующий i-й таймерный канал отключается от вывода PTi и этот вывод может использоваться для обмена данными через порт Т (см. 2.1.7).

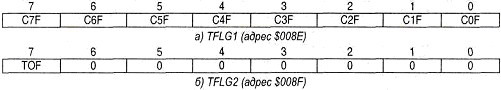

При срабатывании i-ro таймерного канала (захвате или совпадении) в регистре TFLG1 (рис. 2.27, а) автоматически устанавливается значение i-ro признака CiF=1. Если в регистре TMSK1 соответствующий бит CiI=l, то формируется запрос прерывания с обращением к вектору, адрес которого зависит от номера канала (см. табл. 2.14). В регистре TFLG2 (рис. 2.27, б) устанавливается значение признака TOF=1 при переполнении таймера (изменении содержимого с $FFFF на $0000). Если в регистре TMSK2 значение бита ТОI=1, то формируется запрос прерывания с обращением к вектору с адресом $FFDE-DF(cm. табл. 2.14). Сброс в 0 значений признаков CiF, TOF производится путем записи 1 в соответствующий бит содержимого регистров TFLG1, TFLG2. При значении бита TFFCA=1 в регистре TSCR сброс в 0 признака CiF производится при чтении содержимого регистра TCi, если i-й канал работает в режиме захвата, или при записи нового содержимого в TCi, если этот канал работает в режиме совпадения. Сброс в 0 признака TOF при значении TFFCA=1 можно выполнить путем чтения содержимого счетчика TCNT.

Рис. 2.26. Формат содержимого регистров, задающих вид сигналов совпадения (а, б) и захвата (в, г) таймерного модуля

Рис. 2.27. Формат содержимого регистров признаков таймерного модуля TFLG1,2

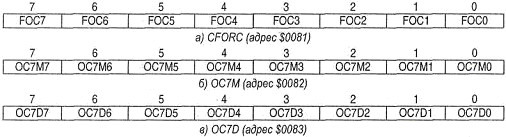

При работе каналов в режиме совпадения имеется возможность форсировать выдачу заданных значений выходных сигналов OCi на соответствующие выводы порта Т путем установки в регистре CFORC (рис. 2.28, а) битов FOCi=l. Таким образом обеспечивается установка заданных сигналов OCi программным способом,

Таймерный модуль можно запрограммировать для формирования на выходах РТ7-0 заданного выходного кода в определенные моменты времени. Для выполнения этой функции используется регистр 7-го канала ТС7 и дополнительные регистры ОС7М, OC7D (рис. 2.28, б, в). В регистр ТС7 записывается число, определяющее момент выдачи заданного кода. В регистре ОС7М устанавливаются значения битов OC7Mi=l для тех выводов PTi, на которые должен поступать заданный код. В регистр OC7D записывается код, который поступает на эти выводы в момент совпадения содержимого ТС7 и TCNT. Таким образом может выдаваться код, содержащий до восьми разрядов.

Порт Т, входящий в состав таймерного модуля, имеет 8 выводов РТ7-0, которые могут служить для параллельного ввода-вывода данных, если они не используются соответствующими таймерными каналами. Передача данных через этот порт обеспечивается с помощью регистра данных PORTT и регистра направления DDRT (см. 2.1.7). При этом биты PUPT, RDPT в регистре TMSK2 определяют режим работы выходных каскадов с подключением «подтягивающих» резисторов или с пониженными токами нагрузки.

Рис. 2.28. Формат содержимого регистра CFORC (а), обеспечивающего форсированную выдачу выходных сигналов, и регистров OС7М (б), OC7D (в), реализующих выдачу заданного кода в установленный момент времени

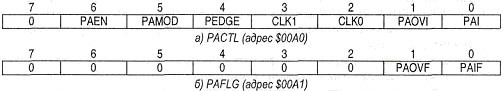

В состав таймерного модуля входит 16-разрядный счетчик событий PACNT (адреса $00A2-A3), работа которого контролируется с помощью регистров PACTL, PAFLG (рис. 2.29). Счетчик имеет два режима работы. В режиме счета внешних событий он переключается внешними сигналами, поступающими на вход PAI (вывод РТ7 порта Т). В режиме стробируемого таймера счетчик PACNT переключается внутренними импульсами с частотой Ft/64, а сигналы на входе PAI вызывают его запуск и формирование запросов прерывания.

Регистр PACTL (рис. 2.29, а), управляющий работой счетчика событий, содержит следующие биты:

PAEN - разрешает при значении PAEN=1 работу счетчика событий;

PAMOD - определяет режим работы счетчика: в качестве счетчика событий при PAMOD=0, в качестве стробируемого таймера при PAMOD=1;

PEDGE - задает вид сигнала на входе PAI, вызывающего переключение счетчика (при PAMOD=0) или запуск таймера (при PAMOD=1);

CLK1-0 - определяют выбор сигналов, переключающих таймер-счетчик TCNT (см. табл. 2.26);

РАОVI - разрешает при значении PAOVI=1 формирование запроса прерывания в случае переполнения счетчика (установка признака POVF=1);

PAI - разрешает при значении РА1=1 формирование запроса прерывания в случае поступления сигнала на вход PAI счетчика (установка признака РАI=1).

Рис. 2.29. Формат содержимого регистров PACTL, PAFLG счетчика событий

Значение бита PAMOD задает выбор сигнала PACLK, переключающего счетчик PACNT: при PAMOD=0 в качестве PACLK используются внешние сигналы на входе PAI, при PAMOD=1 - импульсы с частотой Ft/64.

Бит PEDGE при PAMOD=0 определяет вид сигнала, переключающего счетчик PACNT: положительный перепад потенциала на входе PAI, если PEDGE=1; отрицательный перепад потенциала, если PEDGE=0. При PAMOD=1 бит PEDGE определяет вид строб-сигнала, разрешающего переключение PACNT:

если PEDGE=0, то переключение разрешается при подаче 0 на вход PAI, а поступление на этот вход положительного перепада потенциала вызовет установку признака РАI=1 в регистре PAFLG;

если PEDGE=1, то переключение разрешается при подаче 1 на вход PAI, а при поступлении на этот вход положительного перепада потенциала устанавливается значение признака РАI=1.

В регистре PAFLG (рис. 2.29, б) устанавливаются значения признака PAVF=1 при переполнении счетчика событий и признака РАI=1 при поступлении на вход PAI определенного перепада потенциала, указанного значением бита PEDGE. В этом случае формируется запрос прерывания от счетчика событий, если соответствующий бит разрешения PAOVI или PAI в регистре PACTL равен 1. Переполнение счетчика при значении бита PAOVI=1 вызывает обращение к вектору прерывания, расположенному по адресу $FFDC-DD, поступление соответствующего перепада на вход PAI - обращение к вектору по адресу $FFDA-DB (см. 2.1.3). Сброс в 0 признаков PAOVF, PAIF производится путем записи в регистр PAFLG содержимого, в котором соответствующие биты имеют значение 1.

Сигналы PACLK могут использоваться для переключения счетчика-таймера TCNT при установке в регистре PACTL соответствующих значений битов CLK1-0 (табл. 2.26).

Таблица 2.26. Выбор сигналов переключения для счетчика TCNT

Таймерный модуль ЕСТ, используемый в моделях 68НС12ВЕ32, 68HC912D60, 68HC912DG128, а также в моделях семейства 68HCS12 (см. табл. 2.3) является модифицированным вариантом модуля TIM, в структуру которого внесены следующие изменения:

введены четыре 16-разрядных буферных регистра ТСхН (х=0, 1, 2 или 3) для промежуточного хранения времени поступления входных сигналов IC3-0;

на входах сигналов захвата IСх (х=0, 1, 2 или 3) включены регистры задержки, которые позволяют исключить срабатывание соответствующих таймерных каналов при поступлении помех;

для счета событий используются четыре 8-разрядных счетчика PACNx (х = 0, 1, 2 или 3), которые могут работать как два 16-разрядных счетчика;

для каждого счетчика событий введен 8-разрядный буферный регистр РАхН (х=0, 1, 2 или 3), обеспечивающий временное хранение содержимого счетчика;

обеспечивается возможность работы буферных регистров захвата ТСхН и счета событий РАхН в режиме очереди или в режиме временного хранения, который реализуется с помощью дополнительного 16-разрядного вычитающего счетчика.

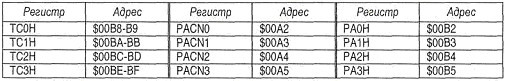

Таблица 2.27. Адреса буферных регистров и счетчиков событий в модуле ЕСТ

Модуль ЕСТ содержит 16-разрядный таймер-счетчик TCNT и восемь таймерных каналов, в каждом из которых имеется 16-разрядный регистр захвата-совпадения ТСх. Работа таймера в модуле ЕСТ контролируется с помощью регистров TIOS, TMSK1,2, TCTL1,2,3,4, TFLG1,2, CFORC, OC7M, OC7D, содержимое и адреса которых такие же, как и в модуле TIM. Каналы с номерами 0-3 имеют дополнительные буферные регистры ТСхН, в которые может переписываться содержимое соответствующих регистров ТСх при работе каналов в режиме захвата. Адреса этих регистров приведены в табл. 2.27. Использование буферных регистров разрешается при значении бита BUFEN=1 в регистре управления ICSYS (рис. 2.30, а). Введен также регистр управления ICOVW (рис. 2.30, б), который содержит биты NOVWi, определяющие возможность записи в регистр TCi в режиме захвата:

при NOVWi=0 разрешается запись нового содержимого в регистр TCi или перезапись в регистр TCiH при поступлении следующего сигнала захвата ICi;

при NOVWi=l запись нового содержимого в регистр TCi или перезапись в регистр TCiH при поступлении следующего сигнала захвата ICi производится только в случае, если эти регистры пустые, т. е. предварительно проведено чтение их содержимого.

Для таймерных каналов 0-3 введен контроль значения сигналов захвата IСх спустя определенное время задержки Td. При этом захват содержимого счетчика TCNT в регистр ТСх происходит, если по истечении времени Td уровень входного сигнала 1Сх оказывается противоположным исходному. Таким образом исключается срабатывание каналов при поступлении импульсов помехи, длительность которых меньше Td. Значение Td задается содержимым регистра DLYCT (рис. 2.30, в).

Допускается совмещение работы каналов 0 и 4, 1 и 5, 2 и 6, З и 7 в режиме захвата. Совмещение реализуется при установке в 1 соответствующего бита SHxy в регистре ICSYS. При этом сигнал захвата IСх, поступающий на вход канала х=0,1,2 или 3, вызывает также захват текущего содержимого счетчика-таймера TCNT в регистр ТСу канала у=4,5,6 или 7. Выводы РТу порта Т могут использоваться в этом случае для ввода-вывода данных.

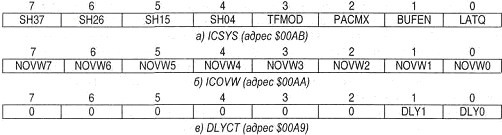

Рис. 2.30. Формат содержимого дополнительных регистров управления таймерным модулем ЕСТ

Дополнительный регистр управления ICSYS содержит следующие биты:

SHxy - обеспечивает при значении SHxy=1 совмещение таймерных каналов х и у, при SHxy=0 соответствующие каналы работают в обычном раздельном режиме;

TFMOD - управляет установкой признаков CF3-0 в регистре TFLG1 при работе каналов 3-0 в режиме захвата: при TFMOD=0 признак CFx устанавливается в 1 при поступлении соответствующего сигнала захвата IСх, при TFMOD=1 и работе каналов 3-0 в режиме очереди (биты BUFEN=1, LATQ=0) признак CFx устанавливается в 1 при перезаписи содержимого регистра ТСх в буферный регистр ТСхН;

РАСМХ - задает режим работы счетчиков событий PACN3-0: при РАСМХ=0 содержимое счетчиков сбрасывается в 0 после достижения максимального значения $FF, при РАСМХ=1 содержимое счетчиков фиксируется при достижении значения $FF;

BUFEN - разрешает при значении BUFEN=1 использование буферных регистров ТСхН для таймерных каналов х=0-3 и буферных регистров РАхН для счетчиков событий PACNx, при BUFEN=0 буферные регистры не используются;

LATQ - определяет режим работы таймерных каналов 0-3 и счетчиков событий PACN3-0 при использовании буферных регистров: режим очереди при LATQ=0, режим временного хранения при LATQ=1.

Регистр DLYCT содержит биты DLY1-0, определяющие значение задержки Td для сигналов IC3-0, вводимой для защиты каналов 3-0 от срабатывания при поступлении помех: Td=0 (обычный режим) при DLY1-0=00, Td=256 Tt при DLY1-0=01, Td=512 Tt при DLY1-0= 10, Td= 1024 Tt при DLY1-0= 11.

При запуске микроконтроллера все биты в регистрах ICSYS, ICOVW, DLYCT принимают значение 0. При дальнейшей работе допускается однократная запись в регистр ICSYS и любые виды обращения к регистрам ICOVW, DLYCT.

При использовании буферных регистров ТСхН (бит BUFEN=1 в регистре ICSYS) таймерные каналы 0-3 могут работать в режиме очереди или временного хранения.

В режиме очереди (бит LATQ=0) при поступлении сигнала IСх содержимое регистра ТСх переписывается в соответствующий буферный регистр ТСхН, а в ТСх заносится текущее содержимое счетчика TCNT. Если при этом в регистре ICOVW соответствующий бит NOVWx=1, то запись в ТСх и перезапись в ТСхН производятся, когда данные регистры пустые.

В режиме временного хранения (бит LATQ=1) перезапись содержимого ТСх в буферный регистр ТСхН выполняется после определенного интервала времени Th, который задается с помощью специального 16-разрядного вычитающего счетчика MCCNT (адрес $00B6-B7). Если в регистре ICOVW соответствующий бит NOVWx=0, то при поступлении сигнала IСх разрешается захват нового содержимого в регистр ТСх и его последующая перезапись в ТСхН спустя время Th. При значении бита NOVWx=1 захват содержимого в ТСх и перезапись в ТСхН производится, если эти регистры пустые.

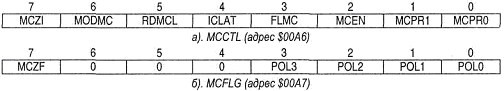

Вычитающий счетчик MCCNT работает под управлением регистра MCCTL (рис. 2.31, а), биты которого имеют следующее назначение:

MCZI - при MCZI=1 разрешает прерывание, когда содержимое MCCNT становится равным $0000 (устанавливается признак MCZF=1 в регистре MCFLG);

MODMC - определяет режим работы счетчика: при MODMC=0 - однократный обратный счет от записанного в MCCNT начального значения до $0000, при MODMC=1 - многократный счет с загрузкой при достижении $0000 начального значения и повторением обратного счета;

RDMCL - указывает, какое содержимое счетчика MCNT будет получено при его чтении: текущее содержимое при RDMCL=0, начальное значение при RDMCL=1;

ICLAT - установка значения ICLAT=1 вызывает в режиме очереди (биты BUFEN=LATQ=1) перезапись содержимого регистров ТСх и PACNx в буферные регистры ТСхН и РАхН;

FLMC - установка значения FLMC=1 вызывает при MCEN=1 загрузку в MCCNT ранее записанного начального значения (возврат счетчика в исходное состояние);

MCEN - разрешает при установке значения MCEN=1 работу счетчика MCNT;

MCPR1-0 - задает частоту переключения Fm счетчика MCNT: Fm=Ft при MCPR=00, Fm=Ft/4 при MCPR=01, Fm=Ft/8 при MCPR=10, Fm=Ft/16 при MCPR=11.

Когда содержимое MCCNT становится равным $0000, содержимое регистров ТСх и счетчиков событий PACNx при работе каналов 3-0 в режиме временного хранения (биты BUFEN=1, LATQ=0) переписывается в соответствующие буферные регистры ТСхН и РАхН. При этом формируется запрос прерывания с обращением к вектору, расположенному по адресу $FFCC-CA (см. 2.1.3). Счетчик MCCNT может также использоваться для реализации периодических прерываний.

Регистр MCFLG (рис. 2.31, б) содержит признак MCZF, который принимает значение 1, когда содержимое регистра MCCNT становится равным $0000, и признаки POLx, которые указывают, какой сигнал IСх вызвал первый захват в канале х=0,1,2 или 3: значение POLx=0 показывает, что захват был вызван отрицательным перепадом потенциала, значение POLx=l - положительным перепадом. Содержимое регистра MCFLG доступно только для считывания. Сброс в 0 признака MCZF производится путем записи 1 в соответствующий бит этого регистра.

Рис. 2.31. Формат содержимого регистров вычитающего счетчика

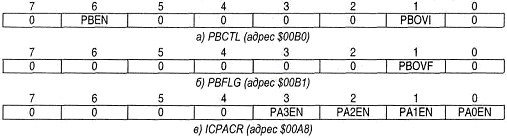

Таймерный модуль ЕСТ содержит четыре 8-разрядных счетчика событий PACN3-0, которые могут выполнять счет сигналов, поступающих на входы РТЗ-0 порта Т, или объединяться в 16-разрядные счетчики РАСА, РАСВ. Управление работой счетчиков производится с помощью регистров PACTL, PAFLG (см. рис. 2.29) и дополнительных регистров PBCTL, PBFLG, ICPACR (рис. 2.32).

Если в регистре PACTL установлено значение бита PAEN=1, то счетчики PCN3 и PACN2 объединяются в 16-разрядный счетчик РАСА, который функционирует аналогично счетчику событий в модуле TIM. Его работа определяется содержимым регистров PACTL, PAFLG.

Если в регистре PBCTL (рис. 2.32, а) установлено значение бита PBEN=1, то счетчики PCN1 и PACN0 объединяются в 16-разрядный счетчик РАСВ, который осуществляет счет сигналов, поступающих на вывод PT0 порта Т. При этом вид сигналов, переключающих счетчик, определяется значениями битов EDG0B, EDG0A в регистре TCTL4 (рис. 2.26, г) в соответствии с табл. 1.71. В регистре PBFLG (рис. 2.32, б) устанавливается значение признака PBOVF=1, когда содержимое счетчика РАСВ изменяется с $FFFF на $0000 (переполнение счетчика). В этом случае формируется запрос прерывания с обращением к вектору по адресу $FFCA-CB, если в регистре PBCTL значение бита разрешения прерывания PBOVI=1. Содержимое регистра PBFLG доступно только для чтения, а для сброса в 0 признака PBOVF требуется записать 1 в соответствующий бит этого регистра.

Рис. 2.32. Формат содержимого дополнительных регистров управления счетчиками событий в таймерном модуле ЕСТ

Если биты PAEN, PBEN имеют значение 0, то режим работы счетчиков PACNx определяется битами PAxEN в регистре ICPACR (рис. 2.32, в). Если PAxEN=0, то счетчик PACNx отключается и соответствующие выводы РТЗ-0 могут использоваться для передачи данных через порт Т с помощью регистров PORTT, DDRT. Если PAxEN=1, то счетчик PACNx выполняет счет сигналов, поступающих на соответствующий вывод РТх порта Т. Вид сигналов, переключающих счетчики PACNx, определяется значениями битов EDGxB, EDGxA в регистре TCTL4 (рис. 2.26, г) в соответствии с табл. 1.71.

Если в регистре ICSYS (рис. 2.30, а) установлено значение бита BUFEN=1, то для сохранения содержимого счетчиков PACNx используются буферные регистры РАхН. Бит LATQ в регистре ICSYS задает условия перезаписи содержимого PACNx в РАхН: при значении LATQ=0 перезапись производится, когда в вычитающем счетчике MCCNT установится $0000, при LATQ=1 содержимое PACNx загружается в буферный регистр РАхН после чтения из этого регистра. После перезаписи счетчик PACNx сбрасывается в нулевое состояние.

Отметим, что при использовании выводов РТЗ-0 для подачи сигналов, переключающих счетчики PACN3-0, значения битов DLY1-0 в регистре DLYCT (рис. 2.30, в) задают значение задержки срабатывания счетчиков Td. Таким образом можно предотвратить переключение счетчиков при поступлении на эти входы импульсных помех.

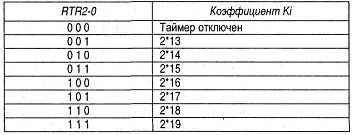

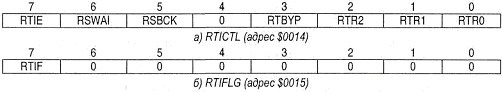

Таймер периодических прерываний PIT. Этот таймер входит в состав модуля интеграции LIM и служит для формирования запроса прерывания через промежутки времени Ti = Tt x Ki, где Ki - заданный коэффициент деления тактовой частоты (табл. 2.28). Работой таймера PIT управляет регистр RTICTL (рис. 2.33, а), отдельные биты которого имеют следующее назначение:

RTIE - разрешает при значении RTIE=1 формирование запроса прерывания по сигналу таймера периодических прерываний;

RSWAI - останавливает при значении RSWAI=1 работу таймера периодических прерываний и блока контроля функционирования в режиме ожидания;

RSBCK - останавливает при значении RSBCK=1 работу таймера периодических прерываний и блока контроля функционирования в режиме отладки BDM;

RTBYP - используется при тестировании таймера (рабочем режиме RTBYP=0);

RTR2-0 - задают значения коэффициента Ki в соответствии с табл. 2.28 (при значении RTR2-0 = 000 таймер выключается).

Таблица 2.28. Значения коэффициента Ki для таймера периодических прерываний

После запуска микроконтроллера все биты этого регистра принимают значение 0. При дальнейшей работе биты RSWAI, RSBCK допускают только однократную запись, а биты RTIE, RTR2-0 постоянно доступны для записи и чтения.

Таймер PIT срабатывает через каждый промежуток времени Ti. При его срабатывании в регистре RTIFLG (рис. 2.33, 6) устанавливается значение признака RTIF=1. Если в регистре RTCTL значение бита RTIE=1, то формируется запрос прерывания с обращением к вектору с адресом $FFF0-F1 (см. 2.1.3). Сброс в 0 признака RTIF производится путем записи 1 в соответствующий бит регистра RTIFLG.

Рис. 2.33. Формат содержимого регистров RTICTL, RTIFLG таймера периодических прерываний PIT

Модуль формирования ШИМ-сигналов. В дополнение к возможностям генерации ШИМ-сигнала с помощью таймерного модуля TIM или ЕСТ в микроконтроллерах имеется отдельный модуль PWM для формирования ШИМ-сигналов. Выходы каналов этого модуля совмещены с выводами РР3-0 порта Р. Выводы PP7-4 этого порта, а также выводы РР3-0, неиспользуемые модулем PWM, могут служить для обмена данными с помощью регистров PORTP, DDRP (см. 2.1.7).

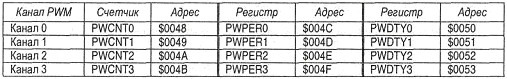

Модуль PWM обеспечивает работу двух выходных каналов с 16-разрядной модуляцией ШИМ-сигналов (65 536 значений скважности формируемых импульсов) или четырех каналов с 8-разрядной модуляцией (256 значений скважности импульсов). В микроконтроллерах семейства 68HCS12 число каналов модуля PWM вдвое увеличено (см. табл. 2.3). Возможны комбинации сигналов с 16- и 8-разрядной модуляцией. Каналы имеют отдельные счетчики PWCNTx и регистры настройки PWPERx, PWDTYx (табл. 2.29), что позволяет независимо программировать частоту и длительность их выходных импульсов.

Таблица 2.29. Адреса счетчиков и регистров настройки каналов модуля PWM

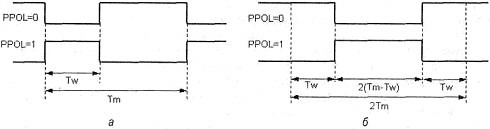

Каждый канал х=0, 1, 2 и 3 содержит 8-разрядный счетчик PWCNTx, который переключается сигналами, поступающими от схемы тактирования, и 8-разрядные регистры PWPERx, задающий период формируемых ШИМ-сигналов, и PWDTYx, определяющий длительность импульса. Получаемые на выходе каналов ШИМ-сигналы имеют смещенную (рис. 2.34, а) или центрированную (рис. 2.34, б) форму в зависимости от значения бита CENTR в регистре управления PWCTL (рис. 2.35, г). Полярность формируемых импульсов задается для каждого канала значением бита PPOLx в регистре PWPOL (рис. 2.35, б). Выбор сигнала тактирования для каждого канала определяется значением бита PCLKx в регистре PWPOL. При смещенной форме (бит CENTR=0) период импульсов составляет Tm=M/Fp, длительность Tw=W/Fp, где Fp - частота сигналов тактирования PWCNTx, М и Р - числа, записанные в регистрах PWPERx и PWDTYx соответственно. При центрированной форме (бит CENTR=1) период импульсов составляет 2Tm, а длительность 2(Tm-Tw). Таким образом, программирование параметров формируемых ШИМ-сигналов производится путем записи необходимых чисел М, W в регистры PWPERx, PWDTYx. Содержимое счетчиков PWCNTx доступно только для чтения, а запись в них вызовет сброс в нулевое состояние (перезапуск счетчика).

Рис. 2.34. Вид ШИМ-сигналов смещенной (а) и центрированной (б) формы

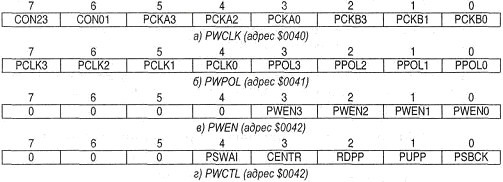

Если в регистре PWCLK (рис. 2.35, а) бит CON23 или CON01 установлен в 1, то счетчики PWCNTx и регистры PWPERx, PWDTYx соответствующей пары каналов 2 и 3 или 0 и 1 объединяются, образуя 16-разрядные счетчики и регистры. При значении CON23=1 пары регистров PWPER2-3, PWDTY2-3 задают период и длительность ШИМ-сигналов на выводе РР2, полярность импульсов определяется значением бита PPOL2, а бит PCLK3 выбирает сигнал тактирования для 16-разрядного счетчика PWCNT2-3. При значении CON01=1 пары регистров PWPER0-1, PWDTY0-1 задают параметры ШИМ-сигналов на выводе РР0, полярность которых определяется значением бита PPOL0, а бит PCLK1 выбирает сигнал тактирования для счетчика PWCNT0-1.

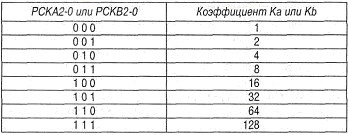

Схема тактирования состоит из 7-разрядного счетчика-делителя частоты PWPRES (адрес $0043), содержимое которого доступно только для чтения. Сигналы ClockA и ClockB с выходов этого делителя используются для тактирования счетчиков PWCNT0,l и PWCNT3,2 соответственно. Эти сигналы имеют частоту Fca=Ft/Ka, Fcb=Ft/Kb, где значения коэффициентов Ка, Kb задаются битами РСКА2-0, РСКВ2-0 в регистре PWCLK.

Для дополнительного деления частоты сигналов ClockA, ClockB служат 8-разрядные регистры PWSCAL0, PWSCAL1 (адреса $0044, $0046), содержимое которых задает коэффициент деления, и счетчики PWSCNT0, PWSCNT1 (адреса $0045, $0047, доступны только для чтения), на выходах которых формируются сигналы тактирования S0 и S1, имеющие пониженную частоту. Пара PWSCAL0-PWSCNT0 обеспечивает получение сигналов S0, имеющих частоту Fs0=Fca/2Ks0, где коэффициент деления частоты Ks0 задается содержимым PWSCAL0 (при содержимом $00 значение Ks0=256). Аналогичным образом пара PWSCAL1-PWSCNT1 формирует сигналы S1, имеющие частоту Fs1=Fcb/2Ks2, где значение Ks1 задается содержимым PWSCAL1.

Рис. 2.35. Формат содержимого регистров управления модулем PWM

Регистры управления PWCLK, PWPOL (рис. 2.35, а, б) содержат следующие биты:

CON23, CON01 - задают режим работы каналов PWM: отдельные 8-разрядные каналы при значениях CON23=0, CON01=0, объединение каналов 3 и 2 в 16-разрядный канал при CON23=1, объединение каналов 1 и 0 в 16-разрядный канал при CON01=1;

РСКА2-0, РСКВ2-0 - определяют значения коэффициентов деления частоты Ка, Kb при формировании сигналов тактирования ClockA, ClockB (табл. 2.30);

PCLK3,2 - определяют выбор сигнала тактирования для каналов 3 и 2: ClockB при значении PCLKx=0, S1 при значении PCLKx=1;

PCLK1,0 - определяют выбор сигнала тактирования для каналов 1 и 0: ClockA при значении PCLKx=0, S0 при значении PCLKx=1;

PPOL3-0 - задают полярность сигналов, формируемых на выходе соответствующих каналов: положительная при PPOLx=1, отрицательная при PPOLx=0 (см. рис. 2.34).

Таблица 2.30. Значения коэффициентов деления Ка, Kb

Биты PWEN3-0 в регистре PWEN (рис. 2.35, в) разрешают при значении PWENx=1 работу соответствующего канала PWM. Биты в регистре PWCTL (рис. 2.35, г) имеют следующее назначение:

PSWAI - разрешает при значении PSWAI=1 работу модуля PWM, когда микроконтроллер находится в режиме ожидания;

CENTR - задает форму ШИМ-сигналов на выходах каналов: смещенная (рис. 2.34, а) при значении CENTR=0, центрированная (рис. 2.34, б) при значении CENTR=1;

PSBCK - разрешает при значении PSDCK=1 работу модуля PWM, когда микроконтроллер находится в режиме отладки BDM.

В регистре PWCTL содержатся также бит PUPP, который при PUPP=1 вызывает подключение ко всем выводам порта Р резисторов, «подтягивающих» их потенциал к напряжению питания, и бит RDPP, который при RDPP=1 обеспечивает для выходов этого порта пониженные значения выходных токов (см. 2.1.7).