- •Теория микропроцессорных систем микроконтроллеры

- •Структура и функциональные возможности мк51

- •Электрический интерфейс мк51

- •Резидентная память данных

- •Работа блока управления и синхронизации

- •Элементы данных в мк51

- •Характеристика функциональных групп команд

- •2.5. Система команд семейства mcs-51.

- •2.5.1. Команды пересылки данных.

- •Команда обработки данных.

- •Команды передачи управления.

- •Характеристика периферийных блоков в составе мк51

- •Управление таймерами-счетчиками (т/с)

- •Описание вариантов конфигурации таймеров-счетчиков

- •Особенности реализации временных интервалов

- •Структура последовательного порта и принципы управления

- •Описание режимов работы уапп

- •Назначение и принципы функционирования системы прерываний

- •Управление приоритетами запросов прерываний

- •Работа системы обслуживания прерываний

- •Заполнение начальной области памяти программ

- •Шестнадцатиразрядные микроконтроллеры Motorola

- •Современные встраиваемые микроконтроллеры, выпускаемые производственной фирмой Freescale Semiconductor

- •Номенклатура и функциональный состав микроконтроллеров cемейства 68hcs12

- •2.1. Микроконтроллеры семейства 68нс12/912

- •2.1.3. Начальный запуск и обработка прерываний

- •2.1.4. Режимы работы и конфигурация микроконтроллеров

- •2.1.5. Функционирование и программирование Flash-памяти и эсппзу

- •2.1.6. Блок контроля функционирования и генератор тактовых импульсов

- •2.1.7. Параллельный ввод-вывод данных и подключение внешней памяти

- •2.1.8. Последовательные порты sci и spi

- •2.1.9. Таймерные модули и широтно-импульсные модуляторы

- •2.1.10. Модуль аналого-цифрового преобразователя atd

- •2.1.11. Модуль последовательного интерфейса msCan

- •2.1.12. Режим отладки bdm и установка контрольных точек

2.1.8. Последовательные порты sci и spi

Для организации последовательного обмена в состав микроконтроллеров семейства 68НС12/912 включен модуль последовательного интерфейса, который содержит 1 или 2 порта асинхронного обмена SCI и порт синхронного обмена SPI. В состав этого модуля входит 8-разрядный порт S, отдельные линии которого обеспечивают последовательный обмен через порты SCI, SPI, и линии, не используемые этими портами, могут служить для параллельного ввода-вывода данных (см. 2.1.7).

Асинхронный последовательный порт SCI функционирует в основном аналогично порту SCI в 8-разрядных микроконтроллерах (см. 1.1.9, 1.2.10), однако имеет некоторые особенности в реализации режимов работы. Соответственно есть определенные отличия и в содержимом регистров порта.

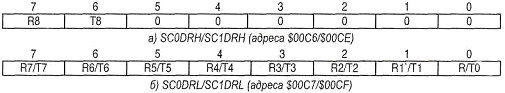

Микроконтроллеры 68НС812А4, 68HC912D60, 68HC912DG128 содержат два порта SCI-0, SCI-1, в микроконтроллерах 68НС912В32, 68НС912ВС32 - один порт SCI-0. Каждый порт имеет два регистра данных SCxDRH, SCxDRL, где символ х=0 или 1 указывает номер порта (если микроконтроллер содержит только один порт SCI, то он имеет номер 0). В регистре SCxDRL (рис. 2.19, а) хранятся 8 информационных бит, поступивших с приемник с вывода RxD (биты R7-0) или выдаваемых передатчиком на вывод TxD (биты Т7-0). Регистр SCxDRH (рис. 2.19, 6) содержит бит R8, который принимает значение 9-го (контрольного) бита, поступающего на вход RxD приемника при 11-битовом кадре принимаемых данных, и бит Т8, который выдается на выход TxD передатчика в качестве 9-го (контрольного) бита при 11-битовом кадре пересылаемых данных.

Рис. 2.19. Формат содержимого регистров данных порта SCI

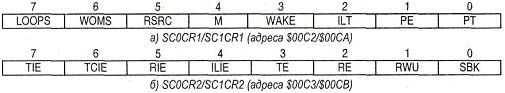

Порт SCI имеет два регистра управления SCxCR0, SCxCR1 (символ х=0 или 1 в зависимости от номера порта). В регистре SCxCRl (рис. 2.20, а) содержатся биты, имеющие следующее назначение:

LOOPS - при установке значения LOOPS=1 переводит порт SCI в режим кольцевого обмена или однопроводного обмена; при этом режим работы порта определяется значениями бита RSRC и бита направления передачи DDRSi, установленного в регистре DDRS для вывода PSi порта S, где i соответствует номеру вывода, к которому подключен выход передатчика TxD (табл. 2.21);

WOMS - при установке значения WOMS=1 обеспечивает работу выходных каскадов на выводах RxD, TxD в режиме с «открытым стоком» (для реализации операции «Монтажное ИЛИ»);

RSRC - при значении LOOPS=1 бит RSRC определяет подключение входа приемника: если RSRC=0, то вход приемника соединяется с выходом передатчика (кольцевой обмен), если RSRC=1, то вход приемника подключается к выводу TxD, реализуя однопроводной режим обмена (табл. 2.21);

М - задает формат пересылаемого кадра данных: 10-битовый при М=0 (отсутствие контрольного бита), 11-битовый при М=1 (наличие контрольного бита);

WAKE - определяет способ выхода приемника из режима ожидания: прием символа IDLE (10 или 11 единичных бит) при WAKE=0, единичное значение последнего принятого бита данных R7 (при М=0) или R8 (при М=1) при WAKE=1;

ILT - указывает начало отсчета единичных битов, представляющих символ ожидания IDLE: начиная с очередного старт-бита при ILT=0 или с очередного стоп-бита при ILT=1;

РЕ - разрешает при установке значения РЕ=1 контроль четности при передаче и приеме данных;

РТ - определяет вид контроля: если РТ=0, то контрольный бит равен 1 при четном числе информационных битов (контроль четности), если РТ=1, то контрольный бит равен 1 при нечетном числе информационных битов (контроль нечетности).

Рис. 2.20. Формат содержимого регистров управления портом SCI

Значения битов LOOPS, WOMS, RSRC и DDRSi (i=l для порта SCI0 - его выход TxD подключен к выводу PS1, i=3 для порта SCI1 - его выход TxD подключен к выводу PS3) определяют режим работы порта (табл. 2.21). При нормальном режиме вывод TxD служит для передачи данных, вывод RxD - для приема. В кольцевом режиме, который обычно используется для контроля правильности работы порта SCI, приемник всегда получает данные, посылаемые передатчиком. При этом они могут выводиться (при DDRSi=l) или не выводиться (при DDRSi=0) на выход TxD (вывод PS1 или PS3). В однопроводном режиме линия, подключенная к TxD, служит как для передачи, так и для приема данных.

Регистр управления SCxCR2 (рис. 2.20, б) содержит следующие биты:

TDE - разрешает при значении ТIЕ=1 формирование запроса прерывания при установке признака освобождения регистров SCxDRH, SCxDRL от данных, направленных в передатчик (в регистре SCxSR1 признак TDRE=1);

TCIE - разрешает при значении ТСIЕ=1 формирование запроса прерывания при установке признака завершения передачи (в регистре SCxSR1 признак ТС=1);

RIE - разрешает при значении RIE=1 формирование запроса прерывания при заполнении регистра данных приемника (в регистре SCxSR1 признак RDRF=1);

Таблица 2.21. Режимы работы порта SCI

ILIE - разрешает при значении ILIE=1 формирование запроса прерывания при поступлении на вход RxD символа ожидания IDLE (в регистре SCxSR1 признак IDLE=1);

ТЕ - включает (при ТЕ=1) и отключает (при ТЕ=0) передатчик;

RE - включает (при RE=1) и отключает (при RE=0) приемник;

RWU - переводит при RWU=1 приемник в режим ожидания, а при RWU-0 разрешает активизацию приемника (в соответствии со значением бита WAKE в регистре SCxCR1);

SBK - вызывает при установке SBK=1 выдачу на выход TxD передатчика символа прекращения обмена BREAK (последовательность 0).

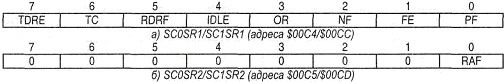

Регистры состояния SCxSR1, SCxSR2 содержат признаки, которые устанавливаются в процессе приема и передачи данных. При запуске микроконтроллера все признаки принимают значение 0. В регистре SCxSR1 (рис. 2.21, а) содержатся следующие признаки:

TDRE - признак готовности передатчика к приему новых данных, принимает значение TDRE=1 после того, как содержимое регистров данных SCxDRH, SCxDRL переписывается в сдвиговый регистр передатчика для выдачи на выход TxD;

ТС - признак окончания передачи, принимает значение ТС=1 после выдачи последнего бита данных из сдвигового регистра передатчика на выход TxD;

RDRF - признак заполнения приемника, принимает значение RDRF=1 после того, как данные, поступившие со входа RxD в сдвиговый регистр приемника, переписываются в регистры SCxDRH, SCxDRL;

IDLE - признак поступления символа ожидания IDLE, принимает значение IDLE=1, если состояние 1 на входе RxD поддерживается более 10 (при М=0) или 11 (при М=1) тактов синхронизации обмена Ts;

OR - признак переполнения приемника, принимает значение OR=1 в случае, когда очередной символ поступает в сдвиговый регистр приемника до считывания из регистров SCxDRH, SCxDRL предыдущего символа (при этом содержимое регистров сохраняется, а очередной поступивший символ теряется);

NF - признак наличия шумов на линии приема, устанавливается в состояние NF=1, если в процессе приема какого-либо бита зафиксированы изменения уровня сигнала на входе RxD;

FЕ - признак нарушения кадра, принимает значение FE=1, если в принятом кадре длительность стоп-бита оказывается меньше, чем длительность такта синхронизации Ts;

PF - признак ошибки четности, принимает значение PF=1, если четность принятых информационных битов R7-0 не соответствует поступившему значению контрольного бита R8.

Рис. 2.21. Формат содержимого регистров состояния порта SCI

Признаки TDRE, ТС, RDRF, IDLE вызывают формирование запроса прерывания, если это разрешено соответствующими битами в регистре SCxCR2. Соответствующий вектор прерывания располагается по адресу $FFD6-D7 для порта SCI-0 и $FFD4-D5 для порта SCI-1 Запросы, вызванные признаками TDRE, TC, RDRF обычно вызывают процедуры записи в регистры SCxDRH, SCxDRL новых данных для передачи или считывания из них принятых данных. Если соответствующие запросы запрещены установкой нулевого значения битов TIE, TCIE, RIE в регистре SCxCR2, то прием и передача данных через порт SCI выполняются программно с помощью периодического считывания и анализа содержимого SCxSR1 (программный опрос). Значения признаков ошибок OR, NF, FE, PF определяются путем программного опроса.

Содержимое регистра SCxSRl доступно только для считывания. Установка в 0 значений признаков RDRF, IDLE, OR, NF, FE, PF производится при чтении содержимого регистра SCxSRl и последующем чтении содержимого регистра данных SCxDRL. Признаки TDRE, ТС принимают значение 0 после чтения содержимого SCxSRl и записи данных в регистр SCxDRL.

Регистр состояния SCxSR2 (рис. 2.21, б) содержит только признак активизации приемника RAF, который принимает значение RAF=1 после приема старт-бита. Содержимое данного регистра доступно только для чтения. Установка значения RAF=0 происходит при поступлении символа ожидания IDLE или при запуске микроконтроллера.

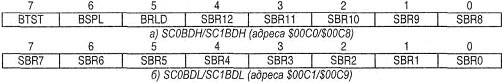

Длительность такта обмена Ts = 1/Fs определяется частотой Fs импульсов, формируемых генератором синхросигналов (ГСС). Значение этой частоты определяется выражением Fs = Ft/16Ks, где значение коэффициента деления Ks задается битами SBR12-0 в регистрах SCxBDH, SCxBDL (рис. 2.22). Биты BTST, BSPL, BRLD используются при тестировании микроконтроллера. При запуске микроконтроллера устанавливается значение бита SBR2=1, остальные биты в SCxBDH, SCxBDL принимают значение 0, т. е. обеспечивается скорость обмена Fs=Ft/64. Путем выбора различных значений коэффициента Ks реализуются скорости последовательного обмена данными в диапазоне от десятков бит в секунду до сотен килобит в секунду. Установка значения Ks=0 вызывает выключение ГСС.

Рис. 2.22. Формат содержимого регистров управления скоростью обмена порта SCI

Синхронный последовательный порт SPI в микроконтроллерах семейства 68НС12/912 функционирует в основном аналогично порту SPI в семействе 68НС05/705 (см. 1.1.10). Обмен данными производится между портами SPI (см. рис. 1.18), один из которых является ведущим (master), а другие - ведомыми (slave). В процессе обмена используются выводы PS7-4 порта S, на которые поступают сигналы порта SPI:

SCK (вывод PS6) - выход синхросигнала для ведущего и вход синхросигнала для ведомого порта;

MOSI (вывод PS5) - выход данных для ведущего и вход данных для ведомого порта;

MISО (вывод PS4) - вход данных для ведущего и выход данных для ведомого порта;

SS# (вывод PS7) - вход сигнала выбора ведомого порта SS# =0, для ведущего порта функции этого вывода указаны в табл. 2.22.

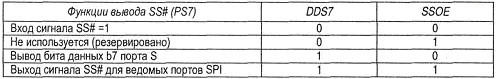

Для выводов порта S, используемых для выхода сигналов порта SPI, необходимо установить соответствующие значения битов DDSi в регистре направления DDRS порта S (см. 2.1.7): DDS5=1 и DDS6=1 для ведущего порта, DDS4=1 для ведомого порта. Функции вывода PS7 для ведущего порта определяются значениями бита SSOE в регистре SP0CR1 и бита DDS7 в регистре DDRS (см. табл. 2.21). Когда этот вывод работает в качестве выхода (DDRS7=1), то при значении бита SSOE=1 он используется для выдачи сигнала SS# =0 для подключенных ведомых портов SPI. При SSOE=0 и DDRS7=1 вывод PS7 служит в качестве выхода для старшего бита данных b7, выдаваемых портом S. При DDRS7=SSOE=0 на вывод PS7 требуется подавать сигнал SS# =1, если порт SPI работает в режиме ведущего (при подаче SS# =0 в регистре SP0SR устанавливается признак ошибки режима MODF=1).

Таблица 2.22. Функции вывода SS# (PS7) ведущего порта SPI

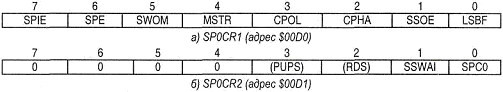

Вводимые и выводимые данные поступают в регистр SP0DR (адрес $00D5). Управление работой порта SPI осуществляется с помощью регистров управления SP0CR1, SP0CR2, формат содержимого которых показан на рис. 2.23.

Отдельные биты в регистре SP0CR1 (рис. 2.23, а) имеют следующее назначение:

SPIE - разрешает при значении SPIE=1 формирование запроса прерывания после окончания приема данных (когда в регистре SP0SR устанавливается признак SPIF=1) или при нарушении режима работы порта (когда в регистре SP0SR устанавливается признак MODF=1);

SPE - разрешает при SPE= 1 или запрещает при SPE-0 работу порта SPI;

SWOM - задает режим работы выходных буферных каскадов на выводах PS7-4: обычный 2-фазный выход при SWOM=0, выход с «открытым стоком» при SWOM=1;

MSTR - устанавливает режим работы порта: в качестве ведущего при MSTR=1, в качестве ведомого при MSTR=0;

CPOL, СРНА - определяют полярность и фазу синхросигналов обмена (см. 1.1.10);

SSOE - определяет функции вывода SS# (PS7) ведущего порта (см. табл. 2.21);

LSBF - задает порядок передачи битов: при LSBF=0 - начиная со старшего бита, при LSBF=1 - начиная с младшего бита.

Рис. 2.23. Формат содержимого регистров управления портом SPI

В регистре управления SP0CR1 содержатся следующие биты:

SSWAI - при установке значения SSWAI=1 останавливает работу порта SPI в режиме ожидания;

SPC0 - определяет включение выводов порта SPI: нормальное включение при SPC0=0, двунаправленное включение (кольцевой режим) при SPC0=l.

При нормальном включении выводы портов соединяются, как показано на рис. 1.18. При двунаправленном включении реализуется кольцевой режим обмена.

Если для ведущего порта SPI установлено значение бита SPC0=1, то выводимые им данные поступают как на вывод PS5 к ведомым портам, так и на вход данных ведущего порта. При этом вывод PS4 (вход данных ведущего), отключается от порта SPI, т. е. данные от ведомого порта не принимаются. Таким образом обеспечивается перезапись выводимых данных в регистр SP0DR ведущего порта.

Если значение бита SPC0=1 установлено для ведомого порта, то данные, выводимые им на вывод PS4, поступают также на его вход данных. При этом вывод PS4 (вход данных ведомого) отключается от этого порта, т. е. данные от ведущего порта не принимаются. В результате выводимые данные последовательно вводятся в регистр SP0DR ведомого порта.

В микроконтроллерах 68НС812А4 бит SSWAI в регистре SP0CR отсутствует. Микроконтроллеры 68HC912DG128 и 68НС812А4 содержат в этом регистре бит PUPS, который при PUPS=1 вызывает подключение ко всем выводам порта S резисторов, «подтягивающих» их потенциал к напряжению питания, и бит RDS, который при RDS=1 обеспечивает для выходов этого порта пониженные значения выходных токов (см. 2.1.7).

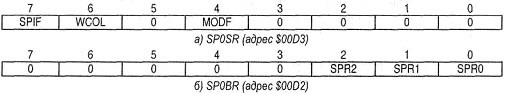

Регистр состояния SP0SR (рис. 2.24, а) содержит следующие признаки, которые автоматически устанавливаются при работе порта:

SPIF - признак завершения приема данных, принимает значение SPIF=1 после пересылки последнего (8-го) бита данных;

WCOL - признак ошибки записи, принимает значение WCOL=1, если процессор пытается выполнить операцию записи в регистр SP0DR в ходе обмена данными через порт SPI (запись при этом не производится);

MODF - признак ошибки режима, принимает значение MODF=1, если на ведущий порт (бит MSTR=1) подан сигнал SS# =0 на вывод PS7, работающий в режиме ввода (биты DDS7=0, SSOE=0, см. табл. 2.22).

Рис. 2.24. Формат содержимого регистра состояния SP0SR (а) и регистра управления скоростью обмена SP0BR (б) порта SPI

Содержимое регистра SPOSR доступно только для чтения. Установка признаков SPIF, WCOL в 0 производится автоматически после чтения содержимого регистра SPOSR и последующего чтения или записи содержимого регистра данных SP0DR. Признак MODF устанавливается в 0 после чтения содержимого SP0SR и последующей записи в регистр управления SP0CR1 (изменения режима работы порта).

Если в регистре SP0CR1 значение бита SPIE=1, то установка битов SPIF=1 или MODF=1 вызовет прерывание с обращением к вектору, расположенному по адресу $FFD8-D9 (см. 2.1.3). Подпрограмма обработки должна определить значение бита WCOL и произвести повторное обращение к порту SPI, если была неудачная попытка записи в его регистр данных (значение WCOL=1).

Время пересылки 1 бита (период синхроимпульсов SCK) равно Tp=1/Fp, где частота синхронизации Fp=Ft/Kp. Коэффициент деления Кр определяется значением битов SPR2-0 в регистре SP0BR (рис. 2.24, б) в соответствии с табл. 2.23.

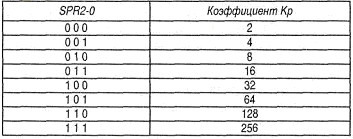

Таблица 2.23. Значения коэффициента деления частоты Кр для порта SPI