- •Теория микропроцессорных систем микроконтроллеры

- •Структура и функциональные возможности мк51

- •Электрический интерфейс мк51

- •Резидентная память данных

- •Работа блока управления и синхронизации

- •Элементы данных в мк51

- •Характеристика функциональных групп команд

- •2.5. Система команд семейства mcs-51.

- •2.5.1. Команды пересылки данных.

- •Команда обработки данных.

- •Команды передачи управления.

- •Характеристика периферийных блоков в составе мк51

- •Управление таймерами-счетчиками (т/с)

- •Описание вариантов конфигурации таймеров-счетчиков

- •Особенности реализации временных интервалов

- •Структура последовательного порта и принципы управления

- •Описание режимов работы уапп

- •Назначение и принципы функционирования системы прерываний

- •Управление приоритетами запросов прерываний

- •Работа системы обслуживания прерываний

- •Заполнение начальной области памяти программ

- •Шестнадцатиразрядные микроконтроллеры Motorola

- •Современные встраиваемые микроконтроллеры, выпускаемые производственной фирмой Freescale Semiconductor

- •Номенклатура и функциональный состав микроконтроллеров cемейства 68hcs12

- •2.1. Микроконтроллеры семейства 68нс12/912

- •2.1.3. Начальный запуск и обработка прерываний

- •2.1.4. Режимы работы и конфигурация микроконтроллеров

- •2.1.5. Функционирование и программирование Flash-памяти и эсппзу

- •2.1.6. Блок контроля функционирования и генератор тактовых импульсов

- •2.1.7. Параллельный ввод-вывод данных и подключение внешней памяти

- •2.1.8. Последовательные порты sci и spi

- •2.1.9. Таймерные модули и широтно-импульсные модуляторы

- •2.1.10. Модуль аналого-цифрового преобразователя atd

- •2.1.11. Модуль последовательного интерфейса msCan

- •2.1.12. Режим отладки bdm и установка контрольных точек

2.1.5. Функционирование и программирование Flash-памяти и эсппзу

Основной объем внутренней памяти микроконтроллеров данного семейства занимает Flash-память и ЭСППЗУ, размещение которых в адресном пространстве определяется соответствующими регистрами конфигурации (см. 2.1.4). В данном разделе рассматриваются особенности их функционирования и программирования.

Flash-память. Большинство микроконтроллеров семейства 68НС12/912 (подсемейство 68НС912) содержит Flash-память объемом до 128 Кбайт, которая организована в виде одного или нескольких сегментов (2 сегмента в модели 68HC912D60, 4 сегмента в модели 68HC912DG128). В исходном состоянии (до записи) содержимое всех ее ячеек равно $FF. Допускается выполнение до 100 циклов стирания-записи содержимого Flash-памяти. Необходимое для этого повышенное напряжение питания Vf = 12 В (±5%) подается на специальный вывод микроконтроллера. В режиме считывания на этом выводе должно быть установлено напряжение питания Vп. В моделях 68HC912D60A, 68HC912DG128A повышенное напряжение для программирования-стирания Flash-памяти обеспечивается с помощью импульсного преобразователя, размещенного на кристалле, поэтому не требуется подключения внешнего источника напряжения Vf.

В конце каждого сегмента Flash-памяти имеется блок, содержимое которого можно защитить от последующего стирания и записи путем установки в 1 бита ВООТР в регистре FEEMCR. Обычно эти блоки служат для хранения программы начальной загрузки. В моделях 68НС912В32, ВС32 данный блок имеет емкость 2 Кбайт и размещается в диапазоне адресов $7800-$7FFF или $F800-$FFFF в зависимости от размещения сегмента Flash-памяти. В моделях 68HC912D60, 68HC912DG128 защищаемые блоки емкостью по 8 Кбайт располагаются в последних адресах сегментов.

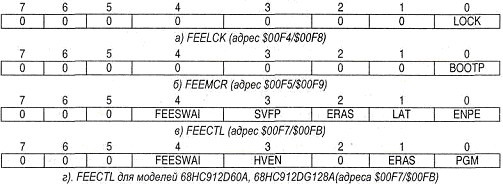

Функционирование каждого из сегментов Flash-памяти определяется содержимым регистров FEELCK, FEEMCR, FEECTL (рис. 2.8). Поэтому микроконтроллеры 68HC912D60, имеющие два сегмента емкостью 28 и 32 Кбайт, используют для управления их работой 3 пары регистров FEELCK28/32, FEEMCR28/32, FEECTL28/32, адреса которых приведены на рис. 2.7. В микроконтроллерах 68HC912DG, содержащих 4 сегмента по 32 Кбайт, имеется 4 набора регистров FEELCK, FEEMCR, FEECTL.

Регистры FEELCK, FEEMCR (рис. 2.8, а, б) содержат по 1 биту, которые имеют следующее назначение:

LOCK - запрещает при значении LOCK=1 запись в регистр FEEMCR;

ВООТР - запрещает при значении ВООТР=1 стирание и запись содержимого в защищаемый блок Flash-памяти.

При запуске микроконтроллера эти биты принимают значения LOCK=0, ВООТР=1. Регистр FEELCK допускает только однократную запись после запуска. Содержимое регистра FEEMCR не может быть изменено, если в регистре FEELCK значение бита LOCK=1 или в регистре FEECTL значение бита ENPE=1.

В регистре FEECTL (рис. 2.8, в) отдельные биты имеют следующее назначение:

FEESWAI - прекращает при значении FEESWAI=1 подачу тактовых импульсов во Flash-память в режиме ожидания;

Рис. 2.8. Формат содержимого регистров FEELCK (a), FEEMCR (б), FEECTL (в,г), определяющих режим работы и программирования Flash-памяти

SVFP - указывает уровень поступающего напряжения программирования Vf (доступен только для чтения): при SVFP=0 значение Vf ниже нормального уровня, при SVFP=1 значение Vf выше нормального уровня;

ERAS - при установке значения ERASE=1 реализуется режим стирания;

LAT - при установке значения LAT=1 разрешает прием адреса и данных при программировании Flash-памяти, при LAT=0 память работает в режиме считывания;

ENPE - при установке значения ENPE=1 разрешает подачу повышенного напряжения для стирания или записи содержимого сегмента Flash-памяти.

После запуска все биты регистра FEECTL принимают значение 0. Изменение значений битов ERAS, LAT возможны только при ENPE=0. Установка значения бита ENPE=1 производится только при LAT=1.

Стирание содержимого сегмента Flash-памяти производится с помощью следующей процедуры:

1. На соответствующий вывод микроконтроллера подается напряжение Vf = 12 В.

2. Устанавливаются значения битов ERASE = LAT = 1 (режим стирания).

3. Производится запись произвольного байта в любую ячейку, находящуюся в стираемом сегменте Flash-памяти.

4. Устанавливается значение бита ENPE=1, что обеспечивает подачу повышенно го напряжения на ячейки Flash-памяти в стираемом сегменте.

5. Реализуется программная задержка длительностью 5-10 мс для стирания содержимого сегмента.

6. Устанавливается значение бита ENPE=0 (отключение повышенного напряжения).

7. Реализуется программная задержка длительностью 1 мс, после которой Flash-память переходит в режим считывания.

8. Производится контрольное считывание, чтобы убедиться в полном стирании содержимого сегмента (содержимое всех ячеек должно быть $FF).

9. Если стирание неполное, то пп. 4-7 повторяются (допускается выполнение до пяти циклов стирания). Если стирание реализовано, то также рекомендуется повторно выполнить указанное количество циклов для обеспечения большей надежности.

10. После завершения циклов стирания устанавливается значение бита LAT=0 и внешнее напряжение Vf снижается до уровня Vп=5 В.

Программирование Flash-памяти производится путем записи байта или слова с помощью следующей процедуры:

1. На соответствующий вывод микроконтроллера подается напряжение Vf = 12 В.

2. Устанавливаются значения битов ERAS=0 и LAT=1 (режим программирования).

3. Производится запись данных (байта или слова) по адресу программируемой ячейки Flash-памяти.

4. Устанавливается значение бита ENPE=1, что обеспечивает подачу повышенного напряжения на программируемую ячейку (запись поступивших данных).

5. Устанавливается значение бита ENPE=0 (отключение повышенного напряжения).

6. Реализуется программная задержка длительностью 20 мкс, после которой Flash-память переходит в режим считывания.

7. Производится контрольное считывание содержимого запрограммированной ячейки, чтобы убедиться в правильности записи (верификация).

8. Если обнаружена ошибка записи, то пп. 4-7 повторяются (допускается выполнение до 50 циклов программирования). Если запись проведена правильно, то также рекомендуется повторить циклы программирования для обеспечения большей надежности.

9. После окончания программирования ячейки устанавливается значение бита LAT=0.

10. При необходимости программирования других ячеек сегмента пп. 2-9 повторяются требуемое количество раз.

11. После завершения программирования всех необходимых ячеек внешнее напряжение Vf снижается до уровня Vп=5 В.

В моделях 68HC912D60A, 68HC912DG128A используется модернизированный вариант Flash-памяти, который не требует внешнего источника повышенного напряжения и имеет более простые алгоритмы стирания и программирования. Сегменты Flash-памяти разбиты на строки размером по 64 байта. Стирание производится для всего сегмента, а программирование осуществляется построчно. Процедуры стирания-программирования реализуются с помощью следующих битов в регистрах FEECTL (рис. 2.8, г):

HVEN - при установке значения HVEN=1 разрешается подача повышенного напряжения для стирания или записи содержимого Flash-памяти;

ERASE - при установке значения ERASE=1 реализуется режим стирания;

PGM - при установке значения PGM=1 реализуется режим программирования.

После запуска микроконтроллера значения этих битов равны 0. Их установка в 1 производится при реализации алгоритмов стирания-программирования. При значениях ERASE=PGM=0 реализуется режим считывания Flash-памяти. Установка значения HVEN=1 разрешается только после задания режима стирания (установка ERASE=1) или программирования (PGM=1). Комбинация значений ERASE=PGM=1 (одновременная реализация стирания и программирования) является запрещенной.

Стирание содержимого сегмента Flash-памяти в микроконтроллерах 68HC912D60A, DG128A производится с помощью следующей процедуры:

1. Устанавливается значение бита стирания ERASE= 1.

2. Производится запись произвольного байта в любую ячейку, находящуюся в стираемом сегменте Flash-памяти.

3. Реализуется программная задержка длительностью 10 мкс.

4. Устанавливается значение бита HVEN=1, что обеспечивает подачу повышенного напряжения на ячейки Flash-памяти в стираемом сегменте.

5. Реализуется программная задержка длительностью 8 мс.

6. Устанавливается значение бита стирания ERASE=0.

7. Реализуется программная задержка длительностью 100 мкс.

8. Устанавливается значение бита HVEN=0 (отключение повышенного напряжения).

9. Реализуется программная задержка длительностью 1 мкс, после которой Flash-память переходит в режим считывания.

Программирование Flash-памяти в этих моделях микроконтроллеров производится путем последовательной записи слов (16-разрядных данных) в пределах одной строки длиной 64 байта. Для этого выполняется следующая процедура:

1. Устанавливается значение бита программирования PGM=1.

2. Производится запись произвольного слова в любую ячейку программируемой строки.

3. Реализуется программная задержка длительностью 10 мкс.

4. Устанавливается значение бита HVEN=1, что обеспечивает подачу повышенного напряжения на ячейки Flash-памяти программируемой строки.

5. Реализуется программная задержка длительностью 5 мкс.

6. Производится запись байта в одну из ячеек программируемой строки.

7. Реализуется программная задержка длительностью 30 мкс.

8. Путем повторения операций 6 и 7 производится запись всех байтов строки.

9. Устанавливается значение бита стирания PGM=0.

10. Реализуется программная задержка длительностью 5 мкс.

11. Устанавливается значение бита HVEN=0 (отключение повышенного напряжения).

12. Реализуется программная задержка длительностью 1 мкс, после которой Flash-память переходит в режим считывания.

Эта процедура выполняется для программирования каждой строки Flash-памяти.

Программирование ЭСППЗУ. Все модели микроконтроллеров семейства 68НС12/912 имеют в своем составе модули ЭСППЗУ емкостью от 768 байт до 4 Кбайт. В исходном (незапрограммированном) состоянии ячейки ЭСППЗУ содержат единичные значения всех битов (число $FF). Микроконтроллер содержит на кристалле импульсный преобразователь, обеспечивающий формирование повышенного напряжения для программирования и стирания ЭСППЗУ. Поэтому данные процедуры производятся без подключения внешнего источника повышенного напряжения под управлением программы, написанной пользователем. Допускается выполнение не менее 10 тыс. циклов стирания-программирования. В моделях 68HC912D60A, 68HC912DG128A имеется возможность выполнять стирание-программирование с автоматической реализацией необходимых задержек с помощью специального внутреннего таймера (режим AUTO).

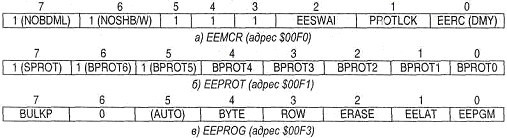

Для управления функционированием ЭСППЗУ служат регистры EEMCR, EEPROT, EEPROG. Регистр EETST ($00F2) используется в процессе тестирования ЭСППЗУ. В рабочем режиме все его биты имеют значение 0.

Регистр управления EEMCR (рис. 2.9, а) содержит следующие биты, общие для всех моделей:

EESWAI - прекращает при значении EESWAI=1 подачу тактовых импульсов в ЭСППЗУ в режиме ожидания;

PROTLCK - запрещает при значении PROTLCK=1 изменение битов защиты BPPROT в регистре EEPROT и бита BULKP в регистре EEPROG;

EERC - включает при значении EERC=1 внутренний RC-генератор для питания импульсного преобразователя, формирующего повышенное напряжение для стирания-программирования (используется при низкой тактовой частоте Ft<l МГц).

Рис. 2.9. Формат содержимого регистров EEMCR (a), EEPROT (б), EEPROG (в), определяющих режим работы и программирования ЭСППЗУ

После запуска микроконтроллера устанавливаются значения EESWAI=1, PROTLCK=EERC=0. При дальнейшей работе допускается только однократное изменение значения бита PROTLCK для установки защиты содержимого регистра EEPROT.

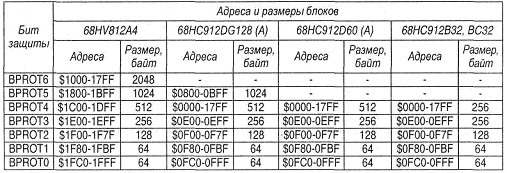

ЭСППЗУ делится на блоки размером от 64 до 1024 байт, которые могут быть защищены от стирания-программирования путем установки значений битов BPROTi в регистре защиты EEPROT (рис. 2.9, б). При значении бита BPROTi=l запрещается выполнение стирания и программирования соответствующего блока ЭСППЗУ. Адреса и размеры блоков для различных моделей микроконтроллеров приведены в табл. 2.16. Количество используемых битов BPROTi зависит от объема ЭСППЗУ в данной модели.

Таблица 2.16. Адреса и размеры защищаемых блоков ЭСППЗУ

Запись и стирание ЭСППЗУ осуществляется программно с помощью регистра EEPROG (рис. 2.9, в), который содержит следующие биты:

BULKP - бит защиты ЭСППЗУ от стирания: при установке значения BULKP=1 запрещает одновременное стирание содержимого всего массива данных или содержимого строк (32 байта);

BYTE - определяет режим стирания содержимого ЭСППЗУ: 1 или 2 байта (слово) при значении BYTE=1, строка (32 байта) или весь массив ЭСППЗУ при BYTE=0;

ROW - при значении BYTE=0 задает вид группового стирания ЭСППЗУ: стирание строки (32 байта) при ROW=1, стирание всего массива ЭСППЗУ при ROW=0;

ERASE - задает режим работы ЭСППЗУ: стирание при значении ERASE=1, программирование или считывание при ERASE=0 (при этом биты BYTE, ROW не влияют на работу ЭСППЗУ);

EELAT - при установке значения EELAT=1 разрешается ввод в ЭСППЗУ адреса программируемой или стираемой ячейки и записываемого в нее содержимого;

EPGM - при установке значения EPGM=1 вызывает подачу напряжения программирования на выбранную ячейку ЭСППЗУ, обеспечивая запись в нее поступивших данных.

После запуска микроконтроллера все биты в регистре EEPROG принимают значение 0. Установка значения BULKP=1 производится только при EEPGM=0 и PROTLCK=0. Запись значения EPGM=1 разрешается только при установленном значении EELAT=1. При значении битов ERASE=EELAT=EPGM=0 реализуется режим считывания ЭСППЗУ.

Стирание содержимого ЭСППЗУ может производиться при установке бита ERASE=1 отдельными байтами или словами (при значении BYTE=1, ROW - любое), построчно (при значении BYTE=0, ROW=1) или сразу всего массива (при значении BYTE=0, ROW=0). Программирование осуществляется путем записи в адресуемую ячейку ЭСППЗУ байта или слова при установке ERASE=0 (биты BYTE, ROW могут иметь любое значение). Процедура стирания-программирования выполняется следующим образом:

1. В регистр EEPROG загружается содержимое, в котором биты BYTE, ROW, ERASE имеют значения, соответствующие выполнению программирования или выбранному способу стирания, устанавливается значение EELAT=1.

2. Выполняется запись данных в ЭСППЗУ - при стирании или программировании байта (слова) запись производится по адресу данного байта (слова), при стирании строки - по адресу любого байта данной строки, при стирании всего массива - по адресу любой ячейки ЭСППЗУ. При стирании записываемые данные могут иметь любое значение, при программировании вводятся необходимые данные.

3. Включается повышенное напряжение стирания-программирования путем установки значения бита EPGM=1 в регистре EEPROG.

4. Реализуется программная задержка длительностью не менее 10 мс.

5. Устанавливается значение бита EEPGM=0 (отключение повышенного напряжения).

6. Устанавливается значение бита EELAT=0 (окончание программирования-стирания).

Если производится программирование или стирание нескольких байт (слов) или строк, то после п. 5 данной процедуры следует перейти к п. 2 и выполнять этот цикл для каждого байта (слова) или строки. После программирования или стирания последнего байта (слова) или строки необходимо установить значение EELAT=0.

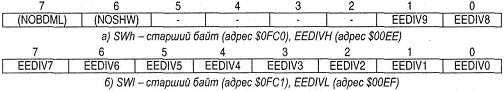

В моделях 68HC912D60A, 68HC912DG128A используется модернизированный вариант ЭСППЗУ, обеспечивающий автоматическое формирование задержек при выполнении стирания-программирования. Для этого используется два дополнительных регистра EEDIVH, L и ячейка ЭСППЗУ (адрес $00EE-EF), в которую заносится управляющее слово SW (Shadow Word), формат которого показан на рис. 2.10. При программировании в эту ячейку заносятся необходимые значения битов NOBDML, NOSHW и EEDIV9-0, которые при запуске микроконтроллера загружаются в регистры EEMCR, EEDIVH, L. В этих моделях регистр EEMCR не содержит бит EERC, так как отсутствует внутренний RC-генератор. Вместо него имеется «холостой» бит DMY (Dummy), который может использоваться разработчиком аппаратуры по своему усмотрению. В регистр введены дополнительные биты (см. рис. 2.8, а):

AUTO - при установке значения AUTO=1 обеспечивает автоматическое формирование необходимых задержек при стирании-программировании (при этом используются регистры EEDIVH, EEDIVL);

NOBDML - запрещает при значении NOBDML=1 отключение режима отладки BDM (см. 2.1.12);

NOSHW - разрешает при значении NOSHW=0 выборку управляющего слова из ячейки с адресом $00EE-EF (при NOSHW=1 по этому адресу размещается обычная ячейка ЭСППЗУ).

Запись SW разрешается при значении бита NOSHW=0 в регистре EEMCR. Последующее стирание-программирование этой ячейки можно запретить, установив значение бита SHPROT=1 в регистре EEPROT (рис. 2.9, б).

Рис. 2.10. Формат содержимого управляющего слова SW и регистров EEDIVH, EEDIVL для микроконтроллеров 68HC912D60A, 68HC912DG128A

Автоматическая реализация необходимых задержек при выполнении стирания-программирования осуществляется с помощью специального внутреннего таймера, рабочая частота которого Fe=Fq/Ke получается путем деления частоты кварцевого резонатора на коэффициент Ке, значение которого задается содержимым регистров EEDIVH, EEDIVL. Для реализации требуемых задержек период переключения этого таймера должен составлять 35±2 мкс, т. е. значение частоты Fe должно быть около 28,6 кГц. Необходимая величина коэффициента Ке определяется с выражением

Ке = [35Fq + 0,5],

где Fq - значение частоты кварцевого резонатора в МГц, величина Ке округляется в сторону уменьшения до ближайшего целого значения. Например, при Fq=16 МГц значение Ке=560 (EEDIV9-0=$0230), при Fq=1 МГц значение Ке=35 (EEDIV9-0 =$0023).

В режиме автоматического формирования задержек (в регистре EECR бит AUTO=1) пп. 4-5 при стирании и программировании ЭСППЗУ исключаются. Бит EEPGM автоматически сбрасывается в 0 после реализации этих операций под управлением внутренней логики. Поэтому программа стирания-программирования после выполнения п. 3 должна контролировать (опрашивать) бит EEPGM и при значении EEPGM=0 произвести установку бита EELAT в 0 (п. 6).