- •Теория микропроцессорных систем микроконтроллеры

- •Структура и функциональные возможности мк51

- •Электрический интерфейс мк51

- •Резидентная память данных

- •Работа блока управления и синхронизации

- •Элементы данных в мк51

- •Характеристика функциональных групп команд

- •2.5. Система команд семейства mcs-51.

- •2.5.1. Команды пересылки данных.

- •Команда обработки данных.

- •Команды передачи управления.

- •Характеристика периферийных блоков в составе мк51

- •Управление таймерами-счетчиками (т/с)

- •Описание вариантов конфигурации таймеров-счетчиков

- •Особенности реализации временных интервалов

- •Структура последовательного порта и принципы управления

- •Описание режимов работы уапп

- •Назначение и принципы функционирования системы прерываний

- •Управление приоритетами запросов прерываний

- •Работа системы обслуживания прерываний

- •Заполнение начальной области памяти программ

- •Шестнадцатиразрядные микроконтроллеры Motorola

- •Современные встраиваемые микроконтроллеры, выпускаемые производственной фирмой Freescale Semiconductor

- •Номенклатура и функциональный состав микроконтроллеров cемейства 68hcs12

- •2.1. Микроконтроллеры семейства 68нс12/912

- •2.1.3. Начальный запуск и обработка прерываний

- •2.1.4. Режимы работы и конфигурация микроконтроллеров

- •2.1.5. Функционирование и программирование Flash-памяти и эсппзу

- •2.1.6. Блок контроля функционирования и генератор тактовых импульсов

- •2.1.7. Параллельный ввод-вывод данных и подключение внешней памяти

- •2.1.8. Последовательные порты sci и spi

- •2.1.9. Таймерные модули и широтно-импульсные модуляторы

- •2.1.10. Модуль аналого-цифрового преобразователя atd

- •2.1.11. Модуль последовательного интерфейса msCan

- •2.1.12. Режим отладки bdm и установка контрольных точек

2.1.4. Режимы работы и конфигурация микроконтроллеров

Микроконтроллеры семейства 68НС12/912 функционируют в одном из семи возможных режимов (табл. 2.15), которые задаются значениями внешних сигналов, поступающих на входы BKGD, MODB, MODA при запуске. При этом устанавливается соответствующее значение битов в регистре режима MODE (рис. 2.4).

![]()

Рис. 2,4. Формат содержимого регистра режима MODE (адрес $000В)

Рабочие режимы обеспечивают функционирование микроконтроллера с использованием только внутренней памяти (автономный режим) или с подключением к портам А, В внешней памяти (расширенные режимы с 8- или 16-разрядной системной шиной). Все модели, кроме 68НС812А4, в расширенном режиме используют мультиплексированную шину адресов-данных. При 16-разрядной шине выводы портов А и В служат для передачи 16 разрядов адреса и данных A/D15-0. При 8-разрядной шине 16 разрядов адреса А15-0 поступают на выводы портов А и В, а пересылка байта данных D7-0 осуществляется через порт А. Ряд выводов порта Е используется в расширенных режимах для передачи сигналов управления обменом по шине.

Специальные режимы используются для тестирования микроконтроллеров в процессе их производства и реализации ряда функций отладки систем. Например, в специальном периферийном режиме отключается процессор микроконтроллера, а все периферийные модули работают под внешним управлением. Таким образом обеспечивается их раздельное тестирование. Специальный автономный режим можно использовать для перевода микроконтроллера в режим отладки BDM, реализация которого описана в 2.1.12.

Регистр MODE (рис. 2.4) содержит следующие биты, определяющие режим работы микроконтроллера:

SMODN, MODA, MODB - задают режим функционирования микроконтроллера в соответствии с табл 2.14;

ESTR - в расширенном режиме всегда устанавливается ESTR=1, обеспечивая выдачу тактовых сигналов ECLK для синхронизации обмена по системной шине; в автономном режиме при ESTR=0 на вывод ECLK поступают сигналы тактовой частоты, а при ESTR=1 на этом выводе устанавливается уровень 0;

Таблица 2.15. Режимы функционирования микроконтроллеров семейства 68НС12/912

IVIS - в автономном режиме этот бит не влияет на работу микроконтроллера; в расширенном режиме установка IVIS=1 разрешает выдачу на системную шину адреса, данных и управляющих сигналов R/W#, LSTRB# при обращении к внутренней памяти, при IVIS=0 адреса, данные и управляющие сигналы выдаются только при обращении к внешней памяти;

EBSWAI - при значении бита EBSWAI=0 разрешается продолжение функционирования интерфейса с системной шиной при переходе в режим ожидания до окончания начатых циклов обмена;

ЕМЕ - при значении бита ЕМЕ=1 запрещается обращение к регистрам порта Е в расширенном режиме, вместо них выбирается содержимое ячеек внешней памяти, имеющих адреса этих регистров.

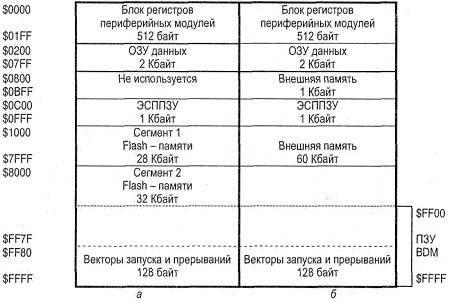

Рис. 2.5. Конфигурация памяти микроконтроллера 68HC912D60 в автономном (а) и расширенном (б) режимах (адресация после запуска микроконтроллера)

В модели 68НС812А4 регистр MODE не содержит бита EBSWI, а имеет бит EMD, используемый в одном из специальных режимов.

После запуска микроконтроллера в регистр MODE можно произвести только однократную запись, устанавливающую необходимые значения управляющих битов. Последующие изменения битов можно осуществить только после повторного запуска.

На рис. 2.5 показана конфигурация памяти микроконтроллера 68HC912D60 в автономном и расширенном режимах. В общем адресном пространстве размещаются следующие виды памяти:

ПЗУ для режима BDM (при работе в этом режиме) - приоритет 1 (высший);

блок регистров периферийных модулей - приоритет 2;

ОЗУ данных - приоритет 3;

ЭСППЗУ - приоритет 4;

Flash-память - приоритет 5;

внешняя память - приоритет 6 (низший).

Если при размещении в адресном пространстве различные виды памяти имеют одинаковые адреса, то обращение будет производиться к ячейкам того вида, который имеет более высокий приоритет.

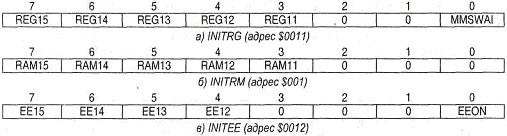

Размещение отдельных видов памяти в адресном пространстве определяется содержимым регистров конфигурации памяти INITRG, INITRM, INITEE (рис. 2.6).

После запуска микроконтроллера реализуется начальное размещение, показанное на рис. 2.5. Затем можно переместить блок периферийных регистров и ОЗУ данных в начало любой страницы памяти емкостью 2 Кбайт, а ЭСППЗУ в начало любой страницы емкостью 4 Кбайт. Старшие разряды базового адреса страниц, на которых располагаются блок регистров, ОЗУ данных и ЭСППЗУ, задаются содержимым битов REG15-11 в регистре INITRG (для блока регистров), RAM15-11 в регистре INITRM (для ОЗУ данных), ЕЕ15-12 в регистре INITEE (для ЭСППЗУ).

Рис. 2.6. Формат содержимого регистров INITRG, INITRM, INITEE, задающих конфигурацию памяти

В дальнейшем при описании регистров и разделов памяти будут указываться их адреса, устанавливаемые после запуска микроконтроллера. В процессе его работы эти адреса могут сдвигаться в соответствии с изменением содержимого соответствующих регистров INITRG, INITRM, INITEE.

В регистрах INITRG, INITEE содержатся также следующие биты:

MMSWAI - сохраняет при значении MMSWAI=0 заданное размещение разделов памяти при переходе в режим ожидания;

EEON - разрешает при значении EEON=1 обращение к ячейкам ЭСППЗУ, размещенным на соответствующей странице памяти, при EEON=0 обращение производится к другим видам памяти, имеющим аналогичный адрес.

После запуска микроконтроллера в регистры INITRG, INITRM, INITEE разрешается только однократная запись, устанавливающая необходимые значения адресных битов REG15-11, RAM15-11, ЕЕ15-12. Последующие изменения этих битов можно осуществить только после повторного запуска. Биты MMSWAI, EEON допускают многократную запись и считывание.

Регистр конфигурации MISC (адрес $0013) в большинстве моделей выполняет следующие функции:

разрешает обращение к внутренней Flash-памяти и определяет ее размещение в адресном пространстве;

увеличивает длительность цикла обращения к внешней памяти, если она имеет недостаточно высокое быстродействие;

задает специальные условия обращения к разделу памяти емкостью 512 Кбайт, который размещается в адресном пространстве непосредственно после блока периферийных регистров.

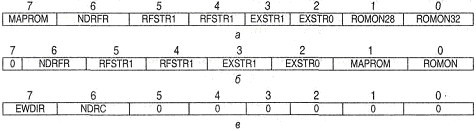

Бит ROMON в регистре MISC (рис. 2.7, а, б) разрешает обращение к Flash-памяти, если установлено значение ROMON=1. Если ROMON=0, то эта память исключается из адресного пространства и запись или чтение ее содержимого запрещены.

Рис. 2.7. Формат содержимого регистра конфигурации MISC (адрес $0013) для микроконтроллеров 68HC912D60 (а), 68НС912В32, ВС32 (б). 68НС812А4 (в)

В модели 68HC912D60 Flash-память состоит из двух сегментов емкостью 28 и 32 Кбайт. Обращение к этим сегментам разрешается отдельными битами ROMON28 и ROMO32R. Бит MAPROM определяет размещение Flash-памяти в адресном пространстве. В моделях 68НС912В32, ВС32 Flash-память размещается в диапазоне адресов $0000-$7FFF при значении MAPROM=0 и в диапазоне $8000-$FFFF при MAPROM=1. В модели 68HC912D60 при MAPROM=0 сегмент емкостью 28 Кбайт имеет адреса $1000-$7FFF, сегмент 32 Кбайт - адреса $8000-$FFFF; при MAPROM=1 сегмент 28 Кбайт имеет адреса $9000-$FFFF, сегмент 32 Кбайт - адреса $0000-$7FFF.

Биты EXSTR1-0 определяют количество дополнительных тактов, вводимых в цикле обращения к внешней памяти в расширенном режиме. Обычно цикл обращения к внешней памяти занимает один такт Tt (см. 2.1.5). Если внешняя память имеет большее время выборки, то можно увеличить цикл обращения на 1, 2 или 3 периода Tt в соответствии с содержимым 2-битового поля EXSTR1-0 в регистре MISC. Таким образом обеспечивается возможность использования медленной памяти.

В большинстве моделей семейства 68НС12/912 предусмотрена возможность специального режима обращения к 512 адресам внешней памяти, которые размешены сразу после блока регистров периферийных устройств. Обычно эти адреса используются для обращения к регистрам различных внешних устройств, подключенных к микроконтроллеру. Если микроконтроллер работает в расширенном режиме с 16-разрядной системной шиной, то можно обеспечить обращение к устройствам, имеющим данные адреса, по 8-разрядной шине. Для этого необходимо установить в регистре MISC значение бита NDRRF=1. При значении NDRF=0 для обращения к этим устройствам используется 16-разрядная шина. Можно ввести дополнительные такты в цикл обращения по данным адресам. Количество вводимых тактов (0, 1, 2 или 3) задается значении битов в поле RFSTR1-0 регистра MISC.

В микроконтроллере 68НС812А4 регистр MISC содержит бит EWDIR, служащий для организации обращения к расширенному адресному пространству до 4 Мбайт, и бит NDRC, используемый при формировании сигналов разрешения выборки CS (Chip Select).

После запуска микроконтроллера биты регистра MISC принимают значение 0, кроме битов ROMON или ROMON28, ROMON32, которые в расширенном режиме устанавливаются в 0, а в автономном режиме в 1. При дальнейшей работе допускается однократная запись в этот регистр, чтобы задать необходимые условия обращения к Flash-памяти и внешней памяти.