- •Теория микропроцессорных систем микроконтроллеры

- •Структура и функциональные возможности мк51

- •Электрический интерфейс мк51

- •Резидентная память данных

- •Работа блока управления и синхронизации

- •Элементы данных в мк51

- •Характеристика функциональных групп команд

- •2.5. Система команд семейства mcs-51.

- •2.5.1. Команды пересылки данных.

- •Команда обработки данных.

- •Команды передачи управления.

- •Характеристика периферийных блоков в составе мк51

- •Управление таймерами-счетчиками (т/с)

- •Описание вариантов конфигурации таймеров-счетчиков

- •Особенности реализации временных интервалов

- •Структура последовательного порта и принципы управления

- •Описание режимов работы уапп

- •Назначение и принципы функционирования системы прерываний

- •Управление приоритетами запросов прерываний

- •Работа системы обслуживания прерываний

- •Заполнение начальной области памяти программ

- •Шестнадцатиразрядные микроконтроллеры Motorola

- •Современные встраиваемые микроконтроллеры, выпускаемые производственной фирмой Freescale Semiconductor

- •Номенклатура и функциональный состав микроконтроллеров cемейства 68hcs12

- •2.1. Микроконтроллеры семейства 68нс12/912

- •2.1.3. Начальный запуск и обработка прерываний

- •2.1.4. Режимы работы и конфигурация микроконтроллеров

- •2.1.5. Функционирование и программирование Flash-памяти и эсппзу

- •2.1.6. Блок контроля функционирования и генератор тактовых импульсов

- •2.1.7. Параллельный ввод-вывод данных и подключение внешней памяти

- •2.1.8. Последовательные порты sci и spi

- •2.1.9. Таймерные модули и широтно-импульсные модуляторы

- •2.1.10. Модуль аналого-цифрового преобразователя atd

- •2.1.11. Модуль последовательного интерфейса msCan

- •2.1.12. Режим отладки bdm и установка контрольных точек

2.1.3. Начальный запуск и обработка прерываний

Запуск (процедура Reset) для микроконтроллеров семейства 68НС12/912 производится так же, как для семейства 68НС11/711 (см. 1.3.3).

Начальный запуск осуществляется при включении напряжения питания Vп или поступлении внешнего сигнала RESET# = 0. При этом в регистре CCR управляющие биты S, X, I устанавливаются в 1, а в программный счетчик PC загружается вектор запуска из ячеек памяти с адресами $FFFE-FF (табл. 2.14). Для надежного запуска с помощью сигнала RESET# рекомендуется поддерживать на нем уровень 0 в течение не менее 32 периодов тактовых импульсов Tt.

Процедура запуска выполняется также при поступлении сигналов от монитора тактовых импульсов и сторожевого таймера, входящих в состав блока контроля функционирования (см. 2.1.6). В этих случаях в PC загружаются специальные векторы запуска, имеющие адреса $FFFC-FD и $FFFA-FB (табл. 2.14).

Процессор CPU12 реализует ряд прерываний, для каждого из которых задается 16-разрядный вектор, указывающий адрес входа в соответствующую процедуру обработки. Таблица векторов прерываний занимает старшие 128 байт адресного пространства, имеющие адреса в диапазоне $FFC0-$FFFF (табл. 2.14). Таким образом обеспечивается возможность использования до 64 различных программ обработки прерываний. При переходе к обработке прерываний процессор последовательно загружает в стек содержимое регистров PC, IY, IX, А, В, CCR - всего 9 байт. Возврат из программы обработки прерывания осуществляется командой RTI, которая восстанавливает содержимое этих регистров, последовательно выбирая его из стека (см. табл. 2.11).

Реально в современных моделях микроконтроллеров используются от 23 до 36 векторов, обеспечивающих обслуживание запросов от различных источников. Старшие 6 позиций таблицы (адреса от $FFF4 до $FFFF) отведены под векторы запуска и немаскируемых прерываний, а остальные распределяются между маскируемыми прерываниями.

К немаскируемым относятся прерывание при поступлении неправильного кода команды (данное прерывание вызывается также командой TRAP, см. табл. 2.11), программное прерывание по команде SWI, прерывание по внешнему сигналу XIRQ# = 0. Эти прерывания перечислены в порядке убывания приоритета их обслуживания. Обслуживание запроса прерывания XIRQ# производится в том случае, если в регистре CCR установлено значение бита Х=0.

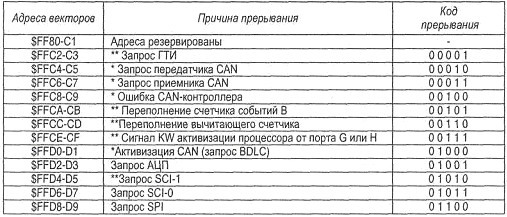

Таблица 2.14. Адреса и приоритеты векторов запуска и прерывания для

микроконтроллеров 68HC912D60, В32, ВС32

К маскируемым относятся прерывания при поступлении сигнала IRQ на вывод РЕ1 порта РЕ или сигналов KW на выводы некоторых параллельных портов (см. 2.1.7), а также прерывания по запросам различных периферийных модулей микроконтроллера: таймерного блока, последовательных портов SCI, SPI, аналого-цифрового преобразователя и др. В зависимости от состава этих модулей различные модели микроконтроллеров используют разное количество векторов прерывания. Разрешение обслуживания для всех маскируемых прерываний осуществляется путем установки в 0 бита I в регистре CCR.

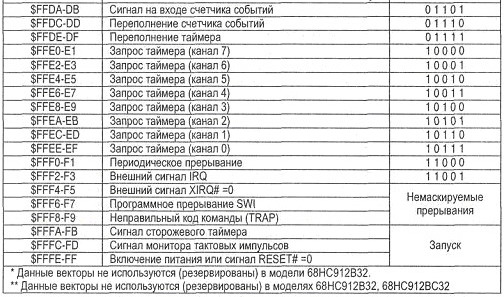

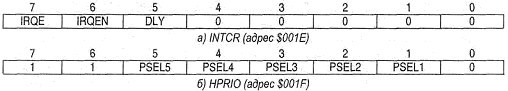

Функционирование вывода РЕ1 определяется значениями битов IRQEN, IRQE в регистре управления INTCR (рис. 2.3, а). При значении бита IRQEN=1 вывод РЕ1 используется в качестве входа запроса прерывания IRQ, при IRQEN=0 этот вывод служит для ввод-вывода данных. Значение бита IRQE определяет вид сигнала IRQ, вызывающего прерывание: при IRQE=0 запросом прерывания является поступление низкого уровня потенциала IRQ=0, при IRQE=1 запрос формируется при поступлении отрицательного перепада потенциала на этот вход. При запуске микроконтроллера эти биты принимают значение IRQEN=1, IRE=0, а затем могут быть установлены в любое необходимое состояние путем записи в регистр INTCR.

Кроме того, регистр INTCR содержит бит DLY, который при значении DLY=1 обеспечивает задержку в 4096 тактов, необходимую для стабилизации работы ГТИ при выходе микроконтроллера из режима останова (см. 2.1.4). При DLY=0 такая задержка не реализуется, поэтому необходимо использовать внешний генератор. При запуске микроконтроллера этот бит принимает значение 1, а затем может быть установлен в 0 только 1 раз (при нормальном режиме работы).

Рис. 2.3. Формат содержимого регистров управления прерываниями INTCR, HPRIO для моделей 68HC912D60, ВС32, B32

В табл. 2.14 приведен состав векторов для наиболее популярных моделей семейства 68НС12. Модель 68HC912D60 помимо типового набора периферийных модулей (таймерного блока, SCI, SPI, АЦП) содержит второй: порт SCI, контроллер CAN-шины, дополнительный счетчик событий В, отдельный вычитающий счетчик. Кроме того, в этой модели имеется программируемый ГТИ со схемой ФАПЧ (PLL), при управлении которым используются прерывания (см. 2.1.6), а выход из режимов ожидания и останова (активизация процессора) может осуществляться с помощью сигналов KW, которые поступают со входов порта G или Н, запрограммированных соответствующим образом (см. 2.1.7). Все эти устройства обслуживаются с помощью отдельных векторов прерывания. Модели 68НС912В32 и 68НС912ВС32 имеют меньший состав периферийных модулей и соответственно другой набор векторов прерывания. Так, в этих моделях есть только один порт SCI, отсутствуют дополнительные счетчики и сигналы активизации KW, используется более простой ГТИ. В модели 68НС912В32 вместо CAN-контроллера имеется BDLC-контроллер, реализующий протокол обмена J1850, который обслуживается с помощью вектора прерывания с адресом $FFD0-D1.

В модели 68HC912DG128, имеющей еще более широкий набор периферийных модулей, дополнительно введены векторы для обслуживания запросов прерываний, которые поступают от второго CAN-контроллера и от интерфейса шины I2C.

Приоритет обслуживания немаскируемых прерываний определяется порядком расположения их векторов в таблице прерываний и значением кода PSEL5-1 в регистре приоритетов HPRIO (рис. 2.3, б). Высший приоритет имеет прерывание, код которого равен коду PSEL5-1. При запуске микроконтроллера в регистре HPRIO устанавливается значение PSEL5-1 = 11001, которое задает максимальный приоритет для сигнала IRQ, а далее приоритет снижается по мере уменьшения адресов векторов (минимальный приоритет имеет прерывание, вектор которого занимает верхнюю позицию в таблице).

Изменить приоритеты немаскируемых прерываний можно путем установки соответствующего значения битов PSEL5-1. При этом прерывание, код которого равен PSEL5-1, получает максимальный приоритет, а приоритеты остальных немаскируемых прерываний циклически изменяются с сохранением их относительных позиций в таблице векторов (минимальный приоритет получает прерывание, предшествующее в таблице прерыванию с максимальным приоритетом). Запись в регистр HPRIO необходимых значений PSEL5-1 разрешается, если в регистре CCR бит I=1 (прерывания запрещены).