- •Лабораторная работа № 13 Стандартные интерфейсы передачи данных компьютерных систем

- •Последовательный порт (com-порт) rs-232c

- •Параллельный порт (Интерфейс ieee1284)

- •Порт ps/2

- •Интерфейс ide (ata)

- •Интерфейс pci

- •Интерфейс pci Express (3gio)

- •Интерфейс HyperTransport

- •Интерфейс scsi

- •Интерфейс agp

- •Порядок работы

- •Лабораторная робота №14 Изучение обмена данных между компьютерами (персональным и карманным palm) и мобильным телефоном через ик – порт.

- •Раздел 1: Синхронизация карманного персонального компьютера (кпк) palm с телефоном Siemens 25.

- •Раздел 2: Синхронизация настольного пк с телефоном Siemens 25

- •Исследование инфракрасного порта (ик)

- •Теоретические сведения

- •Установка ик оборудования

- •Лабораторна робота №17 Использование осциллографа для измерения параметров модулированных сигналов

- •Теоретические сведения

- •Получение модулированных колебаний

- •Амплитудная модуляция

- •Демодуляция сигналов

- •Порядок выполнения работы

- •Требования к содержанию отчета

Интерфейс pci Express (3gio)

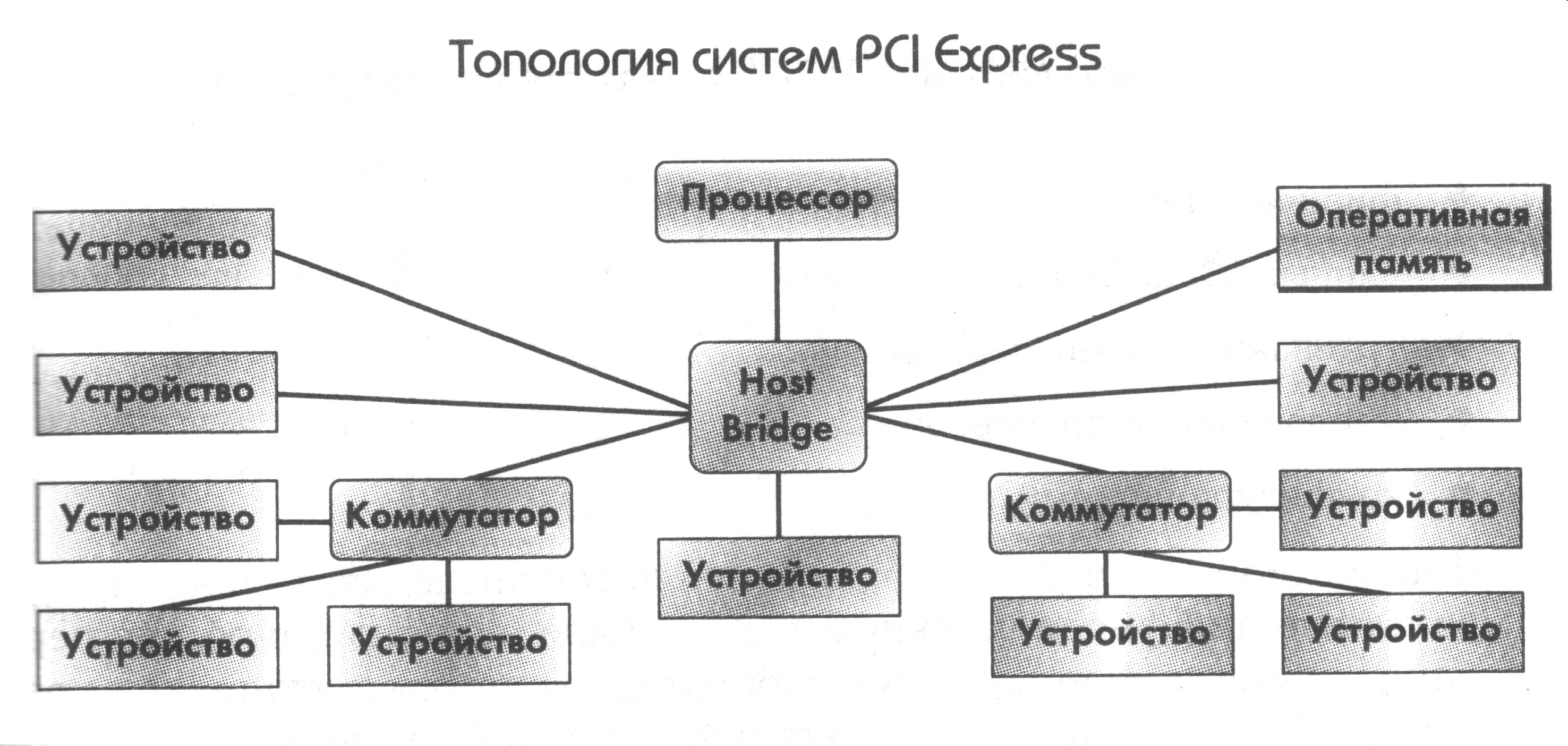

Аббревиатура 3GIO расшифровывается как «3-е поколение шины ввода-вывода»(Third Generation Input/Output Interconnection). По физической сути архитектура шины 3GIO мало чем отличается от HyperTransport, хотя и является синхронной. В ней также используется концепция связи «точка - точка». Полноценным каналом считаются как минимум две низковольтные высокочастотные дифференциальные линии шириной от 1 до 32 бит. Система адресации полностью совместима со спецификацией PC/, что позволяет подключать устройства PCI к новой шине. Точно так же остался практически без изменений механизм автоматического конфигурирования устройств (Plug-and-Play). Данные пересылаются пакетами по 8 или 10 бит (в последнем случае два бита предназначены для поддержки механизма контроля четности и исправления ошибок). Значения снимаются по фронту и спаду сигналов, что обеспечивает удвоение физической тактовой частоты. На аппаратном уровне шина PCI Express управляется контроллером Host Bridge, предназначенным главным образом для взаимодействия с процессором, оперативной памятью и графической подсистемой компьютера. Все остальные устройства могут подключаться через специальный коммутатор, который позволяет им взаимодействовать между собой без обращения к Host Bridge и, тем более, процессору. Конечно, при обращении к памяти или графической подсистеме линия связи 3GIO проходит через коммутатор к Host Bridge. Корпорация Intel взяла на себя роль неформального лидера в рабочей группе по созданию архитектуры интерфейса ввода-вывода третьего поколения. В рабочую группу вошли не менее известные фирмы Microsoft, IBM, Dell, Compaq и пр. Благодаря влиянию этих гигантов в организации PCI-SIG (Special Group for Interesting PCI Interface) в 2001 году принято предварительное решение о внедрении архитектуры 3GIO в массовые компьютерные системы для замены шины PCI и других внутренних интерфейсов. Тем самым Intel пытается составить конкуренцию AMD, у которой еще в 2001 году появились первые компьютерные системы с поддержкой интерфейса HyperTransport.

Физической основой PCI Express являются последовательные низковольтные дифференциальные линии связи, по одной паре для передачи и приема данных. Масштабируемость шины достигается кратным (1, 2, 4, 8, 16, 32) увеличением числа линий. Между участниками обмена данными по шине PCI Express устанавливается выделенный канал связи, ширина которого и тактовая частота обговариваются устройствами в процессе инициализации канала. Здесь же происходит представление данных в формате 8 или 10 бит. При необходимости 2 бита используются для контроля за целостностью данных. Тем самым реализуется концепция обмена данными «точка - точка». Теоретически полоса пропускания самого узкого канала достигает 2,5 Гбит/с в каждом направлении. С внедрением в микросхемы технологии медных соединений ожидается увеличение пиковой пропускной способности до 10 Гбит/с. На уровне драйверов и приложений архитектура PCI Express полностью совместима с интерфейсом PCI и потому поддерживается любой операционной системой, поддерживающей PCI. Тем самым обеспечена поддержка спецификации Plug-and-Play без какой-либо доработки общих программных компонентов. Помимо оконечных устройств архитектурой интерфейса предусмотрено наличие контроллеров (Host), мостов (Bridge) и коммутаторов (Switch), что позволяет организовать сложную топологию каналов и обеспечить совместимость с другими интерфейсами.

-

Число линий PCI Express

Пропускная способность в одном направлении

Суммарная пропускная способность

1

256 Мбайт/с

512 Мбайт/с

2

512 Мбайт/с

1 Гбайт/с

4

1 Гбайт/с

2 Гбайт/с

8

2 Гбайт/с

4 Гбайт/с

16

4 Гбайт/с

8 Гбайт/с