- •Федеральное агентство по образованию

- •1. Основы электрических измерений

- •1.1. Основные понятия и определения

- •1.2. Точностные характеристики средств измерений

- •1.3. Анализ статических погрешностей электронных схем

- •2. Простейшие электронные цепи и методы их анализа

- •2.1. Основные понятия и определения

- •2.2. Применение операторного метода к расчету электрических цепей

- •2.2.1. Прямое преобразование Лапласа

- •2.2.2. Обратное преобразование Лапласа

- •3. Типовые структуры электронных устройств и их свойства

- •3.1. Последовательная структура и ее свойства

- •3.2. Параллельная структура и ее свойства

- •3.3. Встречно-параллельное соединение

- •3.4. Задачи

- •4. Пассивные полупроводниковые компоненты электронных цепей

- •4.1. Полупроводниковые диоды и стабилитроны

- •4.2. Примеры применения полупроводниковых диодов

- •4.3. Светодиоды

- •4.4. Фотодиоды

- •5. Активные полупроводниковые компоненты электронных цепей

- •5.1. Биполярные транзисторы и их применение

- •5.1.1. Структура и принцип действия биполярных транзисторов

- •5.1.2. Характеристики и параметры биполярных транзисторов

- •5.1.3. Обеспечение усилительного режима бт в схемах

- •В результате получаем

- •5.1.4. Малосигнальные эквивалентные схемы и усилительные параметры бт

- •5.1.5. Амплитудно-частотные характеристики бт

- •5.1.6. Элементы транзисторной схемотехники

- •5.2. Полевые транзисторы и их применение

- •5.2.1. Классификация и общие особенности полевых транзисторов

- •5.2.2. Статические характеристики и дифференциальные параметры

- •5.2.3. Способы задания смещения в усилительных каскадах на пт

- •5.2.4. Малосигнальные эквивалентные схемы и усилительные параметры пт

- •5.2.5. Температурная стабильность параметров пт

- •5.2.6. Передаточная функция и динамические свойства пт Инерционные свойства пт описываются передаточной функцией вида

- •5.3. Задачи

- •6. Интегральные микросхемы и их классификация

- •7. Аналоговые интегральные микросхемы и их применение

- •7.1. Операционные усилители и их применение

- •7.1.1. Понятие идеального операционного усилителя

- •7.1.2. Принципы и примеры расчета схем с операционными усилителями

- •7.1.3. Динамические свойства устройств на операционных усилителях

- •7.1.4. Точностные характеристики устройств на операционных усилителях

- •7.1.5. Применение операционных усилителей

- •7.1.6. Задачи

- •7.2. Компараторы

- •7.3. Аналоговые ключи и коммутаторы

- •7.4. Устройства выборки-хранения

- •7.5. Интегральный таймер

- •7.5.1. Задачи

- •7.7. Справочные данные на оу

- •8. Цифро-аналоговые и аналого-цифровые преобразователи

- •8.1. Цифро-аналоговые преобразователи (цап)

- •8.2. Аналого-цифровые преобразователи (ацп)

- •9. Цифровые интегральные микросхемы и их применение

- •9.1. Элементы алгебры логики

- •9.2. Основные типы цифровых имс

- •9.3. Параметры цимс

- •9.4. Комбинационные логические цепи

- •9.4.1. Основные разновидности комбинационных логических цепей

- •9.4.2. Синтез комбинационных логических цепей

- •9.5. Последовательностные логические цепи

- •9.5.1. Классификация последовательностных логических цепей

- •9.5.2. Триггеры

- •9.5.3. Регистры

- •9.5.4. Счетчики импульсов

- •9.6. Применение цифровых имс в импульсных цепях

- •9.7. Задачи

- •10. Микросхемы полупроводниковых запоминающих устройств

- •10.1. Классификация полупроводниковых запоминающих устройств

- •10.2. Построение модулей памяти микропроцессорных систем

- •11. Элементы микропроцессорной техники

- •11.1. Общие сведения о микроконтроллерах семейства piCmicro

- •1. Ядро микроконтроллера

- •2. Периферийные модули

- •3. Специальные особенности микроконтроллеров

- •Ядро микроконтроллера

- •Порты ввода-вывода

- •Периферийные модули

- •11.2. Примеры применения микроконтроллеров piCmicro

- •11.2.1. Устройство управления четырьмя светодиодами

- •Incf portb, f ; включить крайний справа светодиод

- •11.2.2. Управление жки с помощью последовательного адаптера

- •11.2.3. Аналого-цифровое преобразование

- •11.3. Общие сведения о микроконтроллерах семейства avr

- •Режимы адресации программ и данных.

- •11.4. Примеры применения микроконтроллеров avr

- •11.4.1. Ик дальномер

- •Библиографический список

- •Оглавление

9.7. Задачи

Задача 1. Минимизировать логические функции, приведенные в табл. 9.5.

Таблица 9.5

|

№ пп |

Исходная логическая функция |

|

1 |

|

|

2 |

|

|

3 |

|

|

4 |

|

|

5 |

|

|

6 |

|

|

7 |

|

|

8 |

|

|

9 |

|

|

10 |

|

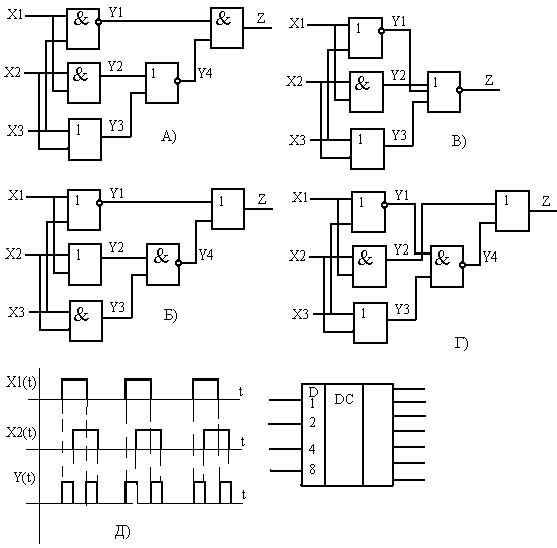

Задача 2. Минимизировать КЛЦ, представленные на рис. 9.14а-г.

Задача 3. Синтезировать КЛЦ, входные (X1(t), X2(t)) и выходной (Y(t)) сигналы которой изменяются во времени так, как показано на рис. 9.14д.

Задача 4. Синтезировать дешифратор для управления цифровым семисегментным светодиодным индикатором, если входной код 8-4-2-1, а сегменты управляются сигналом логической 1. Синтез проводить для каждого сегмента (A, B, C, D, E, F, G) отдельно.

Задача 5. Синтезировать следующие типы преобразователей кодов:

1) четырехразрядного двоичного кода в четырехразрядный код Грея;

2) четырехразрядного двоичного кода в пятиразрядный код Джонсона;

3) кода 8-4-2-1 в код 5-3-1-1.

Задача 6. Синтезировать дешифратор для управления цифровым газоразрядным индикатором, если входной код 8-4-2-1, а катоды управляются сигналом логического 0. Синтез проводить для каждого катода (0, 1, 2, 3, 4, 5, 6, 7, 8, 9) отдельно.

Задача 7. Синтезировать синхронный двоичный счетчик с коэффициентом пересчета 9 на JK-триггерах, тактируемых перепадом из 1 в 0. Провести полную проверку.

Задача 8. Синтезировать асинхронный двоичный счетчик с коэффициентом пересчета 12 на JK-триггерах, тактируемых перепадом из 1 в 0. Провести полную проверку.

Задача 9. Синтезировать синхронный десятичный счетчик в коде 8-4-2-1 на JK-триггерах, тактируемых перепадом из 1 в 0. Провести полную проверку.

Задача 10. Синтезировать синхронный десятичный счетчик в коде 2-4-2-1 на JK-триггерах, тактируемых перепадом из 1 в 0. Провести полную проверку.

Задача 11. Синтезировать синхронный десятичный счетчик в коде 5-3-1-1 на JK-триггерах, тактируемых перепадом из 1 в 0. Провести полную проверку.

Задача 12. Синтезировать асинхронный десятичный счетчик в коде 8-4-2-1 на D-триггерах, тактируемых перепадом из 0 в 1. Провести полную проверку.

Задача 13. Синтезировать асинхронный десятичный счетчик в коде 2-4-2-1 на JK-триггерах, тактируемых перепадом из 1 в 0. Провести полную проверку.

Задача 14. Синтезировать асинхронный десятичный счетчик в коде 5-3-1-1 на JK-триггерах, тактируемых перепадом из 1 в 0. Провести полную проверку.

Задача 15. Синтезировать синхронный счетчик на 7 в коде 4-2-1 на D-триггерах, тактируемых перепадом из 0 в 1.

Задача 16. Синтезировать асинхронный счетчик на 8 в коде 4-2-1 на JK-триггерах, тактируемых перепадом из 1 в 0.

Р ис.

9.14

ис.

9.14

10. Микросхемы полупроводниковых запоминающих устройств

10.1. Классификация полупроводниковых запоминающих устройств

Н а

рис. 10.1 представлена классификация

микросхем полупроводниковых запоминающих

устройств (ЗУ).

а

рис. 10.1 представлена классификация

микросхем полупроводниковых запоминающих

устройств (ЗУ).

Рис. 10.1

По способу обращения к элементам памяти различают адресные и ассоциативные ЗУ. В адресных ЗУ обращение к элементам памяти производится по их физическим координатам, задаваемым двоичным кодом – адресом. Они бывают с произвольным обращением (выборкой), т.е. допускают любой порядок следования адресов, и с последовательным обращением, где выборка элементов памяти возможна только в определенном порядке возрастания или убывания адресов. В настоящее время ЗУ с произвольной выборкой являются наиболее распространеными типами памяти.

По функциональному назначению ЗУ можно разделить на энергонезависимые ЗУ ("только для чтения") – постоянные запоминающие устройства ПЗУ или ROM (read only memory) и энергозависимые оперативные ЗУ с произвольной выборкой для чтения и записи ОЗУ или RAM (random access memory).

ПЗУ применяются для хранения управляющих программ, различных таблиц (в том числе знакогенераторов) и т.д. Существует несколько их разновидностей, которые отличаются принципом занесения информации, технологией изготовления и др.

Масочные ПЗУ выпускаются по различным технологиям (ТТЛ, КМОП); информация в них заносится на заводе-изготовителе, обычно на финишном участке технологического процесса. Каждая "прошивка", т.е. заносимый в ПЗУ массив информации, требует соответствующей дорогостоящей подготовки производства – индивидуальной маски (фотошаблона). Поэтому данный тип ПЗУ рентабельно применять в уже отлаженных изделиях, выпускаемых большими партиями. Примерами являются ПЗУ знакогенератора типа К555РЕ4 или ПЗУ КР568РЕ3 емкостью 16 кБайт, в которое занесены редактор текстов, ассемблер и монитор микропроцессорной системы на основе процессора КР580ВМ80.

Программируемые ПЗУ (ППЗУ) с плавкими перемычками поступают к потребителю в первоначальном незапрограммированном состоянии. В режиме программирования можно записать в ППЗУ информацию путем пережигания перемычек электрическим током по специальной программе. Выпускается широкая гамма подобных микросхем серии КР556 на основе ТТЛШ.

ППЗУ с ультрафиолетовым стиранием информации широко используется в микропроцессорных системах. В этих БИС каждый бит хранимой информации отображается состоянием соответствующего МОП-транзистора с плавающим затвором. Затворы транзисторов при программировании заряжаются лавинной инжекцией, т.е. обратимым пробоем окружающего затвор диэлектрика под действием электрического импульса напряжением 18–26 В. Заряд в таком своеобразном конденсаторе может сохраняться очень долго. Так, например, в ППЗУ серии К573 РФ гарантируется сохранение информации не менее 15–25 тыс. часов во включенном и до 100 тыс. часов (более 10 лет) – в выключенном состоянии. Программирование ПЗУ производят с помощью специальных устройств – программаторов. Незапрограммированная микросхема ПЗУ с ультрафиолетовым стиранием имеет на выходах по всем адресам уровень логической 1. Для записи в требуемые разряды логического 0 при установленном адресе на соответствующие выводы данных подается уровень 0, а на остальные – 1. Можно производить коррекцию записи, изменяя состояние 1 в любых разрядах на 0, но не наоборот. Для полного программирования БИС К573РФ2 емкостью 2 кБайт требуется около 100 с. Для стирания информации в течение 30–60 мин облучают кристалл микросхемы сквозь специальное окно ультрафиолетовым излучением люминесцентной лампы, которое увеличивает ток утечки в изолирующем слое, приводя к рассасыванию заряда на всех элементах памяти. Число циклов перезаписи обычно лежит в пределах от 10 до 100.

ППЗУ с электрическим стиранием позволяет производить как запись, так и стирание информации с помощью электрических сигналов. Для этого, в частности, применяются структуры с лавинной инжекцией заряда, аналогичные тем, на которых строятся ППЗУ с ультрафиолетовым стиранием, но с дополнительными управляющими затворами, размещаемыми над плавающими. Подача напряжения на управляющий затвор приводит к рассасыванию заряда плавающего затвора за счет туннелирования носителей заряда сквозь изолирующий слой. По этой технологии изготавливаются микросхемы К573РР, КМ1609. Достоинством ППЗУ с электрическим стиранием является не только удобство и высокая скорость перезаписи, но и значительное допустимое число циклов перезаписи – до 10000.

ОЗУ в зависимости от структуры элементов памяти подразделяются на статические (СОЗУ) и динамические (ДОЗУ).

Элементы памяти в СОЗУ строятся на основе статических триггерных цепей (регистров памяти). Хранение информации в триггере требует определенной мощности от источника питания, поэтому такое ЗУ является энергозависимым. Типовая реализация триггерного элемента памяти составляет шеститранзисторную схему. Поэтому СОЗУ проигрывают в 4–8 раз по информационной емкости на кристалле динамическим ОЗУ, в которых запоминающий элемент выполняется однотранзисторным.

Информация в ДОЗУ хранится в виде заряда на конденсаторе, обкладками которого являются области стока МОП-транзистора и подложки. Запись и считывание информации производятся путем открывания транзистора по затвору и подключения тем самым запоминающей емкости к схеме усилителя-регенератора.

Последний является статическим триггерным элементом, который в зависимости от предварительной подготовки или принимает информацию из емкостной ячейки, устанавливаясь при этом в состояние 0 или 1, или, наоборот, в режиме записи соответствующим образом заряжает ячейку, будучи предварительно установленным в 0 или 1.

В режиме чтения триггер усилителя вначале специальным управляющим сигналом устанавливается в неустойчивое состояние, из которого при подключении к нему запоминающей емкости он переключается в 0 или 1. При этом вначале он потребляет часть заряда, а затем при установке в устойчивое состояние возвращает его ячейке, осуществляя, таким образом, регенерацию ее состояния.

В режиме хранения необходимо периодически производить регенерацию для компенсации естественных утечек заряда. Максимальный период цикла регенерации для каждой ячейки составляет 1–2 мс.

Основными параметрами ЗУ являются: 1) информационная емкость; 2) организация ЗУ; 3) время записи; 4) время считывания; 5) время хранения. Естественно, что для ПЗУ третий и пятый параметры лишены практического смысла (запись производится один раз на заводе и время хранения теоретически бесконечно) и тогда остаются первый, второй и четвертый параметры. Для статических ОЗУ время хранения равно времени поддержания питания на элементах ЗУ. Таким образом, только для ДОЗУ имеют значения все указанные параметры.

Информационная емкость Си определяется соотношением Си = 2M N, где M – число разрядов адреса микросхемы ЗУ, N – число разрядов выходного кода ЗУ. Правая часть этой формулы определяет организацию ЗУ. Например, микросхема ДОЗУ типа К565РУ5Б имеет организацию 64К1 = 216 адресов одноразрядных ячеек, что соответствует информационной емкости 64 кбит.